一种闪存器件的制备方法与流程

本发明涉及半导体制造,尤其涉及一种闪存器件的制备方法。

背景技术:

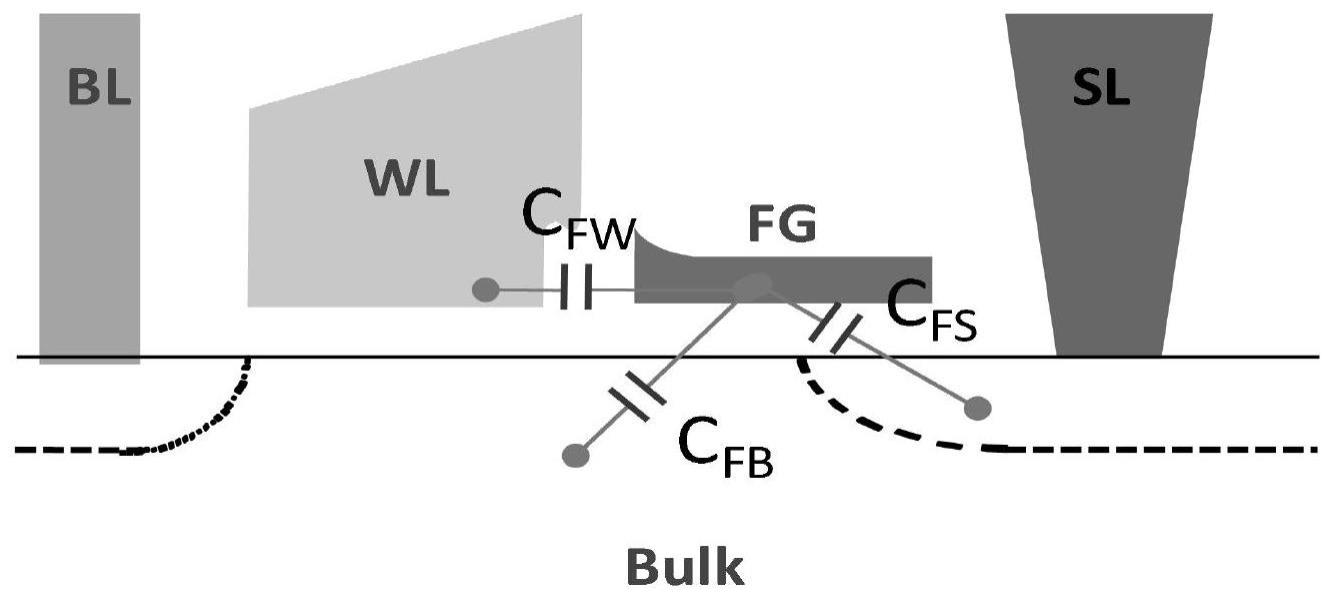

1、快闪存储器,简称为闪存,分为两种类型:叠栅(stack gate)器件和分栅(splitgate)器件,其中,分栅器件是在浮栅的一侧形成作为擦除栅极的字线,字线作为控制栅,在擦除性能上,分栅器件有效地避免了叠栅器件的过擦除效应,电路设计相对简单。因而被广泛应用在各类电子产品中。

2、在分栅式闪存存储器中,浮栅尖端的高度与尖锐度会影响浮栅在编程、擦除时候耦合的电压,从而影响闪存在编程、擦除时的性能。而过高的浮栅尖端高度会导致源线耦合效率降低,从而导致存储单元编程失效,而浮栅尖端高度一般取决于浮栅淀积厚度,传统做法通过炉管淀积不同浮栅厚度来控制浮栅尖端高度,但由于炉管特性,这很难控制很精确,因此,经常会出现编程失效的问题。

技术实现思路

1、本发明的目的在于提供一种闪存器件的制备方法,以解决现有技术中由于炉管自身无法精准控制的特性,导致利用炉管形成的闪存器件的浮栅尖端的高度过高,进而引起闪存器件的编程失效的技术问题。

2、为了达到上述目的,本发明首先提供了一种闪存器件的制备方法,至少可以包括如下步骤:

3、提供一半导体衬底;

4、在所述半导体衬底的表面上自下而上依次形成浮栅氧化物材料层和浮栅材料层;

5、测量所述浮栅材料层的厚度,并基于不同产品的膜层厚度设计要求刻蚀所述浮栅材料层,以动态调整刻蚀后形成的浮栅尖端的高度。

6、进一步的,刻蚀所述浮栅材料层的工艺具体可以包括:化学干法刻蚀工艺cde、湿法刻蚀工艺以及混合刻蚀工艺中的至少一种。

7、进一步的,形成所述浮栅材料层的工艺具体可以为炉管工艺。

8、进一步的,在炉管中形成满足不同产品设计要求的浮栅材料层之后,本发明所提供的闪存器件的所述制备方法还可以包括:去除刻蚀所述浮栅材料层后所形成的残留污染物的步骤。

9、进一步的,去除所述残留污染物的工艺具体可以包括湿法清洗工艺。

10、进一步的,所述闪存器件具体可以是但不限于共享源线源线的双存储位结构。

11、进一步的,所述浮栅氧化物材料层的材料具体可以包括二氧化硅,所述浮栅材料层的材料具体可以包括多晶硅。

12、进一步的,在刻蚀所述浮栅材料层的步骤之后,本发明所提供的闪存器件的所述制备方法还可以包括:对包含所述浮栅的半导体衬底进行后续工艺,以形成所述闪存器件的包含源区、漏区、字线以及源线在内的电学结构。

13、进一步的,在刻蚀所述浮栅材料层的步骤之后,本发明所提供的闪存器件的所述制备方法还可以包括:在所述浮栅材料层的表面上形成硬掩膜层,并以所述硬掩膜层为浅沟绝缘研磨的阻挡的掩膜层,进行后续有源区结构的形成。

14、进一步的,所述硬掩膜层的材料具体可以包括氮化硅。

15、与现有技术相比,本发明的技术方案至少具有以下有益效果之一:

16、本发明提供了一种闪存器件的制备方法,具体包括提供一半导体衬底;在所述半导体衬底的表面上自下而上依次形成浮栅氧化物材料层和浮栅材料层;测量所述浮栅材料层的厚度,并基于不同产品的膜层厚度设计要求刻蚀所述浮栅材料层,以动态调整刻蚀后形成的浮栅尖端的高度。

17、由于本发明提供的制备方法在利用炉管工艺形成闪存器件的浮栅材料层之后,增加了一步根据不同产品的膜层厚度设计要求刻蚀所述浮栅材料层,以动态调整刻蚀后形成的浮栅尖端的高度的步骤,进而实现了浮栅多晶硅厚度的均匀性控制,避免了炉管不同位置带来浮栅多晶硅厚度的偏差,即有效的控制了最终形成的浮栅尖端的高度。

18、进一步的,由于本发明所提供的制备方法增加了动态浮栅多晶硅厚度的调节步骤,因此其还可以实现不同浮栅厚度要求产品共用相同多晶硅程式,以提升浮栅多晶硅炉管生产效率的目的。

技术特征:

1.一种闪存器件的制备方法,其特征在于,包括如下步骤:

2.如权利要求1所述的闪存器件的制备方法,其特征在于,刻蚀所述浮栅材料层的工艺包括化学干法刻蚀工艺cde、湿法刻蚀工艺以及混合刻蚀工艺中的至少一种。

3.如权利要求1所述的闪存器件的制备方法,其特征在于,形成所述浮栅材料层的工艺为炉管工艺。

4.如权利要求3所述的闪存器件的制备方法,其特征在于,在炉管中形成满足不同产品设计要求的浮栅材料层之后,所述制备方法还包括去除刻蚀所述浮栅材料层后所形成的残留污染物的步骤。

5.如权利要求4所述的闪存器件的制备方法,其特征在于,去除所述残留污染物的工艺包括湿法清洗工艺。

6.如权利要求1所述的闪存器件的制备方法,其特征在于,所述闪存器件包括共享源线的双存储位结构。

7.如权利要求4所述的闪存器件的制备方法,其特征在于,所述浮栅氧化物材料层的材料包括二氧化硅,所述浮栅材料层的材料包括多晶硅。

8.如权利要求1所述的闪存器件的制备方法,其特征在于,在刻蚀所述浮栅材料层的步骤之后,所述制备方法还包括对包含所述浮栅尖端的半导体衬底进行后续工艺,以形成所述闪存器件的包含源区、漏区、字线以及源线在内的电学结构。

9.如权利要求2所述的闪存器件的制备方法,其特征在于,在刻蚀所述浮栅材料层的步骤之后,所述制备方法还包括在所述浮栅材料层的表面上形成硬掩膜层,并以所述硬掩膜层为浅沟绝缘研磨的阻挡的掩膜层,进行后续有源区结构的形成。

10.如权利要求9所述的闪存器件的制备方法,其特征在于,所述硬掩膜层的材料包括氮化硅。

技术总结

本发明提供了一种闪存器件的制备方法,应用于半导体制造领域中。由于本发明提供的制备方法在利用炉管工艺形成闪存器件的浮栅材料层之后,增加了一步根据不同产品的膜层厚度设计要求刻蚀所述浮栅材料层,以动态调整刻蚀后形成的浮栅尖端的高度的步骤,进而实现了浮栅多晶硅厚度的均匀性控制,避免了炉管不同位置带来浮栅多晶硅厚度的偏差,即有效的控制了最终形成的浮栅尖端的高度。进一步的,由于本发明所提供的制备方法增加了动态浮栅多晶硅厚度的调节步骤,因此其还可以实现不同浮栅厚度要求产品共用相同多晶硅程式,以提升浮栅多晶硅炉管生产效率的目的。

技术研发人员:曹子贵

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!