分离栅沟槽MOSFET器件的形成方法与流程

本发明涉及半导体,尤其是涉及一种分离栅沟槽mosfet器件的形成方法。

背景技术:

1、分离栅沟槽(sgt,split gate trench)mosfet器件具有电荷耦合效应,在采用同样掺杂浓度的外延规格情况下,器件可以获得更高的击穿电压。

2、分离栅沟槽mosfet器件结构的栅结构一般形成在深沟槽中,形成的步骤包括首先形成深沟槽,再在深沟槽的侧壁形成一层氧化物,氧化物根据深沟槽的形状中间也会形成一个沟槽,接着在沟槽内沉积多晶硅,再刻蚀部分深度的氧化物,剩余的氧化物,作为场氧层。

3、然而,形成分离栅沟槽mosfet器件结构是在晶圆上形成的,可以同时形成多个分离栅沟槽mosfet器件结构,因此在刻蚀形成深沟槽时,会在晶圆表面包括晶圆中心和晶边上形成沟槽,由于刻蚀机台的等离子差异,晶边形成的是浅沟槽,晶圆中心形成的是深沟槽。接着,在深沟槽和浅沟槽内均同时沉积一层氧化层覆盖深沟槽和浅沟槽的侧壁,氧化层均形成沟槽,再在沟槽内形成多晶硅。最后刻蚀深沟槽内部分深度的氧化物露出部分深度的多晶硅。此时,浅沟槽内的氧化物会被刻蚀掉同等深度氧化物,而由于浅沟槽内的氧化物的厚度较低,所以被刻蚀掉的氧化物相对来说是较深的,所以导致浅沟槽内露出的多晶硅容易剥落。如果剥落的多晶硅掉落到晶边外的其他晶圆区域的分离栅沟槽mosfet器件结构上,可能导致分离栅沟槽mosfet器件结构的源极和栅极连通而短路,造成了分离栅沟槽mosfet器件结构的不良。

技术实现思路

1、本发明的目的在于提供一种分离栅沟槽mosfet器件的形成方法,可以减少晶边区域的多晶硅剥落的情况,从而减少分离栅沟槽mosfet器件结构的源极和栅极连通的情况,提高分离栅沟槽mosfet器件结构的质量。

2、为了达到上述目的,本发明提供了一种分离栅沟槽mosfet器件的形成方法,包括:

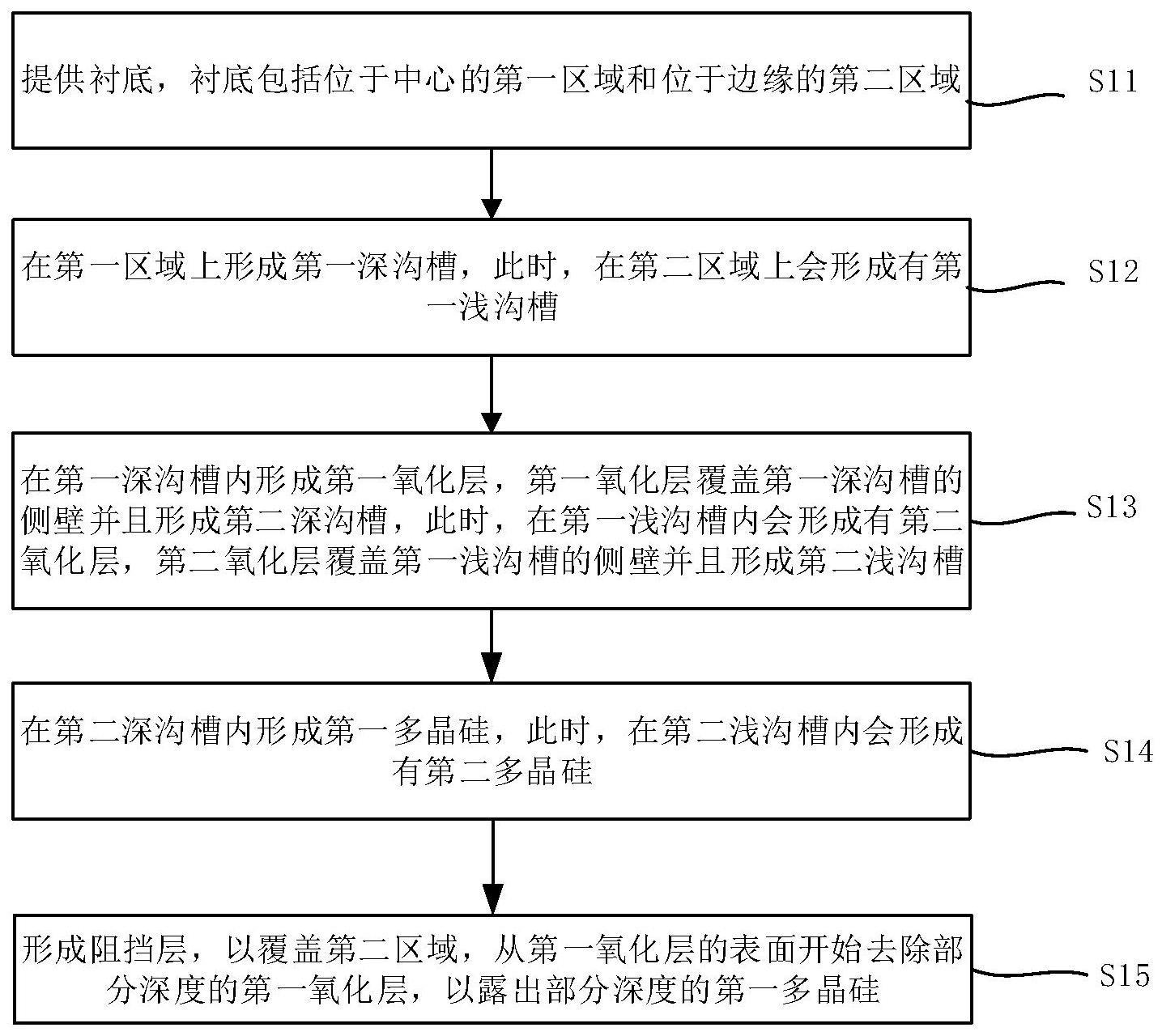

3、提供衬底,所述衬底包括位于中心的第一区域和位于边缘的第二区域;

4、在所述第一区域上形成第一深沟槽,此时,在所述第二区域上会形成有第一浅沟槽;

5、在所述第一深沟槽内形成第一氧化层,所述第一氧化层覆盖所述第一深沟槽的侧壁并且形成第二深沟槽,此时,在所述第一浅沟槽内会形成有第二氧化层,所述第二氧化层覆盖所述第一浅沟槽的侧壁并且形成第二浅沟槽;

6、在所述第二深沟槽内形成第一多晶硅,此时,在所述第二浅沟槽内会形成有第二多晶硅;

7、形成阻挡层,以覆盖所述第二区域,从所述第一氧化层的表面开始去除部分深度的所述第一氧化层,以露出部分深度的所述第一多晶硅。

8、可选的,在所述的分离栅沟槽mosfet器件的形成方法中,所述衬底包括晶圆。

9、可选的,在所述的分离栅沟槽mosfet器件的形成方法中,所述第一深沟槽和第二深沟槽均为多个。

10、可选的,在所述的分离栅沟槽mosfet器件的形成方法中,在所述第一区域上形成第一深沟槽,此时,在所述第二区域上会形成有第一浅沟槽的方法包括:

11、刻蚀所述衬底同时形成第一深沟槽和第一浅沟槽。

12、可选的,在所述的分离栅沟槽mosfet器件的形成方法中,所述深沟槽的深度大于所述第一浅沟槽的深度。

13、可选的,在所述的分离栅沟槽mosfet器件的形成方法中,使用阻挡层覆盖所述第二区域,从所述第一氧化层的表面开始去除0.9μm~1.1μm深度的所述第一氧化层。

14、可选的,在所述的分离栅沟槽mosfet器件的形成方法中,所述阻挡层包括光刻胶。

15、可选的,在所述的分离栅沟槽mosfet器件的形成方法中,所述阻挡层包括负性光刻胶。

16、可选的,在所述的分离栅沟槽mosfet器件的形成方法中,所述阻挡层的厚度为0.5μm~5μm。

17、可选的,在所述的分离栅沟槽mosfet器件的形成方法中,使用阻挡层覆盖所述第二区域,从所述第一氧化层的表面开始去除部分深度的所述第一氧化层,以露出部分深度的所述第一多晶硅之后,还包括:去除所述阻挡层。

18、在本发明提供的分离栅沟槽mosfet器件的形成方法中,包括:提供衬底,衬底包括位于中心的第一区域和位于边缘的第二区域;在第一区域上形成第一深沟槽,此时,在第二区域上会形成有第一浅沟槽;在第一深沟槽内形成第一氧化层,第一氧化层覆盖第一深沟槽的侧壁并且形成第二深沟槽,此时,在第一浅沟槽内会形成有第二氧化层,第二氧化层覆盖第一浅沟槽的侧壁并且形成第二浅沟槽;在第二深沟槽内形成第一多晶硅,此时,在第二浅沟槽内会形成有第二多晶硅;形成阻挡层,以覆盖第二区域,从第一氧化层的表面开始去除部分深度的第一氧化层,以露出部分深度的第一多晶硅。使用阻挡层覆盖第二区域,在刻蚀部分深度的第一氧化层的时候,不会刻蚀到第二氧化层,所以不会导致第二多晶硅露出,减少了晶边区域的多晶硅剥落的情况,从而减少了分离栅沟槽mosfet器件结构的源极和栅极连通的情况,提高了分离栅沟槽mosfet器件结构的质量。

技术特征:

1.一种分离栅沟槽mosfet器件的形成方法,其特征在于,包括:

2.如权利要求1所述的分离栅沟槽mosfet器件的形成方法,其特征在于,所述衬底包括晶圆。

3.如权利要求1所述的分离栅沟槽mosfet器件的形成方法,其特征在于,所述第一深沟槽和第二深沟槽均为多个。

4.如权利要求1所述的分离栅沟槽mosfet器件的形成方法,其特征在于,在所述第一区域上形成第一深沟槽,此时,在所述第二区域上会形成有第一浅沟槽的方法包括:

5.如权利要求1所述的分离栅沟槽mosfet器件的形成方法,其特征在于,所述深沟槽的深度大于所述第一浅沟槽的深度。

6.如权利要求1所述的分离栅沟槽mosfet器件的形成方法,其特征在于,使用阻挡层覆盖所述第二区域,从所述第一氧化层的表面开始去除0.9μm~1.1μm深度的所述第一氧化层。

7.如权利要求1所述的分离栅沟槽mosfet器件的形成方法,其特征在于,所述阻挡层包括光刻胶。

8.如权利要求7所述的分离栅沟槽mosfet器件的形成方法,其特征在于,所述阻挡层包括负性光刻胶。

9.如权利要求1所述的分离栅沟槽mosfet器件的形成方法,其特征在于,所述阻挡层的厚度为0.5μm~5μm。

10.如权利要求1所述的分离栅沟槽mosfet器件的形成方法,其特征在于,使用阻挡层覆盖所述第二区域,从所述第一氧化层的表面开始去除部分深度的所述第一氧化层,以露出部分深度的所述第一多晶硅之后,还包括:去除所述阻挡层。

技术总结

本发明提供了一种分离栅沟槽MOSFET器件的形成方法,包括:提供衬底,衬底包括位于中心的第一区域和位于边缘的第二区域;在第一区域上形成第一深沟槽,第二区域上形成有第一浅沟槽;在第一深沟槽内形成第一氧化层,第一氧化层覆盖第一深沟槽的侧壁并且形成第二深沟槽,第一浅沟槽内形成有第二氧化层,第二氧化层覆盖第一浅沟槽的侧壁并且形成第二浅沟槽;在第二深沟槽内形成第一多晶硅,第二浅沟槽内形成有第二多晶硅;形成阻挡层覆盖第二区域,去除部分深度的第一氧化层。本发明使用阻挡层覆盖第二区域,在刻蚀部分深度的第一氧化层的时候,不会刻蚀到第二氧化层,所以不会导致第二多晶硅露出,减少了晶边区域的多晶硅剥落的情况。

技术研发人员:李秀然,翟盼,王彩虹

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!