半导体封装结构的制作方法

本公开大体上涉及一种半导体封装结构。

背景技术:

1、目前,插入件已广泛地用于衬底与各种功能芯片之间的电互连。然而,随着功能芯片的数目在封装内增加,衬底与各种功能芯片之间的传导路径不合需要地增加。因此,传输损耗增加,且电性能受到不利影响。

技术实现思路

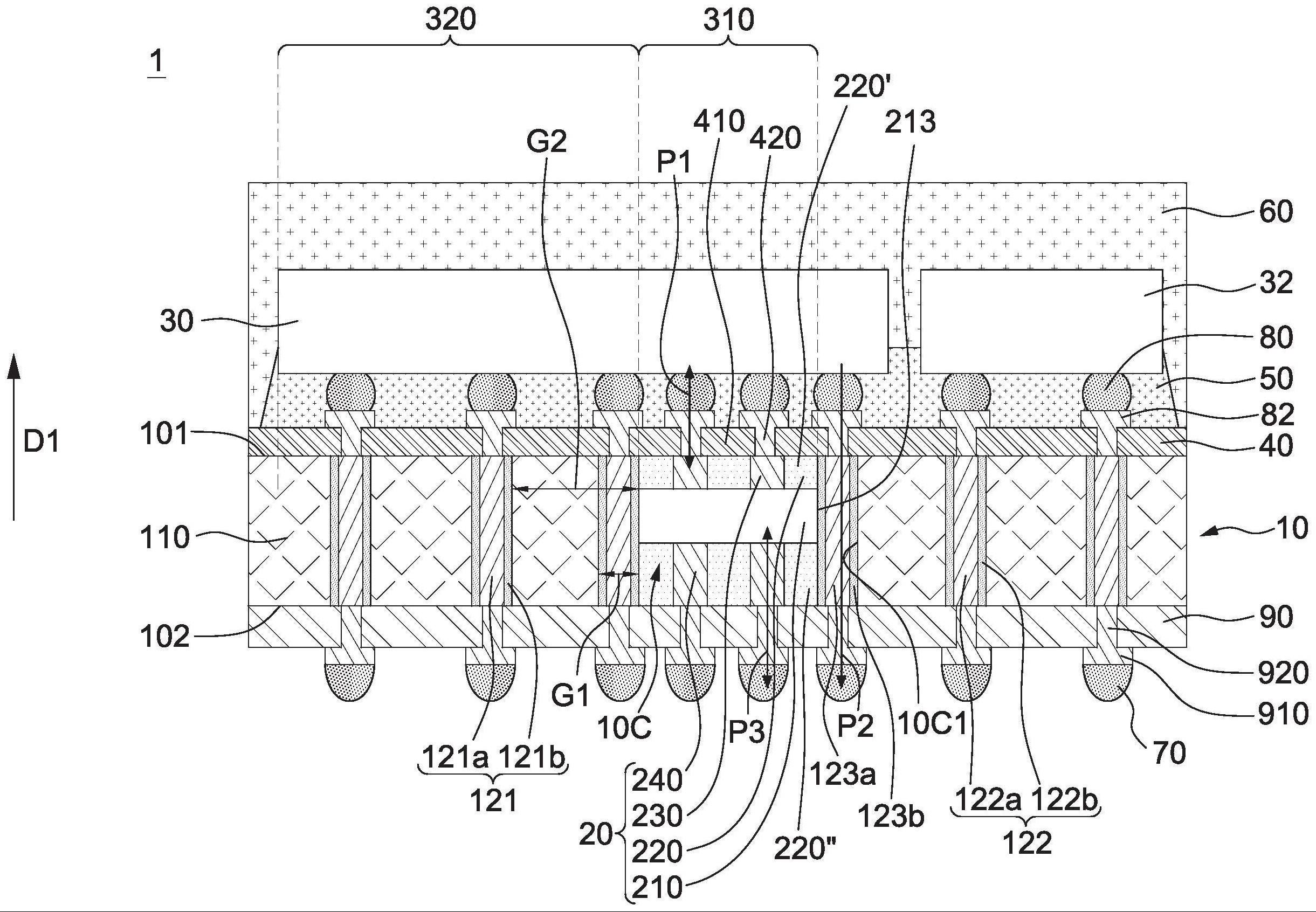

1、在一或多个实施例中,一种半导体封装结构包含衬底、第一电子组件和电子装置。第一电子组件安置于衬底之上。电子装置至少部分地嵌入衬底中。电子装置包含第二电子组件和加强件。第二电子组件经配置以用于将经调节电压(regulated voltage)提供到第一电子组件。加强件支撑第二电子组件。

2、在一或多个实施例中,一种半导体封装结构包含插入件(interposer)、第一电子组件和第一导电结构。插入件具有空腔。第一电子组件安置于空腔中。第一导电结构沿着第一电子组件的侧表面延伸且经配置以用于为插入件外部的第二电子组件提供散热。

3、在一或多个实施例中,一种半导体封装结构包含半导体插入件、第一电子组件、第二电子组件以及第一连接结构。半导体插入件具有上部表面。第一电子组件至少部分地嵌入半导体插入件中。第二电子组件安置于半导体插入件的上部表面之上。第二电子组件在第一电子组件之上。第一连接结构经配置以竖直地提供从第一电子组件到第二电子组件的第一电路径。

技术特征:

1.一种半导体封装结构,其包括:

2.根据权利要求1所述的半导体封装结构,其中所述衬底包括硅插入件。

3.根据权利要求2所述的半导体封装结构,其中所述硅插入件包括硅层和穿透所述硅层的第一硅穿孔。

4.根据权利要求1所述的半导体封装结构,其中所述电子装置包括封装,且所述加强件包括覆盖所述电子装置的第一侧的第一包封物。

5.根据权利要求4所述的半导体封装结构,其中所述衬底包括通过间隙与所述封装间隔开的硅层。

6.根据权利要求4所述的半导体封装结构,其中所述加强件进一步包括覆盖所述电子装置的第二侧的第二包封物,所述第二侧与所述第一侧相对。

7.根据权利要求4所述的半导体封装结构,其中所述电子装置进一步包括第一导电柱,所述第一导电柱穿透所述第一包封物且将所述第二电子组件电连接到所述第一电子组件。

8.根据权利要求1所述的半导体封装结构,其进一步包括覆盖所述电子装置的至少一部分的包封物。

9.一种半导体封装结构,其包括:

10.根据权利要求9所述的半导体封装结构,其进一步包括绝缘层,所述绝缘层邻近于所述第一电子组件的所述侧表面安置且经配置以阻止所述第一电子组件与所述第一导电结构之间的漏电。

11.根据权利要求9所述的半导体封装结构,其中所述第一导电结构包围所述第一电子组件。

12.根据权利要求9所述的半导体封装结构,其进一步包括:

13.根据权利要求9所述的半导体封装结构,其进一步包括第二导电结构,所述第二导电结构安置于所述第一电子组件上且将所述第一电子组件电连接到所述第二电子组件。

14.根据权利要求13所述的半导体封装结构,其进一步包括包封物,所述包封物在所述空腔中且包封所述第二导电结构。

15.根据权利要求13所述的半导体封装结构,其中所述第一导电结构在所述第二导电结构周围。

16.根据权利要求9所述的半导体封装结构,其进一步包括:

17.一种半导体封装结构,其包括:

18.根据权利要求17所述的半导体封装结构,其中所述半导体插入件包括多个导电通孔,且所述第二电子组件具有在所述第一电子组件之上的第一区和不同于所述第一区的第二区,所述第二区与所述半导体插入件的所述导电通孔连接。

19.根据权利要求18所述的半导体封装结构,其中所述半导体插入件具有空腔,所述空腔至少部分地在所述第一区下方且容纳所述第一电子组件。

20.根据权利要求17所述的半导体封装结构,其进一步包括第二连接结构,所述第二连接结构安置于所述第一电子组件的与所述第一连接结构相对的一侧处,所述第二连接结构经配置以提供从所述第一电子组件到电触点的第二电路径。

技术总结

提供一种半导体封装结构。所述半导体封装结构包含衬底、第一电子组件和电子装置。所述第一电子组件安置于所述衬底之上。所述电子装置至少部分地嵌入所述衬底中。所述电子装置包含第二电子组件和加强件。所述第二电子组件经配置以用于将经调节电压提供到所述第一电子组件。所述加强件支撑所述第二电子组件。

技术研发人员:谢孟伟

受保护的技术使用者:日月光半导体制造股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!