一种MOM电容及其制备方法、高频集成电路、芯片与流程

本申请属于半导体器件,尤其涉及一种mom电容及其制备方法、高频集成电路、芯片。

背景技术:

1、在集成电路设计领域,电容器占据和消耗了芯片的大部分面积,电容器的电容计算公式为c=εr*s/(4πkd),其中,εr是相对介电常数,s为电容极板的正对面积,d为电容极板的距离,k则是静电力常量。因此,采用较高的介电常数的介电材料制备的介电层可以获得更高的单位面积电容,但是高介电常数的介质层会影响集成电路的响应速度和功耗,因此电容的设计和选择变得十分重要。

2、目前集成电路中所需的电容器存在制备工艺复杂、单位面积较大、应用场景受限等问题。

技术实现思路

1、本申请提供了一种mom电容及其制备方法、高频集成电路、芯片,旨在解决目前集成电路中所需的电容器存在制备工艺复杂、单位面积较大、应用场景受限等问题。

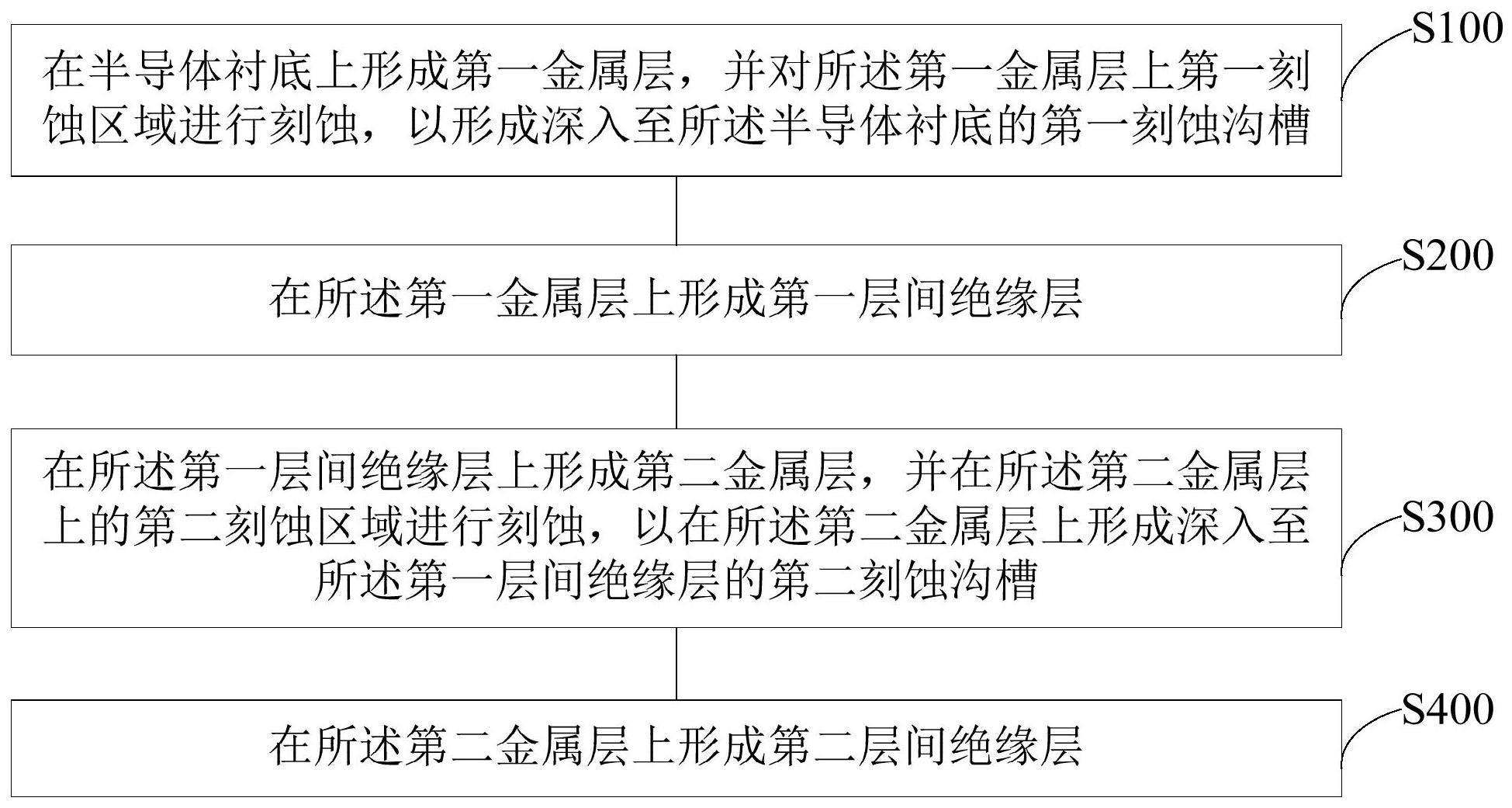

2、为了解决上述技术问题,本申请实施例第一方面提供了一种mom电容的制备方法,包括:

3、在半导体衬底上形成第一金属层,并对所述第一金属层上第一刻蚀区域进行刻蚀,以形成深入至所述半导体衬底的第一刻蚀沟槽;

4、在所述第一金属层上形成第一层间绝缘层;其中,所述第一层间绝缘层呈凸形结构,所述第一层间绝缘层的凸起部与所述半导体衬底接触,所述第一层间绝缘层包括氟碳杂质共掺杂氧化硅和磷硼杂质共掺杂氧化硅中的至少一项;

5、在所述第一层间绝缘层上形成第二金属层,并在所述第二金属层上的第二刻蚀区域进行刻蚀,以在所述第二金属层上形成深入至所述第一层间绝缘层的第二刻蚀沟槽;

6、在所述第二金属层上形成第二层间绝缘层;其中,所述第二层间绝缘层呈凸形结构,所述第二层间绝缘层的凸起部与所述第一层间绝缘层接触,所述第二层间绝缘层包括氟碳杂质共掺杂氧化硅和磷硼杂质共掺杂氧化硅中的至少一项。

7、在一个实施例中,所述在所述第一金属层上采用形成第一层间绝缘层包括:

8、在所述第一金属层上采用薄膜淀积工艺沉积第一介质材料以形成第一层间绝缘层;其中,所述第一介质材料中包含第一比例掺杂浓度的氟杂质和碳杂质,或者包含第一比例掺杂浓度的磷杂质和硼杂质。

9、在一个实施例中,所述在所述第二金属层上形成第二层间绝缘层包括:

10、在所述第二金属层上采用薄膜沉积工艺沉积第二介质材料以形成第二层间绝缘层;其中,所述第二介质材料中包含第二比例掺杂浓度的氟杂质和碳杂质,或者包含第二比例掺杂浓度注入磷杂质和硼杂质,所述第二比例掺杂浓度与所述第一比例掺杂浓度不同。

11、在一个实施例中,所述第一比例掺杂浓度与所述第一金属层与所述第二金属层之间的距离呈反比例关系。

12、在一个实施例中,所述制备方法还包括:

13、获取所述mom电容的电容参数,根据所述电容参数从调节所述第一比例掺杂浓度。

14、在一个实施例中,所述制备方法还包括:

15、获取所述mom电容的电容参数,根据所述电容参数从调节所述第一介质材料的掺杂浓度。

16、在一个实施例中,所述第一刻蚀沟槽与所述第二刻蚀沟槽的位置相对。

17、本申请实施例第二方面还提供了一种mom电容,所述mom电容由上述任一项所述的制备方法制备。

18、本申请实施例第三方面还提供了一种高频集成电路,所述高频集成电路包括如上述任一项所述的制备方法制备的mom电容。

19、本申请实施例第四方面还提供了一种芯片,包括如上述任一项实施例的mom电容。

20、本申请实施例与现有技术相比存在的有益效果是:

21、在第一金属层与第二金属层之间形成第一层间绝缘层,并在第二金属层上形成与第一层间绝缘层接触的第二层间绝缘层,其中,通过由氟碳杂质共掺杂氧化硅和磷硼杂质共掺杂氧化硅中的至少一项组成第一层间绝缘层,并由氟碳杂质共掺杂氧化硅和磷硼杂质共掺杂氧化硅中的至少一项组成第二层间绝缘层,从而在给定的金属层间结构下有效扩展mom电容的电容可变范围,便于设计人员能够在更小的尺寸空间下设计出所需的电容器,提升了集成电路的空间利用效率。

技术特征:

1.一种mom电容的制备方法,其特征在于,所述制备方法包括:

2.根据权利要求1所述的制备方法,其特征在于,所述在所述第一金属层上采用形成第一层间绝缘层包括:

3.根据权利要求2所述的制备方法,其特征在于,所述在所述第二金属层上形成第二层间绝缘层包括:

4.根据权利要求1所述的制备方法,其特征在于,所述第一比例掺杂浓度与所述第一金属层与所述第二金属层之间的距离呈反比例关系。

5.根据权利要求1所述的制备方法,其特征在于,所述制备方法还包括:

6.根据权利要求1所述的制备方法,其特征在于,所述制备方法还包括:

7.根据权利要求1-6任意一项所述的制备方法,其特征在于,所述第一刻蚀沟槽与所述第二刻蚀沟槽的位置相对。

8.一种mom电容,其特征在于,所述mom电容由权利要求1-7任一项所述的制备方法制备。

9.一种高频集成电路,其特征在于,所述高频集成电路包括如权利要求1-7任一项所述的制备方法制备的mom电容。

10.一种芯片,其特征在于,包括如权利要求1-7任一项制备方法制备的mom电容。

技术总结

本申请属于半导体技术领域,提供了一种MOM电容及其制备方法、高频集成电路、芯片,在第一金属层与第二金属层之间形成第一层间绝缘层,并在第二金属层上形成与第一层间绝缘层接触的第二层间绝缘层,其中,通过由氟碳杂质共掺杂氧化硅和磷硼杂质共掺杂氧化硅中的至少一项组成第一层间绝缘层,并由氟碳杂质共掺杂氧化硅和磷硼杂质共掺杂氧化硅中的至少一项组成第二层间绝缘层,从而在给定的金属层间结构下有效扩展MOM电容的电容可变范围,便于设计人员能够在更小的尺寸空间下设计出所需的电容器,提升了集成电路的空间利用效率。

技术研发人员:李菀婷,黄汇钦

受保护的技术使用者:天狼芯半导体(成都)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!