一种提升电容的半导体阵列基板的制造方法与流程

本发明属于显示装置的制造,具体是指一种提升电容的半导体阵列基板的制造方法。

背景技术:

1、液晶显示面板的工作原理是在两片平行的玻璃基板当中放置液晶分子,两片玻璃基板中间有许多垂直和水平的细小电线,通过通电与否来控制液晶分子改变方向,将背光模组的光线折射出来产生画面。通常液晶显示面板由彩膜(cf,colorfilter)基板、薄膜晶体管(tft,thinfilmtransistor)基板、夹于彩膜基板与薄膜晶体管基板之间的液晶(lc,liquidcrystal)及密封胶框(sealant)组成。

2、a-si(非晶硅)、ltps(低温多晶硅)、igzo(铟镓锌氧化物)是薄膜晶体管材料(tft)的种类。近年来,随着中小尺寸显示技术的发展,市场已呈现a-si、ltps等多种技术并存态势。相比之下,a-si技术展时间最长,技术较为简单,凭借较好的性价比等优势占据市场;ltps技术凭借成熟的供应链体系、较高性能等优势,也占扰一定的市场份额。

3、igzo是一种含有铟、镓和锌的非晶氧化物,载流子迁移率是非晶硅的20~30倍,可以大大提高tft对像素电极的充放电速率,提高像素的响应速度,具备更快的面板刷新频率,可实现超高分辨率tft-lcd。

4、目前已应用于tft基板的array制造工艺主要集中在8mask的外挂机种、9masktop-comtic机种以及10mask的mid-comtic机种。为了节省成本,现有的a-si机种也同步开发了6mask的top-com外挂机种,不仅缩短了cycletime,并且简化了工艺流程,有效的提高效益。

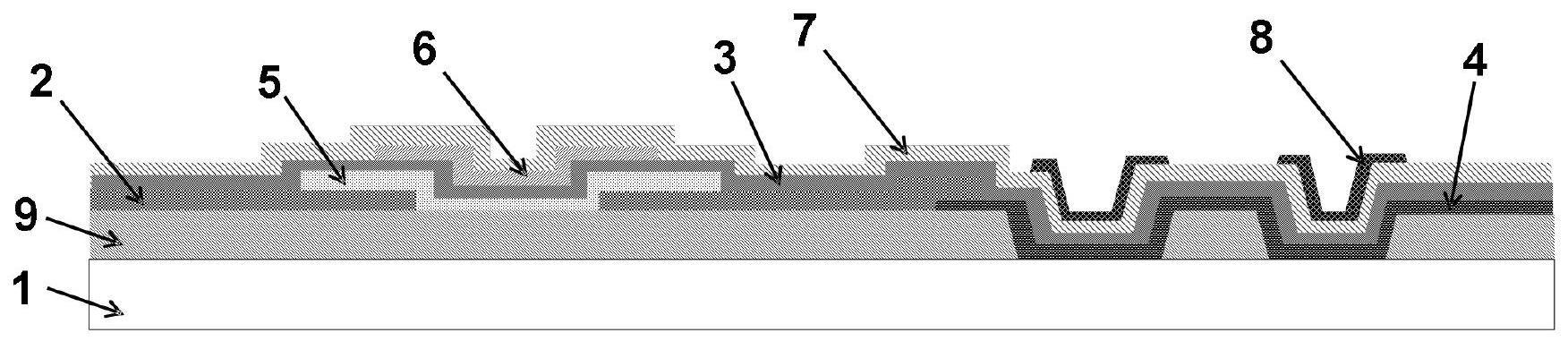

5、基于6mask的top-com外挂机种a-si阵列板制造工艺如果直接用来生产igzo阵列板,结合基板设计与制程工艺发现,由于6maska-si阵列板制造工艺设计(如图1所示)省略了传统的tft器件上的pv绝缘膜层及有机平坦层oc,像素电极pe-ito设计与a-si共平面,传统的a-si图案化工艺采用的是干蚀刻方式,而像素电极pe-ito为草酸湿蚀刻。若该工艺直接生产igzo阵列板后,igzo蚀刻方式也为草酸湿蚀刻,不免造成无论先后图案化igzo还是ito,都会对另一道膜层的图案造成损坏,从而影响画素无法正常显示。

技术实现思路

1、本发明的所要解决的技术问题在于提供一种提升电容的半导体阵列基板的制造方法,适用于6mask的top-com外挂机种。

2、本发明是这样实现的:

3、一种提升电容的半导体阵列基板的制造方法,包括如下步骤:

4、第一步:依序在玻璃基板上采用cvd方式沉积一层siox缓冲层;

5、第二步:采用公共电极层光罩,搭配负型光阻,进行曝光显影制程;

6、第三步:对显影后的位置进行干蚀刻,蚀刻掉未被光阻覆盖位置的siox;

7、第四步:剥膜掉负型光阻;

8、第五步:在所述siox缓冲层沉积像素电极层,并进行图案化,随后进行低温220°退火,制程晶化;

9、第六步:在图案化后的所述像素电极层上采用pvd方式沉积源漏极金属层;

10、第七步:在所述源漏极金属层上采用pvd方式沉积一层igzo有源层,并图案化;

11、第八步:采用cvd方式沉积一层第一绝缘层;

12、第九步:在所述第一绝缘层上图案化形成栅极金属层;

13、第十步:在所述栅极金属层上采用cvd方式沉积第二绝缘层,作为钝化绝缘层,用于保护tft器件,同步作为像素电容;

14、第十一步:在所述第二绝缘层上沉积一层公共电极层。

15、进一步地,所述第五步中的所述像素电极层,选用ito。

16、进一步地,所述第六步中的所述源漏极金属层,选用mo/al/mo或ti/al/ti。

17、进一步地,所述第八步中的所述第一绝缘层,选用siox。

18、进一步地,所述第九步中的所述栅极金属层,选用mo/al/mo或ti/al/ti。

19、进一步地,所述第十步中的所述第二绝缘层,选用siox。

20、进一步地,所述第十一步中的所述公共电极层,选用ito。

21、本发明的优点在于:本发明的方法在第一绝缘层成膜后,优先沉积并图案化像素电极层,并对像素电极层进行220°的制程退火,晶化后的像素电极可抗草酸蚀刻,在图案化igzo有源层时不会使像素电极出现被草酸过蚀刻的现象。成膜顺序的改变虽然有效避免了像素电极ito和有源层igzo共存的问题,但是对于igzotft器件来说,其tft器件的电学性能对第一绝缘层与igzo之间的界面也是非常敏感,此处称为igzo前沟道。如果前沟道经过多次的曝光、水洗、草酸湿蚀刻、剥膜及低温退火制程,其前沟道的缺陷态会增多,igzotft器件在正常工作状态下其电学特性会表现的非常不稳定,如大尺寸阵列基板玻璃上不同位置的vth会呈现不同程度的左右偏移,使得产品稳定性不佳,最终造成产品低良。因此,本发明在原a-si制程不改变6mask的光罩数量基础上,改变了栅极金属层、第一绝缘层、源漏极金属层、有源层及像素电极ito的成膜顺序,不仅有效避免了像素电极ito和igzo有源层共存的问题,而且间接优化了有源层前沟道的界面性能,提高了产品稳定性。成膜顺序的改变虽然有效避免了像素电极ito和igzo有源层共存的问题,但是tft器件的有源层从a-si直接转换成igzo,为了确保电性的稳定性,会同步改变原有tft器件中的膜层膜质,如第二绝缘层从sinx(有源层为a-si)转换成siox(有源层为igzo),这是因为sinx中含有大量的h离子,会对bce结构igzo背沟道造成不可逆的影响,使得器件稳定性不佳,vth偏移,并且根据以往调试经验,第二绝缘层转换成siox后厚度会进行增厚,确保电性稳定,然后在现有6mask制程设计之下,膜层厚度的增加会同步造成像素电极ito与公共电极ito之间电容的减少,电容过小会直接影响到原有设计的画面正常显示。因此,本发明在不增加光罩情况下,在玻璃基板与源漏极金属层之间增加一层siox缓冲层,利用现有的公共电极层光罩搭配负型光阻,进行图案化,在不影响透过率和增加光罩成本情况下,可有效的增加像素电容面积,抵消掉因第二绝缘层厚度增加导致的像素电容减少,故解决了现有产品的a-si半导体层转igzo半导体层的有效转换问题。

技术特征:

1.一种提升电容的半导体阵列基板的制造方法,其特征在于:包括如下步骤:

2.如权利要求1所述的一种提升电容的半导体阵列基板的制造方法,其特征在于:所述第五步中的所述像素电极层,选用ito。

3.如权利要求1所述的一种提升电容的半导体阵列基板的制造方法,其特征在于:所述第六步中的所述源漏极金属层,选用mo/al/mo或ti/al/ti。

4.如权利要求1所述的一种提升电容的半导体阵列基板的制造方法,其特征在于:所述第八步中的所述第一绝缘层,选用siox。

5.如权利要求1所述的一种提升电容的半导体阵列基板的制造方法,其特征在于:所述第九步中的所述栅极金属层,选用mo/al/mo或ti/al/ti。

6.如权利要求1所述的一种提升电容的半导体阵列基板的制造方法,其特征在于:所述第十步中的所述第二绝缘层,选用siox。

7.如权利要求1所述的一种提升电容的半导体阵列基板的制造方法,其特征在于:所述第十一步中的所述公共电极层,选用ito。

技术总结

一种提升电容的半导体阵列基板的制造方法,包括:依序在玻璃基板上沉积一层SiOx缓冲层;采用公共电极层光罩,搭配负型光阻,进行曝光显影制程;对显影后的位置进行干蚀刻,蚀刻掉未被光阻覆盖位置的SiOx;剥膜掉负型光阻;沉积像素电极层,并进行图案化,随后进行低温220°退火,制程晶化;沉积源漏极金属层;沉积一层IGZO有源层,并图案化;沉积一层第一绝缘层;图案化形成栅极金属层;沉积第二绝缘层,作为钝化绝缘层,同步作为像素电容;沉积一层公共电极层。本发明解决了现有产品的a‑Si半导体层转IGZO半导体层的有效转换问题。

技术研发人员:陈伟,卢盼

受保护的技术使用者:华映科技(集团)股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!