一种增强型GaNHEMT器件及其制备方法与流程

本发明涉及半导体器件,尤其涉及一种增强型gan hemt器件及其制备方法。

背景技术:

1、相对于si材料,gan材料具有禁带宽度大、击穿场强高、极化系数高、电子迁移率和电子饱和漂移速率高等一系列性能优势,gan基功率器件受到了越来越多的关注。由于gan材料的特点,gan基功率器件是天然的耗尽型器件,这种耗尽型器件对器件在电路中的应用造成了障碍,人们必须用一颗si mos器件与耗尽型gan器件级联,才能实现在电路上的应用。

2、而对于增强型gan器件,不需要级联si mos器件,单个器件就能实现在电路中的开关作用。增强型器件开发的难度较高,人们研究了各种各样的技术手段,来实现增强型器件。目前主流的增强型gan器件是采用p型栅帽层技术---在algan表面生长一层p型gan层,通过p-gan对栅极下方的二维电子气耗尽,实现增强型(如图1)。但由于p-gan的耗尽能力是有限的,需要牺牲algan势垒层厚度降低二维电子气浓度来实现,导致传统p型栅帽层技术实现增强型存在以下缺点:电流密度相对于耗尽型器件小,同时可实现的阈值电压比较低,驱动电压范围比较窄(最大不能超过7v),存在可靠性风险。

技术实现思路

1、本发明的目的在于提供一种增强型gan hemt器件及其制备方法,本发明的增强型gan hemt器件电流密度更大,驱动电压范围较宽,可靠性高。

2、为了实现上述发明目的,本发明提供以下技术方案:

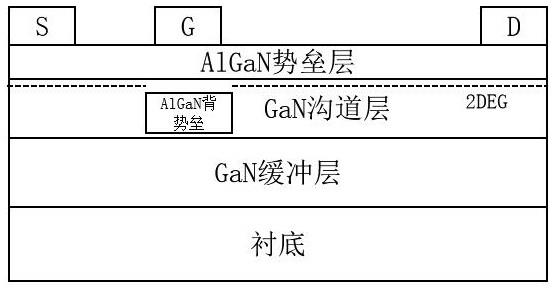

3、本发明提供了一种增强型gan hemt器件,从下到上依次包括:衬底、gan缓冲层、gan沟道层和algan势垒层;在所述algan势垒层上方设有源电极、栅电极和漏电极;在栅下区域所述gan沟道层中设有algan背势垒。

4、优选的,在所述源电极和漏电极之间、栅电极下方、algan势垒层上方,还包括栅介质层。

5、优选的,所述algan背势垒的厚度为10~50nm。

6、优选的,所述algan背势垒的化学式为alxga1-xn,其中,x=0.1~0.3。

7、优选的,所述gan沟道层的厚度为100~500nm。

8、优选的,所述栅介质层的厚度为5~50nm;所述栅介质层的组成为sin、sio2、al2o3或aln。

9、本发明提供了上述方案所述增强型gan hemt器件的制备方法,包括以下步骤:在衬底上依次外延生长gan缓冲层、下层gan沟道层和algan背势垒层,除去栅下区域之外的algan背势垒层,形成algan背势垒;二次外延生长上层gan沟道层及algan势垒层,制作源电极、栅电极和漏电极,得到所述增强型gan hemt器件。

10、本发明提供了上述方案所述增强型gan hemt器件的另一种制备方法,包括以下步骤:在衬底上依次外延生长gan缓冲层和下层gan沟道层;在所述下层gan沟道层表面栅下区域外延生长algan背势垒,继续外延上层gan沟道层及algan势垒层,制作源电极、栅电极和漏电极,得到所述增强型gan hemt器件。

11、优选的,形成algan势垒层后,还包括制备栅介质层。

12、优选的,所述栅介质层通过低压力化学气相沉积、等离子体增强化学气相沉积或原子层沉积制备得到。

13、本发明提供了一种增强型gan hemt器件,从下到上依次包括:衬底、gan缓冲层、gan沟道层和algan势垒层;在所述algan势垒层上方设有源电极、栅电极和漏电极;在栅下区域所述gan沟道层中设有algan背势垒。

14、本发明在栅下区域gan沟道层中设有algan背势垒,实现耗尽栅下二维电子气(2deg)达成增强型的目的。本发明不牺牲algan势垒层厚度,电流密度更大;驱动电压范围比较宽(最大可以达到30v)。

15、此外,本发明可以通过调节algan背势垒的厚度和其中al组分含量,调整增强型器件的阈值电压。

16、进一步的,本发明还能实现mis-hemt结构(如图3所示),可以在栅电极下方设有栅介质层,起到减小漏电、提高可靠性的作用。

技术特征:

1.一种增强型gan hemt器件,其特征在于,从下到上依次包括:衬底、gan缓冲层、gan沟道层和algan势垒层;在所述algan势垒层上方设有源电极、栅电极和漏电极;在栅下区域所述gan沟道层中设有algan背势垒。

2.根据权利要求1所述的增强型gan hemt器件,其特征在于,在所述源电极和漏电极之间、栅电极下方、algan势垒层上方,还包括栅介质层。

3.根据权利要求1或2所述的增强型gan hemt器件,其特征在于,所述algan背势垒的厚度为10~50nm。

4.根据权利要求1或2所述的增强型gan hemt器件,其特征在于,所述algan背势垒的化学式为alxga1-xn,其中,x=0.1~0.3。

5.根据权利要求1或2所述的增强型gan hemt器件,其特征在于,所述gan沟道层的厚度为100~500nm。

6.根据权利要求2所述的增强型gan hemt器件,其特征在于,所述栅介质层的厚度为5~50nm;所述栅介质层的组成为sin、sio2、al2o3或aln。

7.权利要求1~6任一项所述增强型gan hemt器件的制备方法,包括以下步骤:在衬底上依次外延生长gan缓冲层、下层gan沟道层和algan背势垒层,除去栅下区域之外的algan背势垒层,形成algan背势垒;二次外延生长上层gan沟道层及algan势垒层,制作源电极、栅电极和漏电极,得到所述增强型gan hemt器件。

8.权利要求1~6任一项所述增强型gan hemt器件的制备方法,包括以下步骤:在衬底上依次外延生长gan缓冲层和下层gan沟道层;在所述下层gan沟道层表面栅下区域外延生长algan背势垒,继续外延上层gan沟道层及algan势垒层,制作源电极、栅电极和漏电极,得到所述增强型gan hemt器件。

9.根据权利要求7或8所述的制备方法,其特征在于,形成algan势垒层后,还包括制备栅介质层。

10.根据权利要求9所述的制备方法,其特征在于,所述栅介质层通过低压力化学气相沉积、等离子体增强化学气相沉积或原子层沉积制备得到。

技术总结

本发明提供了一种增强型GaN HEMT器件及其制备方法,属于半导体器件技术领域。本发明制备的增强型GaN HEMT器件在相同器件面积下,相对于传统p‑GaN栅HEMT器件,输出电流提高50%~200%,栅漏电降低1~4个数量级,阈值电压可以在1~5V范围调整。驱动电压可以工作在10V,最大可以工作在30V,p‑GaN栅HEMT器件工作在6V,最大不能超过7V。本发明的增强型GaN HEMT器件电流密度更大,驱动电压范围较宽,可靠性高。

技术研发人员:宋亮,朱廷刚,李亦衡,武乐可,夏远洋

受保护的技术使用者:江苏能华微电子科技发展有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!