一种新型栅极总线结构的形成方法与流程

本发明属于半导体,具体涉及一种新型栅极总线结构的形成方法。

背景技术:

1、由于栅极总线的宽度较大,当漏极电极被反向偏置时,延伸自mosfet元胞形成通道基区和高浓度基区的耗尽区在栅极总线的两端可能会导致无法扩展连接,导致两端耗尽层电场局部集中,耐压降低,因此为了提高器件的耐压能力,会在栅极总线的正下方形成了一个高浓度p型区域,但是p型区域会存有寄生二极管,导致降低器件可靠性,以及导致p型区域正向不导通。现提出一种可以解决反向耐压问题,增加导通区域面积,提高芯片面积利用率的新型栅极总线结构的方法。

技术实现思路

1、针对现有技术的不足,本发明的目的在于提供一种新型栅极总线结构的形成方法,解决了反向耐压问题,也增加了导通区域面积,提高芯片面积的利用率。

2、本发明的目的可以通过以下技术方案实现:

3、一种新型栅极总线结构的形成方法,包括以下步骤:

4、在n型衬底上形成n型外延层;

5、在n型衬底的背面形成漏电极;

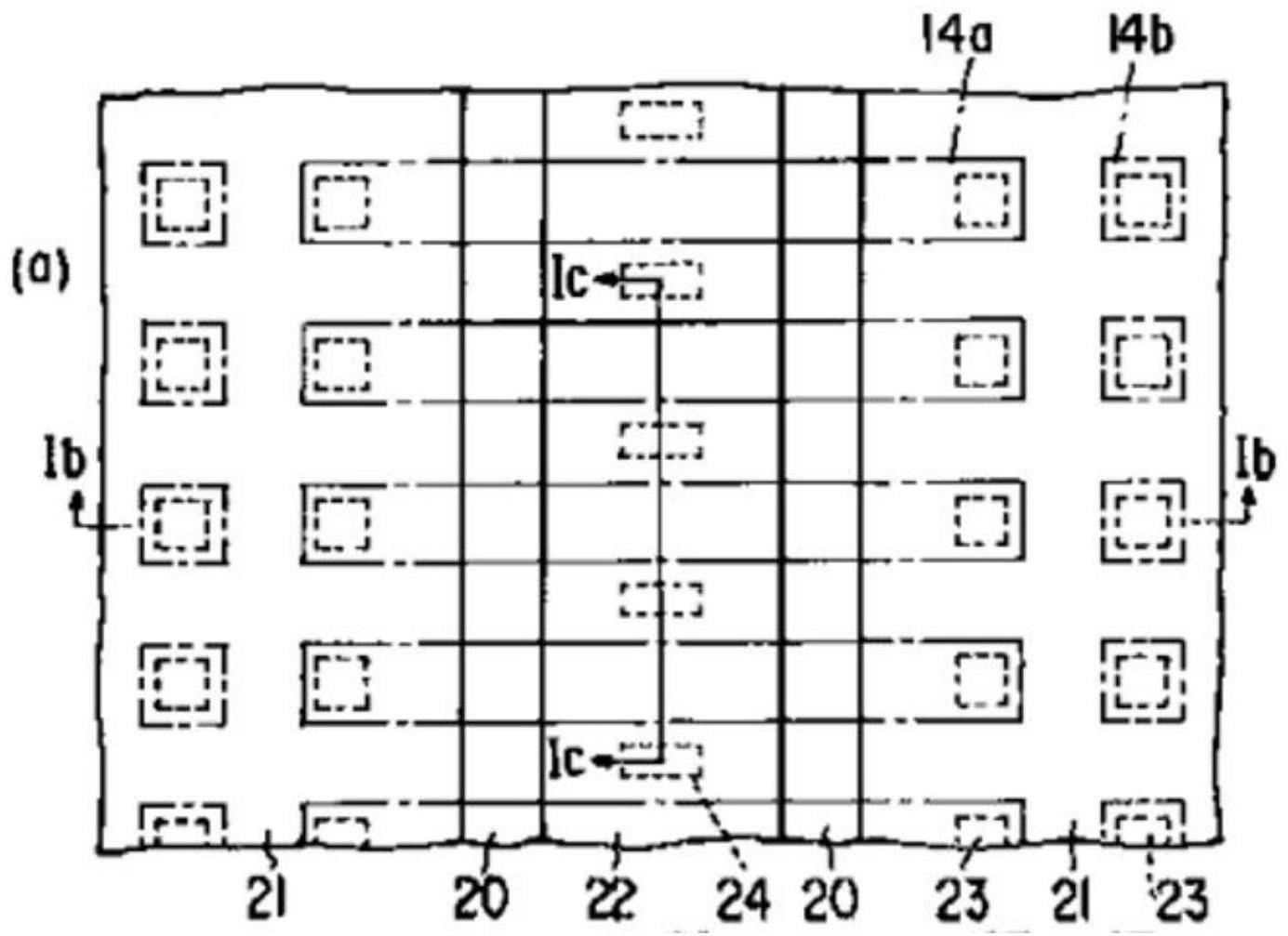

6、在n型外延层内,形成了多个fet元胞14a和fet元胞14b,fet元胞14a各自形成为条形元胞,fet元胞14b在fet单元14a的两端处各自形成为方形的元胞;

7、在通道基区内形成高浓度基区和高浓度n型漏区;

8、在n型外延层的表面上生长介质层;

9、在介质层上沉积多晶硅作为栅极电极;

10、在栅极电极上形成层间绝缘膜、源极电极和栅极总线,通过接触区将源极电极与高浓度基区连接,通过接触区将源极电极和高浓度n型漏区连接;

11、栅极总线通过接触区在每个fet元胞14a之间与栅极连接;

12、通过栅极总线,连接栅极电极和外部电极的栅键合垫区域。

13、进一步的,所述条形元胞位于栅极总线的下方。

14、进一步的,所述介质层和栅极电极设置在n型外延层、通道基区和高浓度n型漏区上。

15、进一步的,每个所述fet元胞14a和fet元胞14b都由通道基区、高浓度基区和高浓度n型漏区组成。

16、进一步的,所述fet元胞14a和fet元胞14b的各个区域是同一步工艺形成。

17、本发明的有益效果:

18、本发明通过在栅极总线下方去除p区,形成了短条形元胞,既可以解决了电场集中问题,也提高器件的反向耐压性能,同时通过减少p区的形成,避免器件中寄生二极管的存在,提高了器件的可靠性,也减少一道注入工艺,降低生产成本;除此以外,还可以增加器件的导通面积。

技术特征:

1.一种新型栅极总线结构的形成方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的一种新型栅极总线结构的形成方法,其特征在于,所述条形元胞位于栅极总线的下方。

3.根据权利要求1所述的一种新型栅极总线结构的形成方法,其特征在于,所述介质层(18)和栅极电极(19)设置在n型外延层(12)、通道基区一(15)和n型漏区(17)上。

4.根据权利要求1所述的一种新型栅极总线结构的形成方法,其特征在于,每个所述fet元胞(14a)和fet元胞(14b)都由通道基区一(15)、基区二(16)和n型漏区(17)组成。

5.根据权利要求1所述的一种新型栅极总线结构的形成方法,其特征在于,所述fet元胞(14a)和fet元胞(14b)的各个区域是同一步工艺形成。

6.权利要求1-5任一所述的方法形成栅极总线结构。

技术总结

本发明公开一种新型栅极总线结构的形成方法,属于半导体技术领域,包括以下步骤:在衬底上形成N型外延层;在N型衬底的背面形成漏电极;在N型外延层内,形成了多个FET元胞14a和FET元胞14b,FET元胞14a各自形成为条形元胞,FET元胞14b在FET单元14a的两端处各自形成为方形的元胞;在通道基区内形成高浓度基区和高浓度N型漏区。本发明通过在栅极总线下方去除P区,形成了短条形元胞,既可以解决了电场集中问题,也提高器件的反向耐压性能,同时通过减少P区的形成,避免器件中寄生二极管的存在,提高了器件的可靠性,也减少一道注入工艺,降低生产成本;除此以外,还可以增加器件的导通面积。

技术研发人员:马利奇,铃木键之,余恒文,李旻姝,洪吉文,郑英豪

受保护的技术使用者:浙江萃锦半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!