使用W2W熔合接合将碳纳米纤维集成到半导体装置中的方法及设备与流程

本技术涉及半导体装置封装。更特定来说,本技术的一些实施例涉及用于改进半导体装置及装置组合件的弹性及导热性的技术。

背景技术:

1、半导体裸片(包含存储器芯片、微处理器芯片、逻辑芯片及成像器芯片)可通过以网格图案在衬底上个别地或以裸片堆叠形式安装多个半导体裸片来组装。存储器芯片可制造在装置晶片中且接着被单切。组合件及芯片可用于移动装置、计算及/或汽车产品。显著热问题可源自将许多裸片堆叠在一起及/或在小封装或装置中包含多个裸片/芯片。需要稳健且高效的热分配器来防止半导体装置过热。

技术实现思路

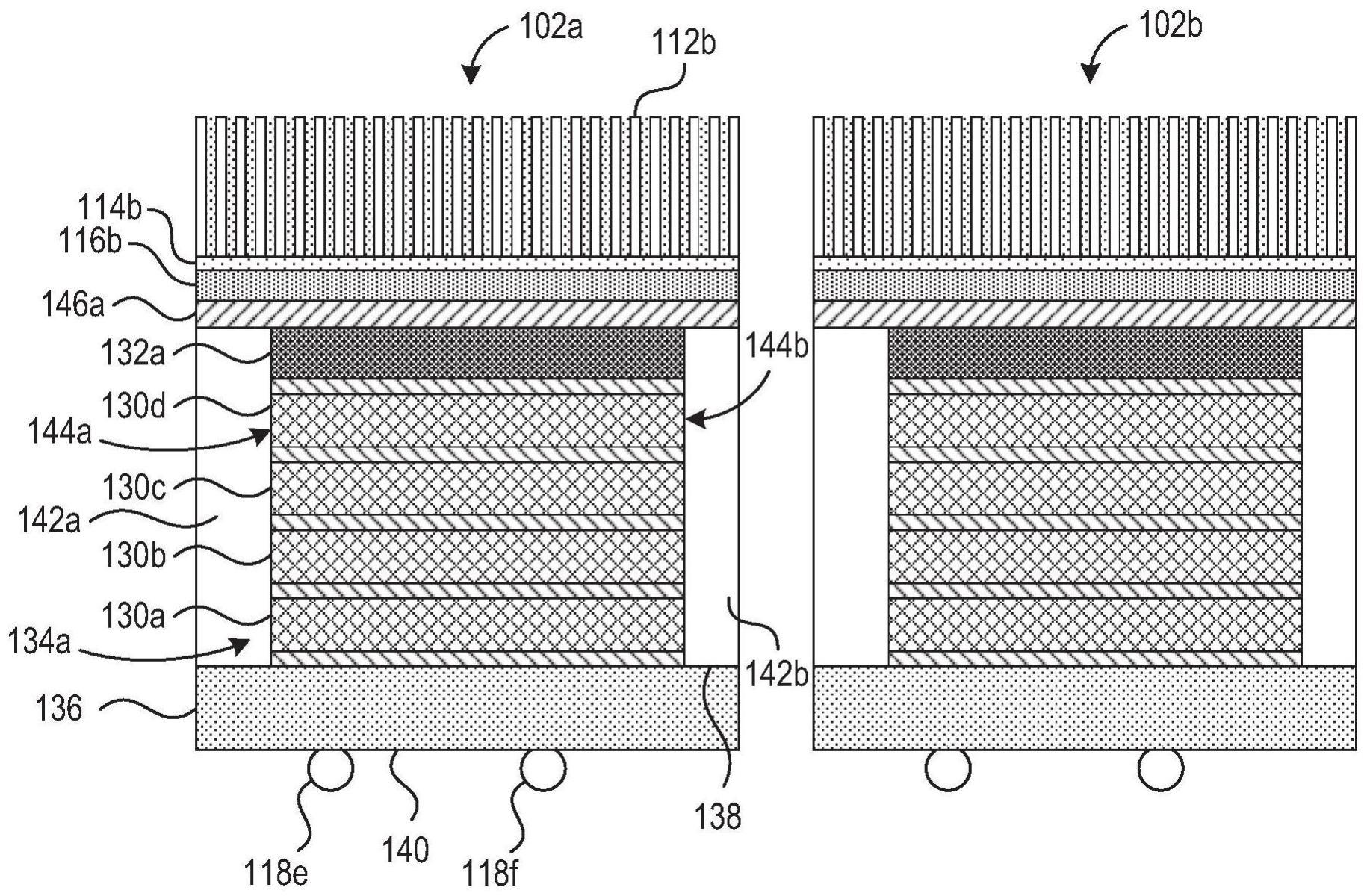

1、一方面,本公开提供一种包含用于热耗散的碳纳米纤维的半导体装置组合件,其包括:碳纳米纤维(cnf)层;模制化合物,其囊封所述cnf层以形成经囊封cnf层,所述模制化合物在所述经囊封cnf层内的个别邻近cnf之间延伸;氧化硅(sio)层,其跨越所述经囊封cnf层的底部表面延伸;及多个裸片堆叠,其形成在装置晶片上方,其中所述多个裸片堆叠囊封在第二模制化合物中,其中所述裸片堆叠及所述第二模制化合物的上表面接合到所述sio层。

2、另一方面,本公开提供一种用于组装经囊封cnf层与装置晶片的方法,其包括:将多个裸片堆叠附接到装置晶片;施加模制材料以囊封所述多个裸片堆叠;以及将经囊封cnf层附接在包含所述裸片堆叠及所述模制材料的上表面的安装表面上方。

3、另一方面,本公开进一步提供一种包含用于热耗散的碳纳米纤维的半导体装置组合件,其包括:cnf层;模制化合物,其囊封所述cnf层以形成经囊封cnf层,所述模制化合物在所述经囊封cnf层内的个别邻近cnf之间延伸,且其中所述经囊封cnf层内的个别cnf的至少一部分的上边缘沿所述经囊封cnf层的上表面暴露;sio层,其跨越所述经囊封cnf层的底部表面延伸;及裸片堆叠,其形成在存储器装置上方,其中所述裸片堆叠包含彼此附接的至少两个裸片,其中所述裸片堆叠囊封在第二模制化合物中,其中所述裸片堆叠及所述模制化合物的上表面接合到所述sio层。

技术特征:

1.一种包含用于热耗散的碳纳米纤维的半导体装置组合件,其包括:

2.根据权利要求1所述的半导体装置组合件,其中所述装置晶片及所述经囊封cnf层的直径大约为12英寸或300cm。

3.根据权利要求1所述的半导体装置组合件,其中所述经囊封cnf层内的个别cnf的至少一部分的上边缘沿所述经囊封cnf层的上表面暴露。

4.根据权利要求1所述的半导体装置组合件,其中所述多个裸片堆叠中的每一者包含相等数目个裸片。

5.根据权利要求1所述的半导体装置组合件,其中聚合物层在所述sio层与所述裸片堆叠及所述第二模制化合物的所述上表面之间延伸,其中所述聚合物层与所述sio层彼此熔合接合。

6.根据权利要求1所述的半导体装置组合件,其中聚合物层在所述sio层与所述裸片堆叠及所述第二模制化合物的所述上表面之间延伸,其中所述聚合物层与所述sio层彼此冷焊接。

7.根据权利要求6所述的半导体装置组合件,其中所述聚合物层具有在约0.5微米与2.0微米之间的厚度。

8.根据权利要求1所述的半导体装置组合件,其中囊封所述cnf层的所述模制化合物包括具有颗粒的环氧基液体化合物、不具有颗粒的环氧基液体化合物、颗粒化合物、薄膜基底填料、薄膜基化合物、树脂基囊封剂或聚合物中的至少一者。

9.根据权利要求1所述的半导体装置组合件,其中所述经囊封cnf层的厚度小于或等于约200微米。

10.一种用于组装经囊封碳纳米纤维cnf层与装置晶片的方法,其包括:

11.根据权利要求10所述的方法,其进一步包括在附接所述经囊封cnf层之前,减薄所述模制材料及所述多个裸片堆叠的顶部裸片以暴露所述安装表面。

12.根据权利要求10所述的方法,其进一步包括在附接所述经囊封cnf层之前在所述安装表面上方施加聚合物层。

13.根据权利要求10所述的方法,其中所述附接进一步包括将邻近层彼此熔合接合。

14.根据权利要求13所述的方法,其中所述邻近层包括氧化硅层及聚合物层。

15.根据权利要求10所述的方法,其进一步包括单切所述多个裸片堆叠。

16.一种包含用于热耗散的碳纳米纤维的半导体装置组合件,其包括:

17.根据权利要求16所述的半导体装置组合件,其进一步包括跨越所述裸片堆叠及所述模制化合物的所述上表面延伸的聚合物层,其中所述聚合物层进一步接合到所述sio层。

18.根据权利要求17所述的半导体装置组合件,其中所述聚合物层比所述经囊封cnf层更薄。

19.根据权利要求16所述的半导体装置组合件,其中所述sio层与所述裸片堆叠之间的所述接合是冷焊接、熔合接合、氧化物对氧化物接合或电介质对电介质接合中的一者。

20.根据权利要求16所述的半导体装置组合件,其中囊封所述cnf层的所述模制化合物包括具有颗粒的环氧基液体化合物、不具有颗粒的环氧基液体化合物、颗粒化合物、薄膜基底填料、薄膜基化合物、树脂基囊封剂或聚合物中的至少一者。

技术总结

本公开涉及使用W2W熔合接合将碳纳米纤维集成到半导体装置中的方法及设备。一种包含用于热耗散的碳纳米纤维CNF的半导体装置组合件具有CNF层。模制化合物囊封所述CNF层以形成经囊封CNF层。所述模制化合物在所述经囊封CNF层内的个别邻近CNF之间延伸,且所述经囊封CNF层内的个别CNF的至少一部分的上边缘沿所述经囊封CNF层的上表面暴露。所述CNF层的所述上表面可移除地附接到载体晶片的底部表面。

技术研发人员:周卫,B·K·施特雷特,A·R·格里芬

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!