一种提升沟槽型SICMOSFET器件开关速度的方法与流程

本发明属于半导体器件,尤其涉及一种提升沟槽型sic mosfet器件开关速度的方法。

背景技术:

1、一般地,sic mosfet器件与si mosfet器件相比具有低的导通电阻、耐高温、高的开关速率等特点,在汽车、交通、高压变频等领域有很大的应用优势。但是,沟槽型sicmosfet器件的沟槽底部的结构特点却仍然导致沟槽型sic mosfet器件的开关速度变慢,而决定开关速度快慢的是沟槽底部电容和栅极电荷。

2、沟槽型sicmosfet器件的电容值是非线性的,它与器件的结构、形态、相关电压有关;在沟槽型sic mosfet结构中,电容有三种,分别是栅源电容(cgs)、栅漏电容(cgd)、源漏电容(csd),即输入电容、输出电容和反向电容,其表达式为cgd=crss,cgs=ciss-crss,cds=coss–crss。(ciss是输入电容,coss是输出电容,crss是反向电容。)假设源漏、栅源端均断开,那么只有反向电容(crss),此时crss=cgd。如图2所示,反向电容和沟槽底部形态有关。

3、当ig>0时,栅源电容和栅漏电容在充电,栅极电压升高的时候,栅源电压就等于开启电压,此时器件会形成导电沟道,栅极电流流向漏极,由于栅漏电容的原因栅极电流一部分会被使用,栅源电压在一定的时间段就反应出一定的值,产生开关延迟。如图3中点b和c的状态所示,我们把发生延迟的这段时间称为米勒平台。想要进一步提高开关的速度,就要缩短这段发生延时的时间,此后想要进一步提升栅极电压的话,器件变为开启状态,此时栅极电压只有受导通电阻和漏极电流的影响,如图3中d点状态。

4、所以,为了避免cgd过大,进一步减慢器件的开关速率,降低器件的损耗,器件的结构方法显得尤为重要,传统的器件结构方法包括以下两种方法:

5、一、首先,在sic外延层上形成沟槽;其次,在sic外延层上形成注入图案;再次,在在沟槽底部注入大量的离子;再次,在沟槽底部生长介质层膜;最后,生长多晶硅;虽然上述方式能够在沟槽底部生长厚的氧化层薄膜,但是注入会导致沟槽侧壁栅氧比目标设定值厚70%多,进而影响沟槽侧壁氧化层的质量。

6、二、首先,在sic外延层上形成沟槽;其次,在沟槽侧壁和底部生长nitride;再次,刻蚀沟槽底部的nitride;再次,在刻蚀完成的沟槽底部生长介质层膜;最后,在刻蚀掉多余的nitride并生长多晶硅;虽然上述方式不会如方案一使得侧壁氧化层厚,但是会有“鸟嘴”现象产生。

7、现提出一种新的器件结构方法,以解决上述问题。

技术实现思路

1、针对现有技术的不足,本发明提供了一种提升沟槽型sic mosfet器件开关速度的方法,解决了上述问题。

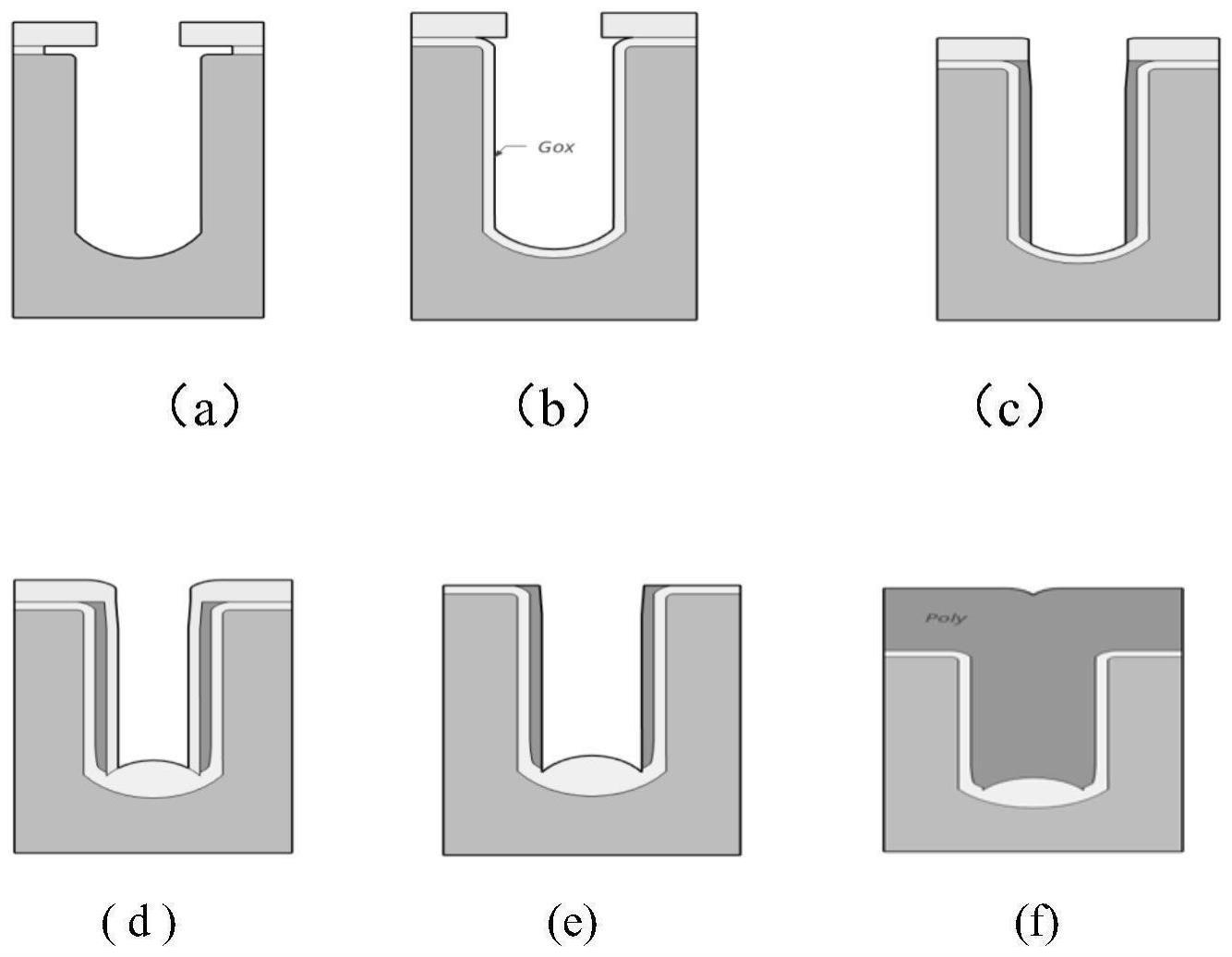

2、为实现以上目的,本发明通过以下技术方案予以实现:一种提升沟槽型sicmosfet器件开关速度的方法,包括以下步骤:

3、s1、在sic外延层表面形成沟槽;

4、s2、沟槽底部和侧壁生长栅氧化膜;

5、s3、在栅极氧化膜上沉积多晶硅膜,并且对沟槽底部多晶硅膜进行刻蚀;

6、s4、在刻蚀后的多晶硅薄膜上沉积nitride;

7、s5、刻蚀沟槽nitride;

8、s6、在刻蚀nitride的多晶硅薄膜上生长氧化层;

9、s7、去除剩余的nitride;

10、s8、在完成s7的操作后在沟槽内涨一层多晶硅,

11、其中,所述多晶硅薄膜厚度为在所述多晶硅薄膜上沉积的nitride的厚度为

12、在上述技术方案的基础上,本发明还提供以下可选技术方案:

13、进一步的技术方案:所述多晶硅膜与nitride的厚度比例为1:1.67~1:1.5。

14、进一步的技术方案:所述sic外延层的型号可与sic晶圆相同或者不同,其中所述sic晶圆为晶向且为n型或者p型。

15、进一步的技术方案:所述s5中刻蚀沟槽中的nitride的方法为括干法刻蚀。

16、进一步的技术方案:所述沟槽整体为u形,所述沟槽圆滑过渡至sic外延层。

17、上述提升沟槽型sic mosfet器件开关速度的方法在sic mosfet器件制造中的应用

18、有益效果

19、本发明提供了一种提升沟槽型sic mosfet器件开关速度的方法,与现有技术相比具备以下有益效果:

20、1、能够通过在sic外延层表面形成沟槽并在沟槽底部和侧壁生长栅极氧化膜,在形成的栅极氧化膜上沉积多晶硅薄膜且对沟槽底部多晶硅膜进行刻蚀并在多晶硅薄膜上沉积nitride,再通过刻蚀沟槽nitride并在刻蚀掉nitride的多晶硅上生长氧化层,然后通过去除剩余的nitride并在此基础上涨一层多晶硅以形成减小cgd的新的器件结构方法的方式,实现避免cgd过大、减慢器件开关速率以及降低器件损耗的技术效果。

技术特征:

1.一种提升沟槽型sic mosfet器件开关速度的方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的提升沟槽型sic mosfet器件开关速度的方法,其特征在于,所述多晶硅膜与nitride的厚度比例为1:1.67~1:1.5。

3.根据权利要求1所述的提升沟槽型sic mosfet器件开关速度的方法,其特征在于,所述sic外延层的型号可与sic晶圆相同或者不同,其中所述sic晶圆为晶向且为n型或者p型。

4.根据权利要求1所述的提升沟槽型sic mosfet器件开关速度的方法,其特征在于,所述s5中刻蚀沟槽中的nitride的方法为干法刻蚀。

5.根据权利要求1所述的提升沟槽型sic mosfet器件开关速度的方法,其特征在于,所述沟槽整体为u形,所述沟槽圆滑过渡至sic外延层。

6.权利要求1-5任一所述的提升沟槽型sic mosfet器件开关速度的方法在sic mosfet器件制造中的应用。

技术总结

本发明公开了一种提升沟槽型SICMOSFET器件开关速度的方法,属于半导体器件技术领域,能够通过在SIC外延层表面形成沟槽并在沟槽底部和侧壁生长栅极氧化膜,在形成的栅极氧化膜上沉积多晶硅薄膜且对沟槽底部多晶硅膜进行刻蚀并在多晶硅薄膜上沉积Nitride,再通过刻蚀沟槽Nitride并在刻蚀掉Nitride的多晶硅上生长氧化层,然后通过去除剩余的Nitride并在此基础上涨一层多晶硅以形成减小Cgd的新的器件结构方法的方式,实现避免Cgd过大、减慢器件开关速率以及降低器件损耗的技术效果。

技术研发人员:李鎔碩,马利奇,金秉燮,李旻姝,訾夏雪

受保护的技术使用者:浙江萃锦半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!