半导体器件的制作方法

本申请涉及半导体,具体涉及一种半导体器件。

背景技术:

1、超结金属-氧化物半导体场效应晶体管(metal-oxide-semiconductorfield-effect transistor, mosfet)是一种多子导电器件,具有开关速度快、开关损耗小以及频率特性好的优点。但是在较高压的状态下,电流的增大,通态损耗显著增大,导致超结mosfet器件在重载情况下,驱动效率不如绝缘栅双极型晶体管 (insulate gatebipolartransistor,igbt)高。

2、绝缘栅双极型晶体管 (insulate gate bipolartransistor,igbt)是一种双极型导电器件,具有mosfet输入阻抗高、控制功率小以及驱动电路简单的优点。但igbt在轻载情况下,驱动效率不如超结mosfet高。

3、目前,为了同时获得超结mosfet芯片和igbt芯片的优点,通常将超结mosfet和igbt并联封装形成新的器件结构,但因超结mosfet芯片和igbt芯片集成在一起,会引入新的寄生电容和电感,即出现相互干扰的情况,从而导致器件的性能不佳。

技术实现思路

1、鉴于此,本申请提供一种半导体器件,以解决现有器件中出现干扰的问题。

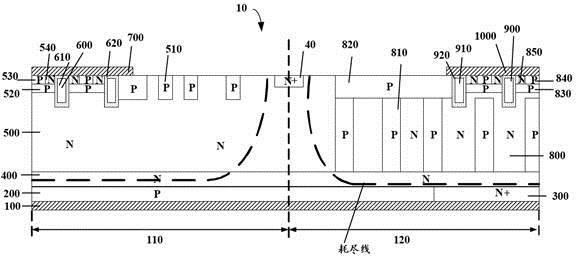

2、本申请提供一种半导体器件,包括:

3、金属集电极,具有第一区域以及位于所述第一区域一侧的第二区域;

4、p型集电部和n型漏区部,同层设置于所述金属集电极上,所述p型集电部位于所述第一区域以及所述第二区域,所述n型漏区部位于所述第二区域;

5、n型缓冲层,设置于所述p型集电部以及所述n型漏区部上;

6、n型漂移部和超结n型漂移部,同层设置于所述n型缓冲层上,且所述n型漂移部位于所述第一区域,所述超结n型漂移部位于所述第二区域;

7、第一p型保护部、第一p型部以及第一n型发射部,设置于所述n型漂移部中,所述第一p型保护部位于所述n型漂移部远离所述金属集电极的区域中;

8、超结p型柱部、第二p型保护部以及第二n型发射部,设置于所述超结n型漂移部中,所述第二p型保护部位于所述超结n型漂移部远离所述金属集电极的区域中;

9、第一栅极结构和第一发射电极,位于所述第一区域;

10、第二栅极结构和第二发射电极,位于所述第二区域;以及

11、n型截止部,设置于所述n型漂移部和所述超结n型漂移部中的至少一者,且位于所述第一p型保护部与第二p型保护部之间。

12、其中,所述n型截止部的厚度与所述n型漂移部或所述超结n型漂移部的厚度相同。

13、其中,所述第二p型保护部靠近所述n型漂移部的一端与所述p型集电部远离所述n型漂移部的一端重叠。

14、其中,所述第二p型保护部远离所述n型漂移部的一端到所述p型集电部远离所述n型漂移部的一端之间的距离为0-5微米。

15、其中,所述n型漂移部和所述n型缓冲层的厚度之和与所述n型截止部的厚度相等。

16、其中,所述n型截止部具有多个,每两相邻的所述n型截止部间隔设置,且自所述n型漂移部朝向所述的金属集电极的方向上,多个所述n型截止部重叠设置。

17、其中,所述第二p型保护部位于所述超结p型柱部远离所述金属集电极的一侧,且位于所述第二n型发射部靠近所述n型漂移部的一侧,所述第一p型保护部位于所述第一p型部以及所述第一n型发射部靠近超结n型漂移部的一侧,所述超结p型柱部的高度与所述p型阻挡部的高度相同。

18、其中,所述第一栅极结构位于所述n型漂移部中,所述第一p型部以及所述第一n型发射部均与所述第一栅极结构接触设置,所述第一发射电极设置于所述第一栅极结构远离所述金属集电极的一侧。

19、其中,所述第二栅极结构设置于所述超结n型漂移部中,所述第二p型保护部设置于所述第二栅极结构靠近所述n型漂移部的一侧,所述第二n型发射部与所述第二栅极结构接触设置,所述第二发射电极设置于所述第二栅极结构远离所述金属集电极的一侧。

20、其中,所述第一栅极结构位于所述n型漂移部远离所述金属集电极的一侧,所述第一发射电极覆盖所述第一栅极结构;所述第二栅极结构位于所述超结n型漂移部远离所述金属集电极的一侧,所述第二发射电极覆盖所述第二栅极结构。

21、本申请提供一种半导体器件,将p型集电部不仅设置于第一区域,而且还设置于第二区域,使得igbt沟槽元胞区到n型漏区部的路径足够长,从而避免igbt导通过程中,出现负阻现象。在本申请中,通过在远离金属集电极一侧的n型漂移部和/或超结n型漂移部设置n型截止部,且n型截止部设置于第一p型保护部与第二p型保护部之间,使得igbt和超结mosfet处于阻断状态时,位于第一区域的igbt在n型截止部处,电场截止,而位于第二区域的超结mosfet在n型截止部处,电场截止,从而避免超结mosfet与igbt之间出现相互干扰,从而提高器件的性能。

22、在本申请中,通过在超结mosfet与igbt之间设置n型截止部,使得超结mosfet与igbt两颗芯片在并联封装时,无需留出一定距离,以减小超结mosfet与igbt集成的在一起时,所占用的面积。

23、在本申请中,因在超结mosfet与igbt之间设置n型截止部,使得超结mosfet与igbt之间的连接无需打线连接,避免打线引入新的寄生电容和电感,从而保证了器件的性能。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,所述n型截止部的厚度与所述n型漂移部或所述超结n型漂移部的厚度相同。

3.根据权利要求1所述的半导体器件,其特征在于,所述第二p型保护部靠近所述n型漂移部的一端与所述p型集电部远离所述n型漂移部的一端重叠。

4.根据权利要求1所述的半导体器件,其特征在于,所述第二p型保护部远离所述n型漂移部的一端到所述p型集电部远离所述n型漂移部的一端之间的距离为0-5微米。

5.根据权利要求1所述的半导体器件,其特征在于,所述n型漂移部和所述n型缓冲层的厚度之和与所述n型截止部的厚度相等。

6.根据权利要求1的半导体器件,其特征在于,所述n型截止部具有多个,每两相邻的所述n型截止部间隔设置,且自所述n型漂移部朝向所述的金属集电极的方向上,多个所述n型截止部重叠设置。

7.根据权利要求1-6任一项所述的半导体器件,其特征在于,所述第二p型保护部位于所述超结p型柱部远离所述金属集电极的一侧,且位于所述第二n型发射部靠近所述n型漂移部的一侧,所述第一p型保护部位于所述第一p型部以及所述第一n型发射部靠近超结n型漂移部的一侧,所述超结p型柱部的高度与所述p型阻挡部的高度相同。

8.根据权利要求7所述的半导体器件,其特征在于,所述第一栅极结构位于所述n型漂移部中,所述第一p型部以及所述第一n型发射部均与所述第一栅极结构接触设置,所述第一发射电极设置于所述第一栅极结构远离所述金属集电极的一侧。

9.根据权利要求7所述的半导体器件,其特征在于,所述第二栅极结构设置于所述超结n型漂移部中,所述第二p型保护部设置于所述第二栅极结构靠近所述n型漂移部的一侧,所述第二n型发射部与所述第二栅极结构接触设置,所述第二发射电极设置于所述第二栅极结构远离所述金属集电极的一侧。

10.根据权利要求7所述的半导体器件,其特征在于,所述第一栅极结构位于所述n型漂移部远离所述金属集电极的一侧,所述第一发射电极覆盖所述第一栅极结构;所述第二栅极结构位于所述超结n型漂移部远离所述金属集电极的一侧,所述第二发射电极覆盖所述第二栅极结构。

技术总结

本申请提供一种半导体器件,包括:金属集电极具有第一区域以及位于第一区域一侧的第二区域;P型集电部和N型漏区部同层设置于金属集电极上,P型集电部位于第一区域以及第二区域,N型漏区部位于第二区域;N型漂移部和超结N型漂移部同层设置于P型集电部和N型漏区部上,且分别位于第一区域以及第二区域;第一P型保护部设置于N型漂移部中;超结P型柱部以及第二P型保护部设置于超结N型漂移部中,第二P型保护部位于超结N型漂移部远离金属集电极的区域中;第一栅极结构和第一发射电极位于第一区域;第二栅极结构和第二发射电极位于第二区域;N型截止部设置于第一P型保护部与第二P型保护部之间,以避免器件中出现干扰。

技术研发人员:李伟聪,陈钱,陈银

受保护的技术使用者:深圳市威兆半导体股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!