芯片晶圆键合结构及键合方法与流程

本发明涉及半导体领域,尤其涉及一种芯片晶圆键合结构及键合方法。

背景技术:

1、在半导体工艺中,要将若干个芯片键合至某一晶圆上的工艺越来越常见。图1所示为现有技术中的芯片的示意图。图2为现有技术中芯片键合至晶圆的位置示意图。如图1~图2所示,将三个芯片11、12、13键合至晶圆21的区域210内,具体地,将芯片11键合至区域a,将芯片12键合至区域b,将芯片13键合至区域c。现有技术中的键合方法是通过芯片上的对准标记10与晶圆上的对准标记20对准后,将芯片键合至晶圆。然后,每键合一芯片,都需要做一次对准,生产效率低。

2、因此,如何提高芯片晶圆键合效率,是目前需要解决的问题。

技术实现思路

1、本发明所要解决的技术问题是如何提高芯片与晶圆键合效率,提供一种芯片晶圆键合结构及键合方法。

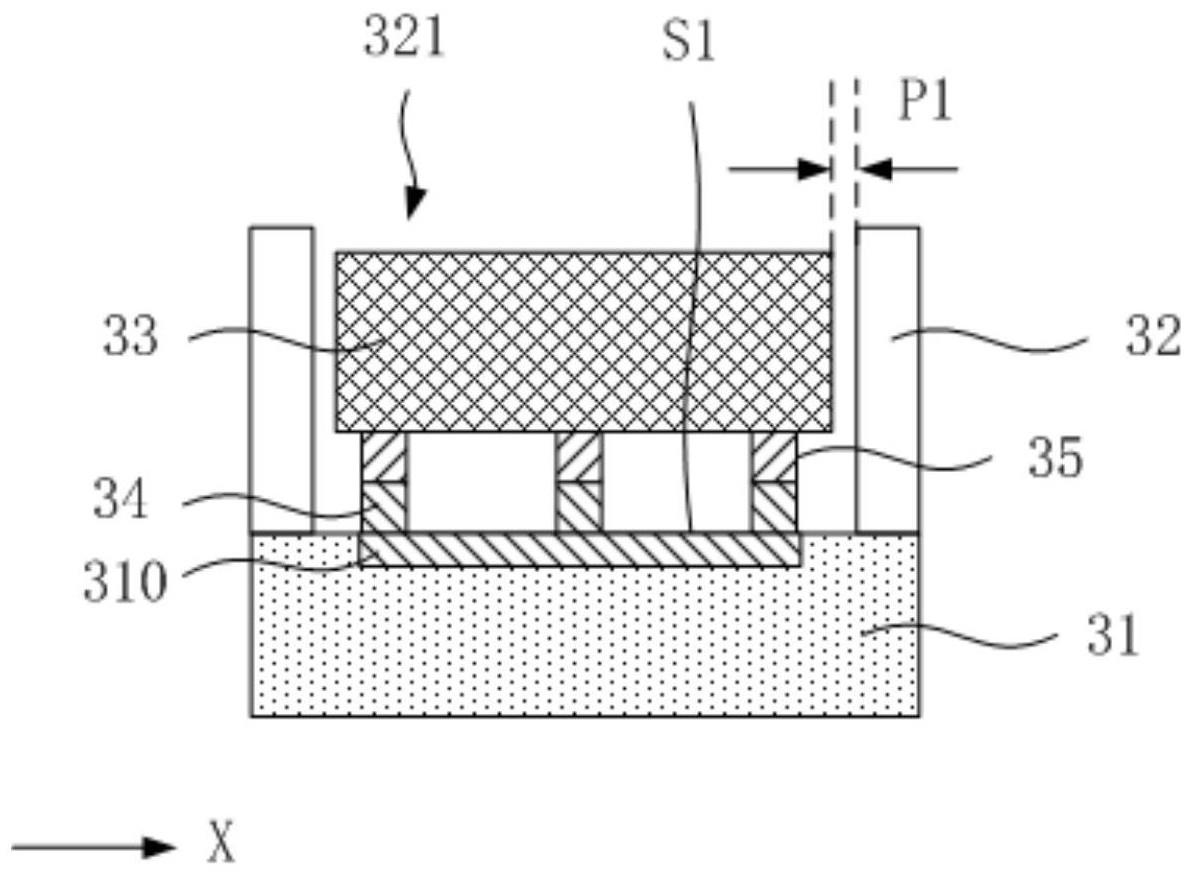

2、为了解决上述问题,本发明提供了一种芯片晶圆键合结构,包括:基底晶圆,具有第一表面,在所述第一表面设置有第一键合柱;键合层,位于所述基底晶圆的第一表面,所述键合层包括至少一键合槽,所述第一键合柱位于所述键合槽底部;至少一芯片,位于所述键合槽内,所述芯片朝向所述基底晶圆的表面具有第二键合柱,所述第一键合柱与所述第二键合柱键合连接。

3、为了解决上述问题,本发明提供了一种芯片晶圆键合方法,包括如下步骤:提供一基底晶圆与一芯片,所述基底晶圆具有第一表面,在所述第一表面设置有第一键合柱,所述芯片的一表面具有第二键合柱;在所述基底晶圆的第一表面形成键合层;在所述键合层形成至少一键合槽,所述键合槽底部暴露出所述第一键合柱;将所述芯片置于所述键合槽中,并将所述第一键合柱与所述第二键合柱键合连接,以形成芯片晶圆键合结构。

4、上述技术方案通过在所述基底晶圆表面设置所述键合层及键合槽,在执行芯片键合到晶圆上的键合操作时利用键合槽的限位来确定芯片的放置位置,无需在执行键合操作之前利用芯片及基底晶圆上的对准标记进行对准,大大提高了键合效率。

5、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本发明。对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为授权说明书的一部分。

技术特征:

1.一种芯片晶圆键合结构,其特征在于,包括:

2.根据权利要求1所述的结构,其特征在于,在平行于所述键合层表面的方向,所述芯片与所述键合槽侧壁具有空隙。

3.根据权利要求1所述的结构,其特征在于,所述基底晶圆的第一表面侧设置有电路层,所述第一键合柱与所述电路层电连接。

4.根据权利要求1所述的结构,其特征在于,所述基底晶圆具有与所述第一表面相对设置的第二表面,所述基底晶圆的第二表面侧设置有电路层,且所述第二表面设置有第三键合柱,所述第三键合柱与所述电路层电连接,且所述第一键合柱与所述第三键合柱通过键合电路连接。

5.根据权利要求4所述的结构,其特征在于,所述键合电路包括:

6.根据权利要求5所述的结构,其特征在于,还包括:

7.一种芯片晶圆键合方法,其特征在于,包括如下步骤:

8.根据权利要求7所述的方法,其特征在于,在平行于所述键合层表面的方向,所述芯片与所述键合槽侧壁具有空隙。

9.根据权利要求7所述的方法,其特征在于,所述基底晶圆的第一表面侧设置有电路层,所述第一键合柱与所述电路层电连接。

10.根据权利要求7所述的方法,其特征在于,所述基底晶圆具有与所述第一表面相对设置的第二表面,所述基底晶圆的第二表面侧设置有电路层,且所述第二表面设置有第三键合柱,所述第三键合柱与所述电路层电连接;

11.根据权利要求10所述的方法,其特征在于,形成第一连接层及第二连接层的步骤包括:

技术总结

本发明提供一种芯片晶圆键合结构及键合方法。所述芯片晶圆键合结构包括:基底晶圆,具有第一表面,在所述第一表面设置有第一键合柱;键合层,位于所述基底晶圆的第一表面,所述键合层包括至少一键合槽,所述第一键合柱位于所述键合槽底部;至少一芯片,位于所述键合槽内,所述芯片朝向所述基底晶圆的表面具有第二键合柱,所述第一键合柱与所述第二键合柱键合连接。上述技术方案通过设置所述键合层及键合槽,在晶圆键合时无需对准晶圆标记,仅需将所述芯片放置于所述键合槽中,并在所述基底晶圆及所述芯片的表面设置所述第一键合柱及所述第二键合柱,通过所述第一键合柱及所述第二键合柱完成所述基底晶圆及所述芯片的键合,提高键合效率。

技术研发人员:蓝天,丁潇

受保护的技术使用者:芯盟科技有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!