一种沟槽型半导体功率器件及版图的制作方法

本申请涉及半导体,特别涉及一种沟槽型半导体功率器件及版图。

背景技术:

1、屏蔽栅沟槽功率器件(sgt mosfet)是一种新型的功率半导体器件,具有传统深沟槽mosfet的低导通损耗的优点,同时具有更加低的开关损耗。屏蔽栅沟槽功率器件(sgtmosfet)作为开关器件应用于新能源电动车、新型光伏发电、节能家电等领域的电机驱动系统、逆变器系统及电源管理系统,是核心功率控制部件。

2、屏蔽栅沟槽功率器件(sgt mosfet)和传统功率器件的主要区别是漂移区引入深沟槽结构,这种深沟槽结构通过横向电场来耗尽沟槽之间的漂移区,从而使得漂移区(深沟槽之间的区域)可以采用更高的掺杂浓度,进一步降低导通电阻,突破传统功率器件硅极限性能。

3、随着屏蔽栅沟槽功率器件(sgt mosfet)技术的发展,分离的屏蔽栅沟槽给设计提供了更大的灵活性。由于分离的屏蔽栅结构相对来讲尺寸比较大,如何通过布局(layout)来提高器件元胞密度(cell density)成为了一个首要解决的技术问题。

技术实现思路

1、鉴于上述问题,本申请的目的在于提供一种沟槽型半导体功率器件及版图,来提高器件元胞密度。

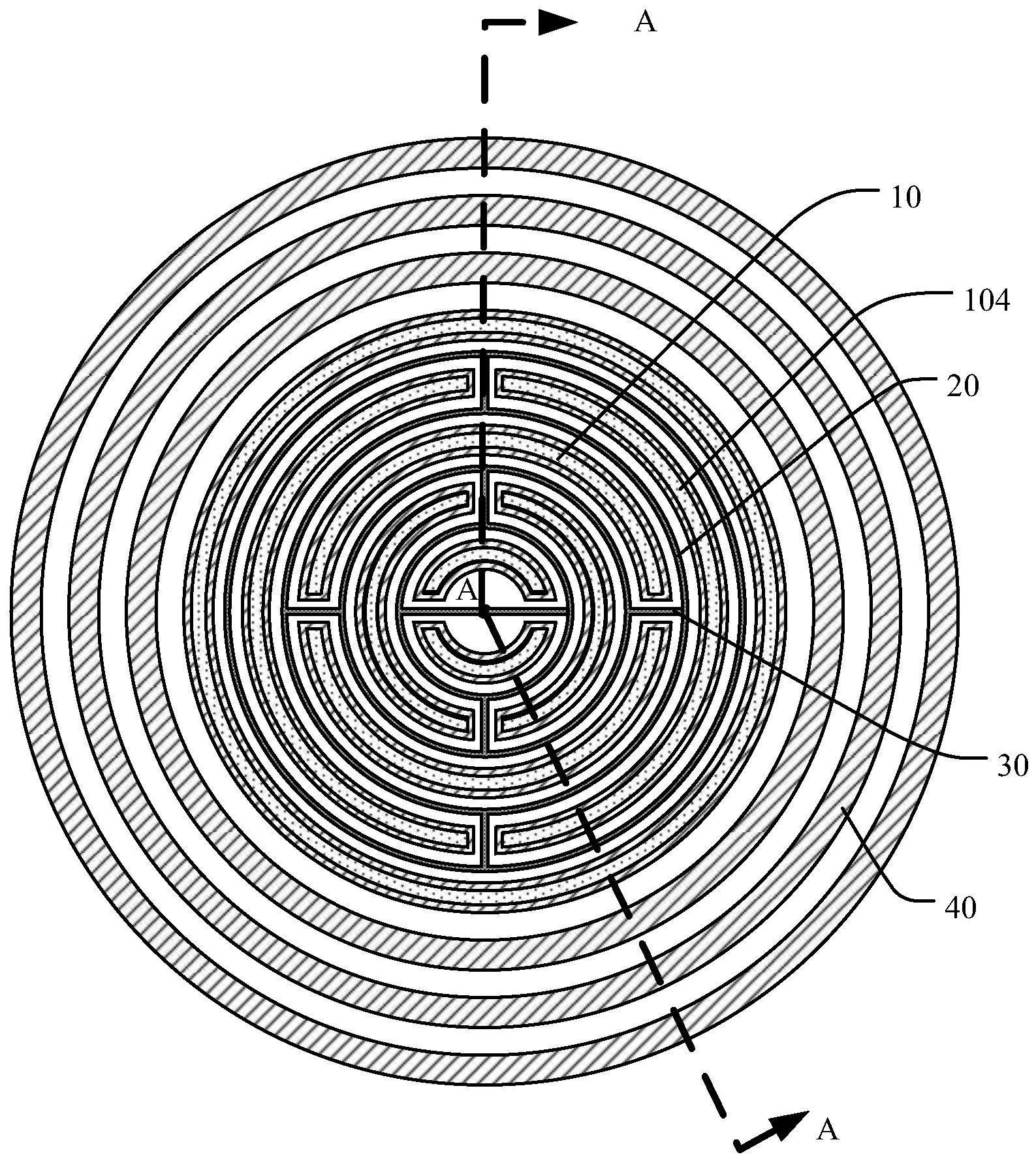

2、本申请第一方面提供一种沟槽型半导体功率器件,包括:第一掺杂类型的衬底;第一掺杂类型的外延层,位于所述衬底第一表面;源沟槽结构,位于所述外延层内部,所述源沟槽结构为圆环形;栅沟槽结构,位于所述外延层内部,所述栅沟槽结构为圆环形,所述源沟槽结构和所述栅沟槽结构相互分离且交替排列;桥沟槽结构,位于所述外延层内部,所述桥沟槽结构跨接于相邻的两个所述栅沟槽结构之间,穿过相邻的两个栅沟槽结构之间的源沟槽结构,将所述源沟槽结构切割成若干个源沟槽弧段,所述源沟槽弧段的端部与所述桥沟槽结构具有间隔;第二掺杂类型的基区,设置于相邻的源沟槽结构和栅沟槽结构之间的漂移区表层,所述第二掺杂类型和所述第一掺杂类型相反;第一掺杂类型的源区,设置于所述基区中;栅金属层,与所述栅沟槽结构连接;源金属层,与所述源沟槽结构和所述源区连接,所述源金属层和所述栅金属层相互绝缘隔离。

3、本申请第二方面提供一种沟槽型半导体功率器件版图,包括:源沟槽结构,所述源沟槽结构为圆环形;栅沟槽结构,所述栅沟槽结构为圆环形,所述源沟槽结构和所述栅沟槽结构相互分离且交替排列;桥沟槽结构,所述桥沟槽跨接于相邻的两个所述栅沟槽结构之间,穿过相邻的两个栅沟槽结构之间的源沟槽结构,将所述源沟槽结构切割成若干个源沟槽弧段,所述源沟槽弧段的端部与所述桥沟槽结构具有间隔。

技术特征:

1.一种沟槽型半导体功率器件,包括:

2.根据权利要求1所述的沟槽型半导体功率器件,其中,相邻的两个所述栅沟槽结构之间的所述桥沟槽结构设置为两个或两个以上。

3.根据权利要求1所述的沟槽型半导体功率器件,其中,相邻内外两圈中的所述桥沟槽结构为错位排列。

4.根据权利要求1所述的沟槽型半导体功率器件,其中,还包括外围沟槽结构,所述外围沟槽结构围绕所述源沟槽结构和栅沟槽结构,所述外围沟槽结构与所述源金属层连接。

5.根据权利要求1所述的沟槽型半导体功率器件,其中,所述源沟槽结构包括:从所述外延层的表面向其内部延伸的第一沟槽,覆盖所述第一沟槽的底部和侧壁的第一介质层,以及填充于所述第一沟槽的第一导体;

6.根据权利要求5所述的沟槽型半导体功率器件,其中,所述第二沟槽和所述第三沟槽的深度小于或等于所述第一沟槽的深度的三分之一。

7.根据权利要求5所述的沟槽型半导体功率器件,其中,所述第二沟槽与所述第三沟槽的深度相同,所述第二介质层与所述第三介质层的厚度相同,所述第二导体与所述第三导体相连。

8.根据权利要求5所述的沟槽型半导体功率器件,其中,所述第一介质层的厚度大于所述第二介质层与所述第三介质层的厚度。

9.根据权利要求1所述的沟槽型半导体功率器件,其中,位于所述第二沟槽底部的所述第二介质层的厚度大于位于所述第二沟槽侧壁的所述第二介质层的厚度,位于所述第三沟槽底部的所述第三介质层的厚度大于位于所述第三沟槽侧壁的所述第三介质层的厚度。

10.一种沟槽型半导体功率器件版图,包括:

11.根据权利要求10所述的沟槽型半导体功率器件版图,其中,在相邻的两个所述栅沟槽结构之间,设置两个或者两个以上的桥沟槽结构。

12.根据权利要求10所述的沟槽型半导体功率器件版图,其中,相邻内外两圈中的所述桥沟槽结构为错位排列。

13.根据权利要求10所述的沟槽型半导体功率器件版图,其中,还包括外围沟槽结构,所述外围沟槽结构围绕所述源沟槽结构和栅沟槽结ia23000116

14.根据权利要求10所述的沟槽型半导体功率器件版图,其中,所述源沟槽结构包括第一导体以及围绕所述第一导体的第一介质层;

技术总结

本申请公开了一种沟槽型半导体功率器件及版图,包括:第一掺杂类型的衬底;第一掺杂类型的外延层,位于衬底第一表面;源沟槽结构,位于外延层内部,为圆环形;栅沟槽结构,位于外延层内部,为圆环形,源沟槽结构和栅沟槽结构相互分离且交替排列;桥沟槽结构,位于外延层内部,桥沟槽结构跨接于相邻的两个栅沟槽结构之间,穿过相邻的两个栅沟槽结构之间的源沟槽结构,将源沟槽结构切割成若干个源沟槽弧段,源沟槽弧段的端部与桥沟槽结构具有间隔;第二掺杂类型的基区,设置于相邻的源沟槽结构和栅沟槽结构之间;第一掺杂类型的源区,设置于基区中;栅金属层,与栅沟槽结构连接;源金属层,与源沟槽结构和源区连接,源金属层和栅金属层相互分离。

技术研发人员:刘坚,蔡金勇

受保护的技术使用者:杭州芯迈半导体技术有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!