集成电路封装框架的制作方法

本申请涉及集成电路,特别涉及集成电路封装技术。

背景技术:

1、本部分旨在为权利要求书中陈述的本申请的实施方式提供背景或上下文。此处的描述不因为包括在本部分中就承认是已被公开的现有技术。

2、在半导体封装领域,特别是针对高集成度和高性能的芯片,小尺寸和高密度的封装技术已经成为一种普遍应用的解决方案。例如,ssop(shrink small-outline package)作为一种常见的封装类型,在电子设备不断追求小型化的趋势下获得了广泛应用。ssop封装具有小尺寸和紧凑的引脚间距,满足了电子设备小型化的需求,并且提供了高引脚密度,支持了更复杂的功能集成。然而,尽管ssop封装在满足许多应用需求方面具有显著优势,但也存在一些局限性和问题需要解决。

3、现有的ssop封装在面对功率较大的芯片时无法有效解决散热问题。随着芯片性能的提升,功耗也相应增加,这导致芯片产生更多的热量。然而,现有的ssop封装在散热设计方面存在一定的局限性,散热片的面积有限,无法有效地排除热量,可能会导致芯片的温度过高,进而影响芯片的稳定性和寿命。

技术实现思路

1、本申请的目的在于提供一种集成电路封装框架,在同样规格的封装中可以提供更好的散热性能。

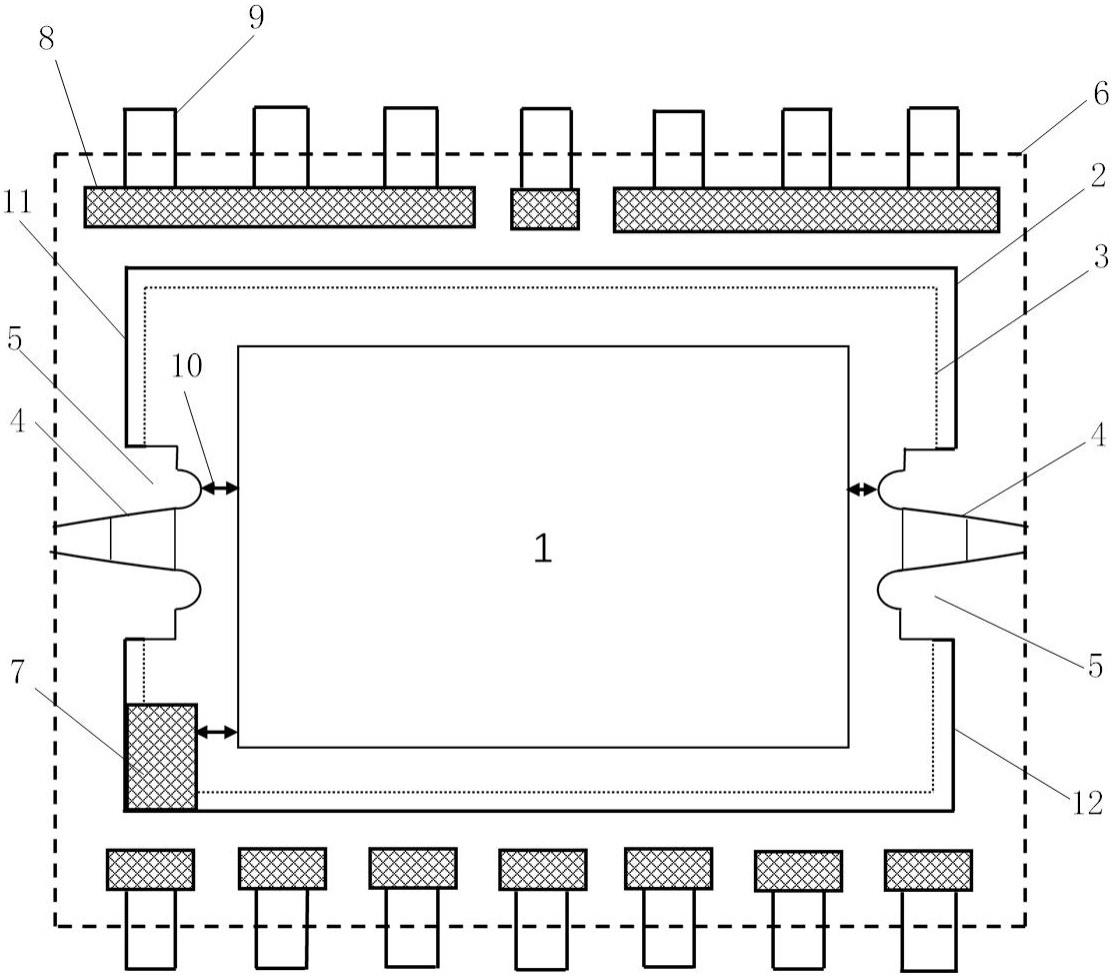

2、本申请公开了一种集成电路封装框架,包括:片状的基岛,芯片,散热片和两个连接筋;

3、所述基岛的第一面与所述芯片贴合,所述散热片配置在所述基岛的第二面,所述芯片和所述散热片的覆盖范围均在所述基岛的覆盖范围之内;

4、所述基岛总体上呈矩形轮廓,该矩形轮廓包括相对的第一边和第二边,第一边和第二边的中部各自形成向所述基岛中心凹陷的内凹结构,所述两个连接筋分别在两个所述内凹结构内与所述基岛连接,且所述两个连接筋与所述基岛的两个连接点之间的距离小于第一边和第二边之间的距离;

5、所述基岛的第一面的一个角设置有局部电镀区域,所述局部电镀区域与所述芯片之间以预定的安全距离隔开,所述局部电镀区域的覆盖范围有部分与所述散热片的覆盖范围重合,所述局部电镀区域的打线位置位于重合部分。

6、在一个优选例中,所述框架包括m个引脚,其中至少n个相邻引脚之间通过导电的内部打线区域连接在一起,m>n>1,所述内部打线区域通过多条金属线与所述芯片电连接,其中至少一条金属线在所述内部打线区域中的打线位置位于两个相邻引脚之间。

7、在一个优选例中,所述内凹结构呈半圆弧形状,所述连接筋与所述基岛的连接点在该半圆弧形状最靠近所述基岛中心的位置。

8、在一个优选例中,所述内凹结构呈矩形,其中所述连接筋与所述基岛的连接点在所述矩形靠近所述基岛中心的一条边上。

9、在一个优选例中,所述局部电镀区域是镀银区。

10、在一个优选例中,所述局部电镀区域接地。

11、在一个优选例中,所述局部电镀区域接电源。

12、在一个优选例中,在一个所述基岛上封装一个芯片。

13、在一个优选例中,在一个所述基岛上封装多个芯片。

14、在一个优选例中,所述封装框架为塑封封装框架。

15、在本申请的实施方式中,通过在矩形基岛的一对相对边上分别构建内凹结构,使得基岛在这个方向上的尺寸可以超过与两个连接筋的两个连接点之间的距离,从而使得基岛可以做得更大,相应地可以布置更大散热片,从而在同样规则的封装中可以提高散热性能。此外,还可以有更大的可容纳芯片的区域。因为局部电镀区域和芯片之间要有一定的安全距离,所以局部电镀区域也限制了芯片的尺寸。当基岛因为内凹结构的存在而可以做得更大时,局部电镀区域也可以布置在基岛与连接筋的连接点之外的区域,从而减小了对芯片尺寸的限制,可以有更大的可容纳芯片的区域。局部电镀区域的打线位置位于局部电镀区域与散热片重合的区域,可以避免脱线风险。

16、因为内凹结构的存在,使得基岛的四个角可以超越原本连接筋的限制向外延伸,这使得在基岛一个角上的局部电镀区域的位置也向外移动。因为局部电镀区域通常和芯片有一定的安全间隔,所以局部电镀区域的外移也留出更多的空间给芯片,从而可以布置更大芯片或更多芯片。

17、进一步地,通过将多个相邻引脚用导电材料连接在一起,形成一整块内部打线区域,该区域的大小显著大于原来这些相邻引脚的打线区域之和,这样可以在原来不能打线的位置(例如两个引脚之间)打线,从而能够在芯片和内部打线区域之间打更多的金属线,这些并联的金属线可以大大减少打线电阻和引脚电阻。

18、上述

技术实现要素:

中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均应该视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征a+b+c,在另一个例子中公开了特征a+b+d+e,而特征c和d是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征e技术上可以与特征c相组合,则,a+b+c+d的方案因技术不可行而应当不被视为已经记载,而a+b+c+e的方案应当视为已经被记载。

技术特征:

1.一种集成电路封装框架,其特征在于,包括:片状的基岛,芯片,散热片和两个连接筋;

2.如权利要求1所述的集成电路封装框架,其特征在于,所述框架包括m个引脚,其中至少n个相邻引脚之间通过导电的内部打线区域连接在一起,m>n>1,所述内部打线区域通过多条金属线与所述芯片电连接,其中至少一条金属线在所述内部打线区域中的打线位置位于两个相邻引脚之间。

3.如权利要求1所述的集成电路封装框架,其特征在于,所述内凹结构呈半圆弧形状,所述连接筋与所述基岛的连接点在该半圆弧形状最靠近所述基岛中心的位置。

4.如权利要求1所述的集成电路封装框架,其特征在于,所述内凹结构呈矩形,其中所述连接筋与所述基岛的连接点在所述矩形靠近所述基岛中心的一条边上。

5.如权利要求1所述的集成电路封装框架,其特征在于,所述局部电镀区域是镀银区。

6.如权利要求1所述的集成电路封装框架,其特征在于,所述局部电镀区域接地。

7.如权利要求1所述的集成电路封装框架,其特征在于,所述局部电镀区域接电源。

8.如权利要求1所述的集成电路封装框架,其特征在于,在一个所述基岛上封装一个芯片。

9.如权利要求1所述的集成电路封装框架,其特征在于,在一个所述基岛上封装多个芯片。

10.如权利要求1所述的集成电路封装框架,其特征在于,所述封装框架为塑封封装框架。

技术总结

本申请涉及集成电路,公开了一种集成电路封装框架,在同样规格的封装中可以提供更好的散热性能。该封装框架包括:片状的基岛,芯片,散热片和两个连接筋;基岛的第一面与芯片贴合,散热片配置在基岛的第二面,芯片和散热片的覆盖范围均在基岛的覆盖范围之内;基岛总体上呈矩形轮廓,该矩形轮廓两条相对边的中部各自形成向基岛中心凹陷的内凹结构,两个连接筋分别在两个内凹结构内与基岛连接;基岛的第一面的一个角设置有局部电镀区域,局部电镀区域与芯片之间以预定的安全距离隔开,局部电镀区域的覆盖范围有部分与散热片的覆盖范围重合,局部电镀区域的打线位置位于重合部分。

技术研发人员:王玲,夏晨,张泽飞

受保护的技术使用者:上海类比半导体技术有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!