一种隧穿场效应晶体管的制备方法

本发明属于微纳电子学,具体涉及一种隧穿场效应晶体管的制备方法。

背景技术:

1、随着半导体技术的不断进步,器件尺寸不断减小,电路性能不断提升,芯片功耗密度也急剧增大,低功耗已经成为一个重要设计方向。从器件层面上,降低电源电压可以有效降低电路功耗,然而为了保持足够的驱动能力,mosfet器件阈值电压也必须下降,带来关态电流和静态功耗的抬升。常规隧穿场效应晶体管(tfet)采用带带隧穿的电流机制,其位于高能带尾的载流子被有效截断,能够获得低于60mv/dec的超陡亚阈值斜率,提供了较高的电流开关比,为低压工作提供了可能,被认为是一种很有希望替代mosfet的超陡器件。

2、根据已有文献报道的实验结果可知,相比于iii-v族材料的tfet和锗基的tfet,硅基tfet的关态电流最低,这是因为硅的带隙较宽。因此,硅基tfet更有利于降低芯片的静态功耗。此外,硅基tfet和现有硅基cmos的工艺兼容性最好,有利于降低芯片成本。

3、然而,正因为硅的带隙较宽,导致硅基tfet器件的开启电压较高,进而使得硅基tfet电路的工作电压vdd较高,即,tfet器件的关态电流和工作电压优化之间存在折中关系。进一步地,面向大规模tfet-cmos混合集成电路应用,tfet的栅叠层需要和现有硅基cmos工艺兼容,有可能出现ntfet的开启电压为负值或者ptfet的开启电压为正值的情况,使得tfet的关态电流增大。

4、因此,如何在保证硅基tfet器件的静态功耗优势的同时,将硅基tfet器件的开启电压向0v方向调整,进而实际降低硅基tfet电路的工作电压和动态功耗,成为了将硅基tfet实际用于低功耗电路需要迫切解决的问题,需要结合与硅基cmos的工艺兼容性思考解决方案。

技术实现思路

1、本发明的目的在于提出一种tfet器件的制备方法,可以实现对tfet器件工作电压的调整,同时保证tfet器件低关态电流的优势。。

2、本发明的技术方案如下,

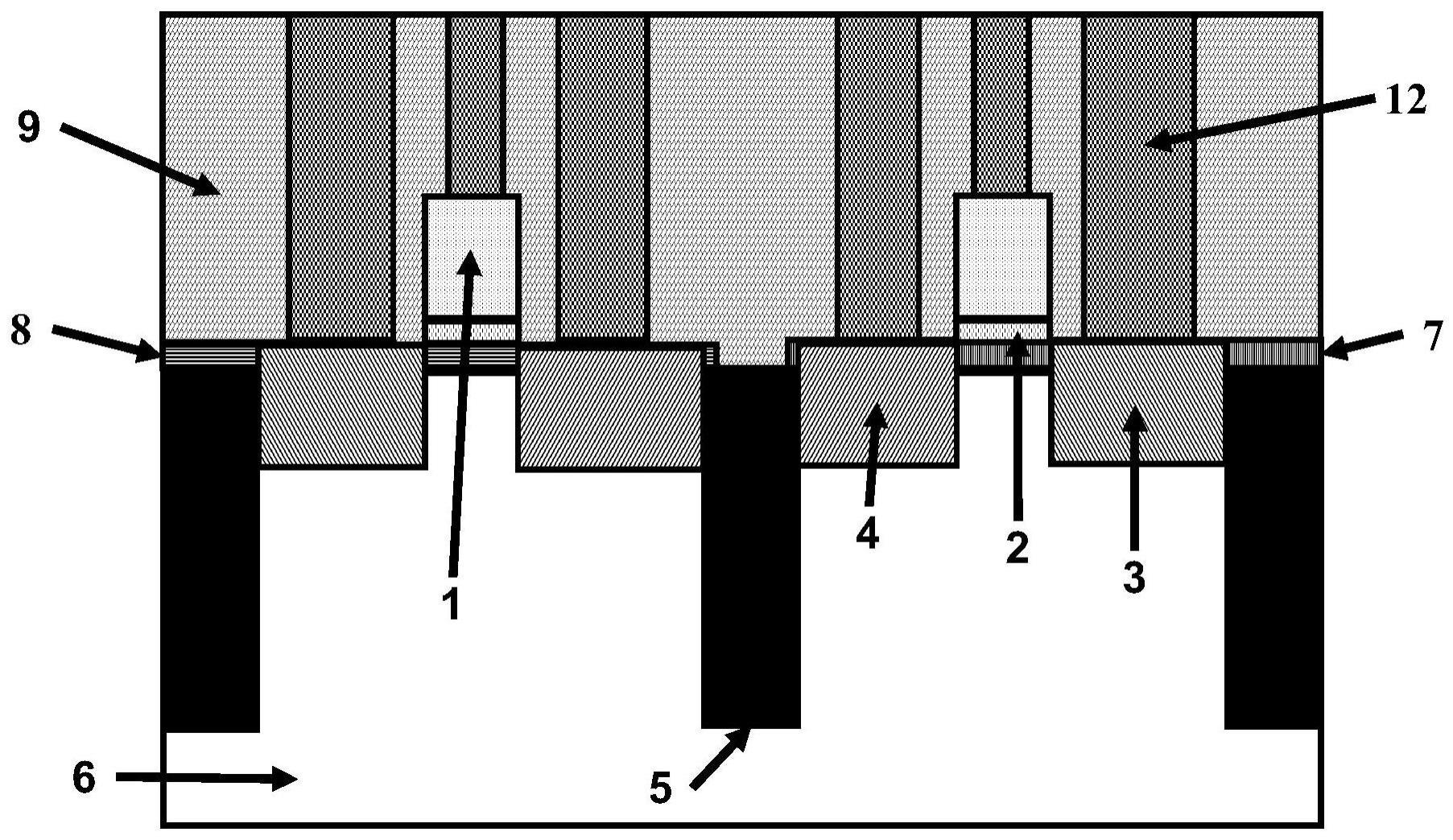

3、一种隧穿场效应晶体管的制备方法,其特征在于,在制备隧穿场效应晶体管过程中,在衬底表面和栅叠层之间,采用外延的方式制备一个具有与漏区或源区同样掺杂类型的中等浓度硅材料作为沟道区,包括以下步骤:

4、步骤1:提供一个具有n型掺杂类型或者p型掺杂类型的轻掺杂硅作为衬底区;

5、步骤2:做浅槽隔离(sti),具体的方法是在有源区以外的地方以各向异性的方式刻蚀硅;再在有源区以外的地方以各向异性的方式沉积氧化层;

6、步骤3:做硬掩模定义n型tfet器件的有源区,具体的方法是全片淀积介电材料薄膜,通过光刻的方式定义n型tfet器件的有源区,再将暴露出的介电材料刻蚀掉,形成硬掩模;

7、步骤4:制备n型tfet器件的沟道区,具体的方法是全片外延中等掺杂浓度的硅薄层,再通过湿法刻蚀的方式去除掉介电材料硬掩模以及其上的硅薄层;

8、步骤5:做硬掩模定义p型tfet器件的有源区,具体的方法是全片淀积介电材料薄膜,通过光刻的方式定义p型tfet器件的有源区,再将暴露出的介电材料刻蚀掉,形成硬掩模;

9、步骤6:制备p型tfet器件的沟道区,具体的方法是全片外延中等掺杂浓度的硅薄层,再通过湿法刻蚀的方式去除掉介电材料硬掩模以及其上的硅薄层;

10、步骤7:全片淀积形成栅绝缘层和栅导电层;

11、步骤8:用光刻和刻蚀的方法图形化栅叠层区;

12、步骤9:光刻暴露出tfet的p型重掺杂区的窗口,并通过离子注入的方式形成p型重掺杂区,离子注入结束以后去胶;

13、步骤10:光刻暴露出tfet的n型重掺杂区的窗口,并通过离子注入的方式形成n型重掺杂区,离子注入结束以后去胶;

14、步骤11:退火激活前几步工艺中注入的杂质;

15、步骤12:淀积形成绝缘层,然后掩膜曝光刻蚀出源区、漏区以及栅叠层区上的源电极通孔、漏电极通孔和栅电极通孔;

16、步骤13:用电极的导电材料填充源电极通孔、漏电极通孔和栅电极通孔形成源电极、漏电极和栅电极。

17、进一步,上述步骤中的n型掺杂的杂质可以是磷、砷或者其他五价元素及其化合物。p型掺杂的杂质可以是硼、氟化硼或者其他三价元素及其化合物。

18、步骤2中sti的厚度应在200nm-1000nm之间。

19、步骤3和步骤5中用于制备硬掩模的介电材料可以是二氧化硅、氮化硅等介电材料。

20、步骤4和步骤6中外延硅薄膜的厚度为1nm-20nm之间,掺杂浓度为1e16cm-3-1e19cm-3之间。外延硅薄膜的掺杂类型可以是n型,也可以是p型,需要根据具体需求进行设计。如果外延硅薄膜的掺杂类型与对应tfet器件的源区掺杂类型相同,那么可以增加tfet器件的工作电压。如果外延硅薄膜的掺杂类型与对应tfet器件的漏区掺杂类型相同,则可以减小tfet器件的工作电压。

21、步骤7中的栅绝缘层可以是二氧化硅、氧化铪、氧化镧等介电材料,栅导电层可以是重掺杂多晶硅、氮化钛等导电材料。

22、步骤11中的绝缘层可以是氧化硅、氮化硅或者是其他绝缘材料的一种。

23、步骤12中的电极材料可以是铝、铜、钨等金属中的一种。

24、具体技术效果如下:

25、以n型tfet器件为例,当沟道表面的能带在栅压的作用下达到强反型以后,再在漏压的作用下,将沟道表面能带的导带底降低到源区能带的价带顶以下,ntfet的源区隧穿窗口打开,器件处于开启状态,此时器件的栅压被定义为开启电压von。因此,当漏区电压为电路工作电压vdd时,ntfet器件的开启电压von是沟道表面能带达到强反型时的栅压。ptfet器件的开启电压同理也是类似的定义。那么,对于轻掺杂衬底的tfet器件来说,沟道表面的费米能级原本在禁带中心附近,发生强反型时,沟道表面的费米能级位于导带底(ptfet的沟道表面能带的费米能级位于价带顶)附近,对应的沟道表面能带弯曲量为eg/2。所以tfet器件的开启电压与沟道材料的带隙宽度成正比。因此若外延硅的掺杂类型与漏区相同,则可以降低tfet器件的开启电压。若外延硅的掺杂类型与源区相同,则可以增大tfet器件的开启电压。同时,沟道区的厚度较小,器件的衬底区主体仍然是轻掺杂的高阻硅,因此隧穿场效应晶体管的低关态电流优势得以保持。

26、本发明的优点在于:

27、一、本发明提出的工艺制备方法可以降低tfet器件的涨落

28、本发明中,沟道区的中等掺杂浓度硅材料采用外延的方式制备,相比于传统的离子注入的工艺方式,可以降低器件的涨落。

29、二、本发明提出的制备方法可以与cmos工艺兼容,可以用于未来大规模低功耗集成电路的集成。

技术特征:

1.一种隧穿场效应晶体管的制备方法,其特征在于,在制备隧穿场效应晶体管过程中,在衬底表面和栅叠层之间,采用外延的方式制备一个具有与漏区或源区同样掺杂类型的中等浓度硅材料作为沟道区,具体步骤包括:

2.如权利要求1所述的隧穿场效应晶体管的制备方法,其特征在于,上述步骤中的n型掺杂的杂质是磷、砷或者其他五价元素及其化合物;p型掺杂的杂质是硼、氟化硼或者其他三价元素及其化合物。

3.如权利要求1所述的隧穿场效应晶体管的制备方法,其特征在于,步骤2中浅槽隔离sti的厚度在200nm-1000nm之间。

4.如权利要求1所述的隧穿场效应晶体管的制备方法,其特征在于,步骤3和步骤5中用于制备硬掩模的介电材料采用二氧化硅、氮化硅等介电材料。

5.如权利要求1所述的隧穿场效应晶体管的制备方法,其特征在于,步骤4和步骤6中外延硅薄膜的厚度为1nm-20nm之间,掺杂浓度为1e16cm-3-1e19cm-3之间。

6.如权利要求1所述的隧穿场效应晶体管的制备方法,其特征在于,步骤7中的栅绝缘层是二氧化硅、氧化铪、氧化镧等介电材料,栅导电层是重掺杂多晶硅、氮化钛等导电材料。

7.如权利要求1所述的隧穿场效应晶体管的制备方法,其特征在于,步骤11中的绝缘层是氧化硅、氮化硅或者是其他绝缘材料的一种。

8.如权利要求1所述的隧穿场效应晶体管的制备方法,其特征在于,步骤12中的电极材料是铝、铜、钨等金属中的一种。

技术总结

本发明提供了一种隧穿场效应晶体管的制备方法,属于微纳电子学技术领域。本发明在基本的隧穿场效应晶体管结构的基础上,采用外延方法在衬底表面和栅叠层之间制备了一个具有和漏区或源区同样掺杂类型的中等浓度硅材料作为沟道区,从而降低或增大了隧穿场效应晶体管用于沟道反型的栅电压,进而降低或增大了隧穿场效应晶体管的开启电压。同时,沟道区的厚度较小,器件的衬底区主体仍然是轻掺杂的高阻硅,因此隧穿场效应晶体管的低关态电流优势得以保持。本发明可以与CMOS工艺兼容,可以用于未来大规模低功耗集成电路的集成。

技术研发人员:黄芊芊,王凯枫,卜伟海,吴旭升,武咏琴,任烨,黄如

受保护的技术使用者:北京大学

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!