嵌入式闪存栅氧化层工艺集成方法与流程

本申请涉及半导体,具体涉及一种嵌入式闪存栅氧化层工艺集成方法。

背景技术:

1、嵌入式闪存(embedded flash,e-flash)是将闪存嵌入到cmos(complementarymetal-oxide-semiconductor transistor)上,形成soc(system on a chip)。常用嵌入式闪存的i/o(输入/输出)器件的工作电压为2.5v,core(核心)器件的工作电压为1.2v,因此需要两种厚度的栅氧化层。

2、形成两种厚度的栅氧化层的工艺包括如下步骤:先在衬底上生长i/o器件需要的厚氧化层,然后形成图案化的光刻胶层,露出core器件区域;通过刻蚀去除位于core器件区域的厚氧化层后,去除图案化的光刻胶层;最后在衬底上生长core器件需要的薄氧化层。分步形成i/o器件需要的厚栅氧化层和core器件需要的薄氧化层之后,完成栅极的制作。

3、嵌入式闪存中存在一类通过i/o器件的宽电压应用实现类似core器件功能的特殊产品,该产品栅氧化层仅有一种厚度,故其标准工艺(signal gate工艺)流程中去掉了上述工艺中的形成图案化的光刻胶层以及通过刻蚀去除位于core器件区域的厚氧化层后去除图案化的光刻胶层的步骤。但为了保证热预算(thermal budge和栅氧化层质量,仍然沿用了两步生长栅氧化层的方法。

4、上述现有的嵌入式闪存栅氧化层工艺需要分两步生长栅氧化层,两步生长栅氧化层之间至少增加一反应前清洗的工艺步骤,制造成本高,生产效率低。

技术实现思路

1、鉴于以上所述现有技术的缺点,本申请的目的在于提供一种嵌入式闪存栅氧化层工艺集成方法,用于解决现有技术中嵌入式闪存栅氧化层工艺制造成本高且生产效率低的问题。

2、为实现上述目的及其它相关目的,本申请提供一种嵌入式闪存栅氧化层工艺集成方法,用于形成位于i/o器件区的第一栅氧化层和位于核心器件区的第二栅氧化层,该方法包括:

3、提供一衬底,对衬底进行预清洗处理;

4、在衬底上一步同时形成厚度相同的第一栅氧化层和第二栅氧化层,以实现i/o器件区的宽电压应用;

5、在厚度相同的第一栅氧化层和第二栅氧化层上形成栅极材料层,然后在衬底上形成位于i/o器件区的第一栅极和位于核心器件区的第二栅极。

6、优选的,嵌入式闪存栅氧化层标准工艺通过两步形成栅氧化层的厚度分别为thk1和thk2,该第一栅氧化层和第二栅氧化层的厚度介于thk1和thk2之间。

7、优选的,该第一栅氧化层和第二栅氧化层的厚度与thk1的偏差不超过5埃。

8、优选的,嵌入式闪存栅氧化层标准工艺通过两步形成栅氧化层的温度分别为temp1和temp2,所述一步同时形成第一栅氧化层和第二栅氧化层时的温度与temp1相同,并且高于temp2。

9、优选的,衬底上形成有多个隔离部件。

10、优选的,隔离部件将衬底分成多个区域,所述区域包括i/o器件区和核心器件区。

11、优选的,第一栅极和第二栅极为多晶硅栅极或金属栅极。

12、如上所述,本申请提供的嵌入式闪存栅氧化层工艺集成方法,具有以下有益效果:相比现有的嵌入式闪存栅氧化层标准工艺,本申请提供的嵌入式闪存栅氧化层工艺集成方法节省一道反应前清洗、一道栅氧化层生长以及栅氧化层薄膜量测等工艺,可以实现嵌入式闪存产品栅氧化层生长及薄膜量测机台产能提高,达到降本增效的目的。

技术特征:

1.一种嵌入式闪存栅氧化层工艺集成方法,用于形成位于i/o器件区的第一栅氧化层和位于核心器件区的第二栅氧化层,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,嵌入式闪存栅氧化层标准工艺通过两步形成栅氧化层的厚度分别为thk1和thk2,所述第一栅氧化层和所述第二栅氧化层的厚度介于所述thk1和thk2之间。

3.根据权利要求2所述的方法,其特征在于,所述第一栅氧化层和所述第二栅氧化层的厚度与所述thk1的偏差不超过5埃。

4.根据权利要求1所述的方法,其特征在于,嵌入式闪存栅氧化层标准工艺通过两步形成栅氧化层的温度分别为temp1和temp2,所述一步同时形成所述第一栅氧化层和所述第二栅氧化层时的温度与所述temp1相同,并且高于所述temp2。

5.根据权利要求1所述的方法,其特征在于,所述衬底上形成有多个隔离部件。

6.根据权利要求5所述的方法,其特征在于,所述隔离部件将所述衬底分成多个区域,所述区域包括所述i/o器件区和所述核心器件区。

7.根据权利要求1所述的方法,其特征在于,所述第一栅极和所述第二栅极为多晶硅栅极或金属栅极。

技术总结

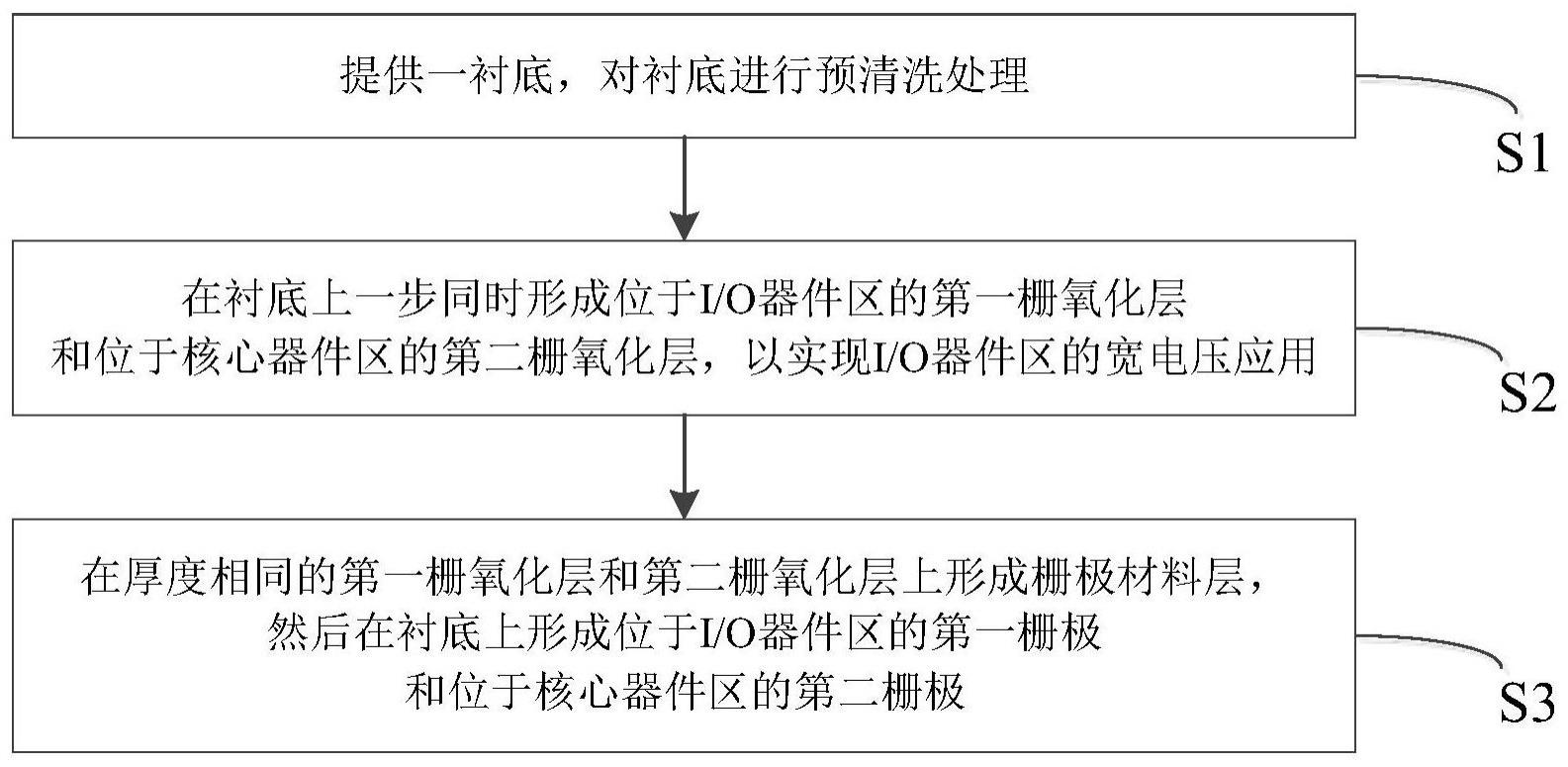

本申请提供一种嵌入式闪存栅氧化层工艺集成方法,包括:步骤S1,提供一衬底,对衬底进行预清洗处理;步骤S2,在衬底上一步同时形成位于I/O器件区的第一栅氧化层和位于核心器件区的第二栅氧化层,以实现I/O器件区的宽电压应用;步骤S3,在厚度相同的第一栅氧化层和第二栅氧化层上形成栅极材料层,然后在衬底上形成位于I/O器件区的第一栅极和位于核心器件区的第二栅极。相比现有的嵌入式闪存栅氧化层标准工艺,本申请提供的嵌入式闪存栅氧化层工艺集成方法节省一道反应前清洗、一道栅氧化层生长以及栅氧化层薄膜量测等工艺,可以实现嵌入式闪存产品栅氧化层生长及薄膜量测机台产能提高,达到降本增效的目的。

技术研发人员:翟海涛,赵鹏,齐瑞生,黄冠群

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!