一种半导体结构及其制作方法与流程

本发明属于半导体,特别涉及一种半导体结构及其制作方法。

背景技术:

1、在制备半导体结构时,为了提高半导体器件的性能。会在衬底上形成应力薄膜,并将应力薄膜中的应力转移至沟道中,从而提高电子迁移率。

2、但是,在一些半导体结构中,相邻的同类型的半导体器件共用一个掺杂区。共用掺杂区可减小半导体结构的体积,但是,相邻的同类型的半导体器件中沟道的应力会相互抑制,影响沟道中应力的效果,进而影响半导体结构的性能。

技术实现思路

1、本发明的目的在于提供一种半导体结构及其制作方法,通过本发明提供的半导体结构及其制作方法,可避免应力的相互积压,并修复衬底损伤,提高半导体结构的性能。

2、为解决上述技术问题,本发明是通过以下技术方案实现的。

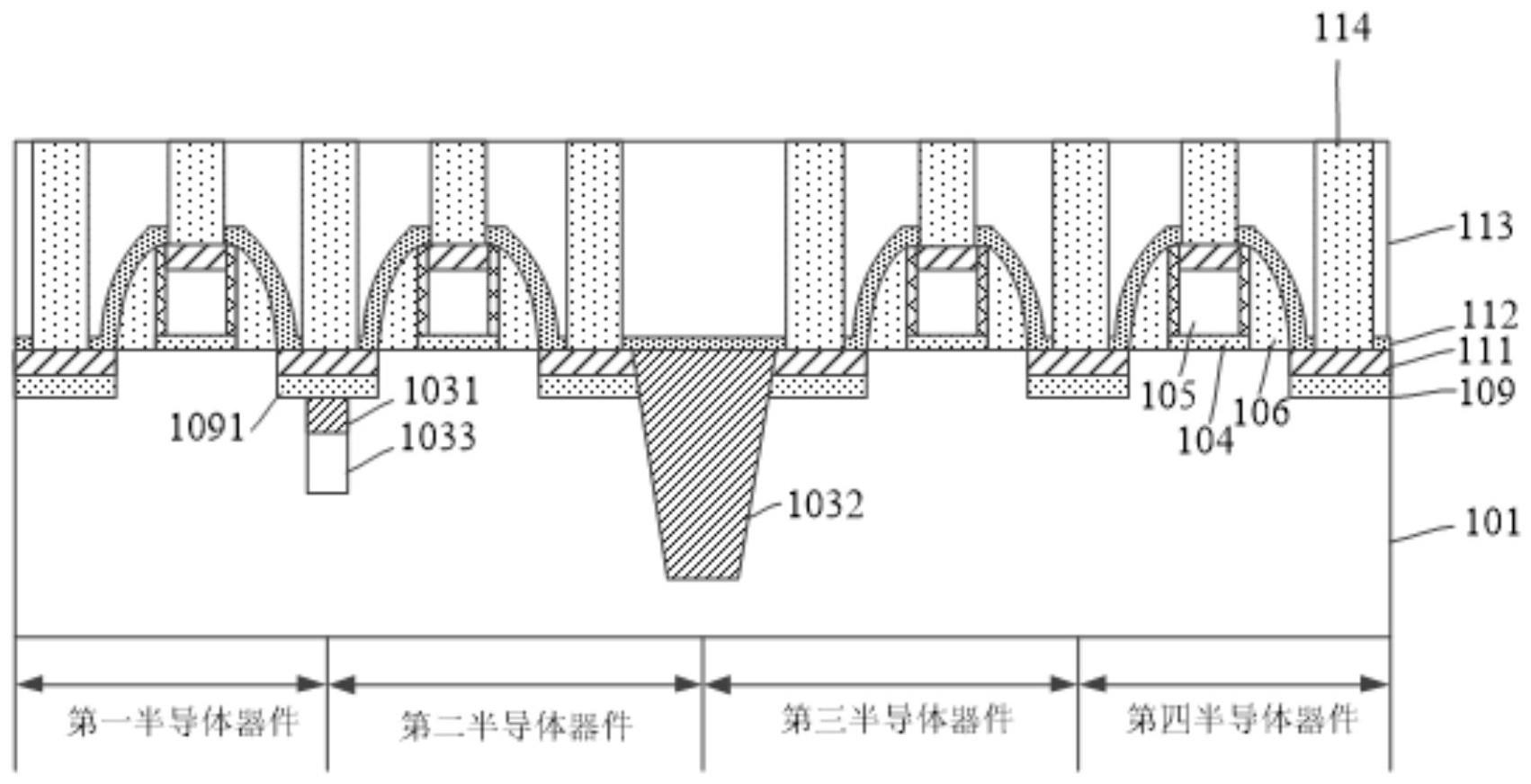

3、本发明提供一种半导体结构,至少包括:

4、衬底;

5、至少两个第一类型半导体器件,设置在所述衬底上,每个所述第一类型半导体器件包括栅极和掺杂区,所述掺杂区设置在所述栅极两侧的所述衬底中,且所述掺杂区包括共享掺杂区,所述共享掺杂区位于两个所述第一类型半导体器件之间;以及

6、应力释放沟槽,位于在所述共享掺杂区覆盖的所述衬底中。

7、在本发明一些实施例中,所述应力释放沟槽的开口宽度范围为5nm~10nm。

8、在本发明一些实施例中,所述应力释放沟槽的深度范围为30nm~50nm。

9、在本发明一些实施例中,所述应力释放沟槽的顶部填满介质层,未被所述介质层填充的所述应力释放沟槽形成应力释放空隙。

10、在本发明一些实施例中,所述应力释放空隙的深度范围为20nm~30nm。

11、在本发明一些实施例中,所述半导体结构包括多个凹部,所述凹部位于所述栅极两侧的衬底中。

12、在本发明一些实施例中,所述凹部的深度范围为8nm~15nm。

13、在本发明一些实施例中,所述半导体结构包括硅外延层,所述硅外延层位于所述凹部中。

14、在本发明一些实施例中,所述半导体结构包括接触孔蚀刻停止层,所述接触孔蚀刻停止层位于所述衬底和所述栅极上。

15、本发明还提供一种半导体结构的形成方法,至少包括以下步骤:

16、提供一衬底;

17、蚀刻所述衬底,形成应力释放沟槽;以及

18、在所述衬底上形成至少两个第一类型半导体器件,所述第一类型半导体器件设置在衬底上,每个所述第一类型半导体器件包括栅极和掺杂区,所述掺杂区设置在所述栅极两侧的衬底中,且所述掺杂区包括共享掺杂区,所述共享掺杂区位于两个所述第一类型半导体器件之间;

19、其中,所述应力释放沟槽位于在所述共享掺杂区的所述衬底中。

20、综上所述,本发明提供的一种半导体结构及其制作方法,形成应力层和接触孔蚀刻停止层,意想不到的效果是为第一类型半导体器件的沟道提供张应力,为第二类型半导体器件的沟道提供压应力。同时通过在相邻的第一类型半导体器件之间的共享掺杂区下的衬底中设置应力释放间隙,释放相互挤压的张应力,进而提高应力层和接触孔蚀刻停止层在沟道中施加的张应力效果,进而增强第一类型半导体器件的电子迁移率。而第二类型半导体器件之间的共享掺杂区下的衬底中未设置应力释放间隙,在形成应力层时,相邻半导体器件之间的应力相互积压,可以抑制张应力对第二类型半导体器件的负作用。并且通过在栅极两侧的衬底中设置凹部,并在凹部中形成硅外延层,可修复形成侧墙时造成的衬底损伤,还可以形成抬高的掺杂区。

21、当然,实施本发明的任一产品并不一定需要同时达到以上所述的所有优点。

技术特征:

1.一种半导体结构,其特征在于,至少包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述应力释放沟槽的开口宽度范围为5nm~10nm。

3.根据权利要求1所述的半导体结构,其特征在于,所述应力释放沟槽的深度范围为30nm~50nm。

4.根据权利要求1所述的半导体结构,其特征在于,所述应力释放沟槽的顶部填满介质层,未被所述介质层填充的所述应力释放沟槽形成应力释放空隙。

5.根据权利要求4所述的半导体结构,其特征在于,所述应力释放空隙的深度范围为20nm~30nm。

6.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构包括多个凹部,所述凹部位于所述栅极两侧的衬底中。

7.根据权利要求6所述的半导体结构,其特征在于,所述凹部的深度范围为8nm~15nm。

8.根据权利要求6所述的半导体结构,其特征在于,所述半导体结构包括硅外延层,所述硅外延层位于所述凹部中。

9.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构包括接触孔蚀刻停止层,所述接触孔蚀刻停止层位于所述衬底和所述栅极上。

10.一种半导体结构的形成方法,其特征在于,至少包括以下步骤:

技术总结

本发明公开了一种半导体结构及其制作方法,属于半导体技术领域。所述半导体结构至少包括:衬底;至少两个第一类型半导体器件,设置在所述衬底上,每个所述第一类型半导体器件包括栅极和掺杂区,所述掺杂区设置在所述栅极两侧的所述衬底中,且所述掺杂区包括共享掺杂区,所述共享掺杂区位于两个所述第一类型半导体器件之间;以及应力释放沟槽,位于在所述共享掺杂区覆盖的所述衬底中。通过本发明提供的半导体结构及其制作方法,可提高半导体结构的性能。

技术研发人员:陈兴,黄普嵩

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!