功率半导体器件及其制作方法

本申请涉及半导体,尤其涉及一种功率半导体器件及其制作方法。

背景技术:

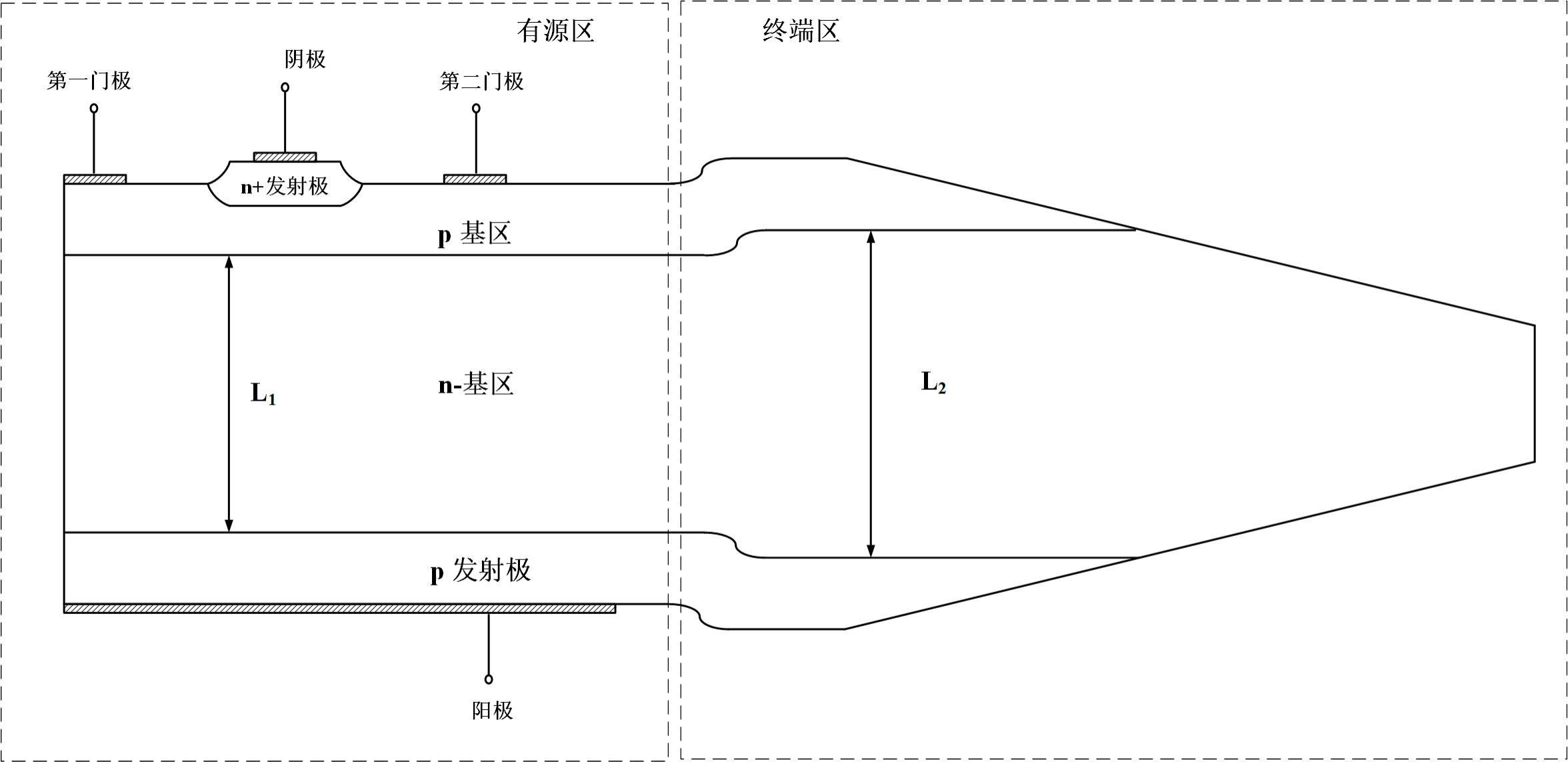

1、功率半导体器件可以分为内侧有源区和边缘终端区,其漏电流自然也分为内侧有源区的漏电流和外侧终端区的漏电流。器件阻断状态时,电场在边缘终端区发生畸变,存在电场强度极大值。而边缘终端区并非通流区域,外侧包裹钝化材料,使其散热能力大大降低。因此,器件阻断时漏电流集中、产热大,无直接接触的电极、散热差,有可能成为阻断状态芯片内的薄弱点。而对于不同电压等级、不同类型的芯片,有源区和终端区都有可能成为阻断状态的薄弱点。

技术实现思路

1、本申请的一个目的在于提供一种功率半导体器件,减小终端区的漏电流,对于薄弱点在终端区的功率半导体器件,提升阻断能力和最高运行结温。本申请的另一个目的在于提供一种功率半导体器件制作方法。

2、为了达到以上目的,本申请一方面公开了一种功率半导体器件,包括第一材料层以及形成于所述第一材料层上下两侧的第二材料层和第三材料层;

3、所述功率半导体器件包括有源区和终端区;

4、所述有源区包括位于所述第一材料层的第一掺杂区、位于所述第二材料层的第二掺杂区、位于所述第三材料层的第三掺杂区、阳极区以及阴极区 ;

5、所述终端区包括位于所述第一材料层的第一终端区以及位于所述第二材料层和所述第三材料层的第二终端区和第三终端区;

6、其中,所述第一终端区的厚度大于所述第一掺杂区的厚度,并且所述第二终端区和所述第三终端区的至少之一的表面高于对应的掺杂区的表面。

7、可选的,所述第一终端区的表面与对应侧所述第一掺杂区的表面的高度差为10~100um。

8、可选的,所述第一终端区与所述第一掺杂区通过过渡区连接,所述过渡区的长度为所述第一终端区的表面与对应侧所述第一掺杂区的表面的高度差的5~10倍。

9、可选的,所述第二材料层和所述第三材料层的厚度相同。

10、可选的,所述第二掺杂区与所述第二终端区的厚度相同,所述第三掺杂区与所述第三终端区的厚度相同。

11、可选的,所述阳极区包括设置在所述第二掺杂区表面的阳极电极。

12、可选的,所述阴极区包括形成在所述第三掺杂区表面的阴极发射极、设置在所述阴极发射极表面的阴极电极以及形成在所述第三掺杂区表面且位于所述阴极发射极两侧的第一门极和第二门极。

13、本申请还公开了一种功率半导体器件制作方法,包括:

14、将衬底的终端区掩蔽,对所述衬底进行刻蚀得到有源区;

15、对所述终端区和所述有源区整体进行预沉积或离子注入;

16、在预沉积或离子注入之后进行推进得到第一材料层以及位于所述第一材料层上下两侧的第二材料层和第三材料层,其中,所述第一材料层包括有源区的第一掺杂区和终端区的第一终端区,所述第二材料层包括有源区的第二掺杂区和终端区的第二终端区,所述第三材料层包括有源区的第三掺杂区和终端区的第三终端区,所述第一终端区的厚度大于第一掺杂区的厚度,所述第二终端区和所述第三终端区的至少之一的表面高于对应的掺杂区的表面;

17、在所述第二掺杂区的表面形成阳极区,在所述第三掺杂区的表面形成阴极区。

18、本申请还公开了一种功率半导体器件制作方法,包括:

19、将衬底的终端区掩蔽,对所述衬底进行预沉积或离子注入得到有源区并进行第一次推进;

20、对所述终端区和所述有源区整体进行预沉积或离子注入并进行第二次推进;

21、将所述终端区掩蔽,对所述有源区进行刻蚀得到第一材料层以及位于所述第一材料层上下两侧的第二材料层和第三材料层,其中,所述第一材料层包括有源区的第一掺杂区和终端区的第一终端区,所述第二材料层包括有源区的第二掺杂区和终端区的第二终端区,所述第三材料层包括有源区的第三掺杂区和终端区的第三终端区,所述第一终端区的厚度大于第一掺杂区的厚度,所述第二终端区和所述第三终端区的至少之一的表面高于对应的掺杂区的表面;

22、在所述第二掺杂区的表面形成阳极区,在所述第三掺杂区的表面形成阴极区。

23、本申请还公开了一种功率半导体器件制作方法,包括:

24、将衬底的终端区掩蔽,对所述衬底进行刻蚀得到有源区;

25、将所述有源区掩蔽,对所述终端区进行预沉积或离子注入并进行第一次推进;

26、对所述终端区和所述有源区整体进行预沉积或离子注入并进行第二次推进得到第一材料层以及位于所述第一材料层上下两侧的第二材料层和第三材料层,其中,所述第一材料层包括有源区的第一掺杂区和终端区的第一终端区,所述第二材料层包括有源区的第二掺杂区和终端区的第二终端区,所述第三材料层包括有源区的第三掺杂区和终端区的第三终端区,所述第一终端区的厚度大于第一掺杂区的厚度,所述第二终端区和所述第三终端区的至少之一的表面高于对应的掺杂区的表面;

27、在所述第二掺杂区的表面形成阳极区,在所述第三掺杂区的表面形成阴极区。

28、本申请功率半导体器件包括第一材料层以及形成于所述第一材料层上下两侧的第二材料层和第三材料层。所述功率半导体器件的有源区包括位于所述第一材料层的第一掺杂区、位于所述第二材料层的第二掺杂区、位于所述第三材料层的第三掺杂区、阳极区以及阴极区;终端区包括位于所述第一材料层的第一终端区以及位于所述第二材料层和所述第三材料层的第二终端区和第三终端区;其中,所述第一终端区的厚度大于所述第一掺杂区的厚度,并且所述第二终端区和所述第三终端区的至少之一的表面高于对应的掺杂区的表面。从而,本申请在使有源区结构不变的情况下,增加终端区的第一终端区的厚度,减小终端区的电流增益,进而减小终端区的漏电流,对薄弱点在终端区的功率半导体器件,提升阻断能力和最高运行结温。

技术特征:

1.一种功率半导体器件,其特征在于,包括第一材料层以及形成于所述第一材料层上下两侧的第二材料层和第三材料层;

2.根据权利要求1所述的功率半导体器件,其特征在于,所述第一终端区的表面与对应侧所述第一掺杂区的表面的高度差为10~100um。

3.根据权利要求1所述的功率半导体器件,其特征在于,所述第一终端区与所述第一掺杂区通过过渡区连接,所述过渡区的长度为所述第一终端区的表面与对应侧所述第一掺杂区的表面的高度差的5~10倍。

4.根据权利要求1所述的功率半导体器件,其特征在于,所述第二材料层和所述第三材料层的厚度相同。

5.根据权利要求1所述的功率半导体器件,其特征在于,所述第二掺杂区与所述第二终端区的厚度相同,所述第三掺杂区与所述第三终端区的厚度相同。

6.根据权利要求1所述的功率半导体器件,其特征在于,所述阳极区包括设置在所述第二掺杂区表面的阳极电极。

7.根据权利要求1所述的功率半导体器件,其特征在于,所述阴极区包括形成在所述第三掺杂区表面的阴极发射极、设置在所述阴极发射极表面的阴极电极以及形成在所述第三掺杂区表面且位于所述阴极发射极两侧的第一门极和第二门极。

8.一种功率半导体器件制作方法,其特征在于,包括:

9.一种功率半导体器件制作方法,其特征在于,包括:

10.一种功率半导体器件制作方法,其特征在于,包括:

技术总结

本申请提供了一种功率半导体器件及其制作方法,该功率半导体器件包括第一材料层以及形成于所述第一材料层上下两侧的第二材料层和第三材料层;所述功率半导体器件包括有源区和终端区;有源区包括位于所述第一材料层的第一掺杂区、位于所述第二材料层的第二掺杂区、位于所述第三材料层的第三掺杂区、阳极区以及阴极区;终端区包括位于所述第一材料层的第一终端区以及位于所述第二材料层和所述第三材料层的第二终端区和第三终端区;其中,所述第一终端区的厚度大于所述第一掺杂区的厚度,并且所述第二终端区和所述第三终端区的至少之一的表面高于对应的掺杂区的表面。本申请可提升功率半导体器件的阻断能力和最高运行结温。

技术研发人员:曾嵘,吴锦鹏,任春频,刘佳鹏,陈政宇,余占清,屈鲁

受保护的技术使用者:清华大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!