静电释放保护电路的制作方法

本发明涉及集成电路设计和制造领域,尤其是涉及一种静电释放保护电路。

背景技术:

1、随着集成电路制造工艺水平进入线宽的深亚微米时代,深亚微米集成电路更容易遭受到静电放电(esd,electro static discharge)冲击而失效,从而造成产品的可靠性下降。esd是指一定量的电荷从一个物体(例如人体)转移到另一个物体上(例如芯片)的过程。esd常常在集成电路的输入、输出单元口以及从电源到地的电路内部形成。这个过程可导致芯片在很短的时间内通过一个非常大的电流,35%以上的芯片失效是由esd引起的。

2、esd保护电路的设计目的就是避免工作电路成为esd的放电通路而遭到损害,保证在任意芯片引脚发生的esd,都有适合的低阻旁路将esd电流引入电源线,通过另外一个引脚建立esd电流通路放电。

3、然而,现有技术的esd保护电路可能会出现闩锁效应(latch up),从而导致芯片损坏。即便采取了一些措施,仍然只能抑制闩锁效应,不能完全避免闩锁效应的产生。

技术实现思路

1、本发明的目的在于提供一种静电释放保护电路,可以避免出现闩锁效应,从而防止芯片被损坏。

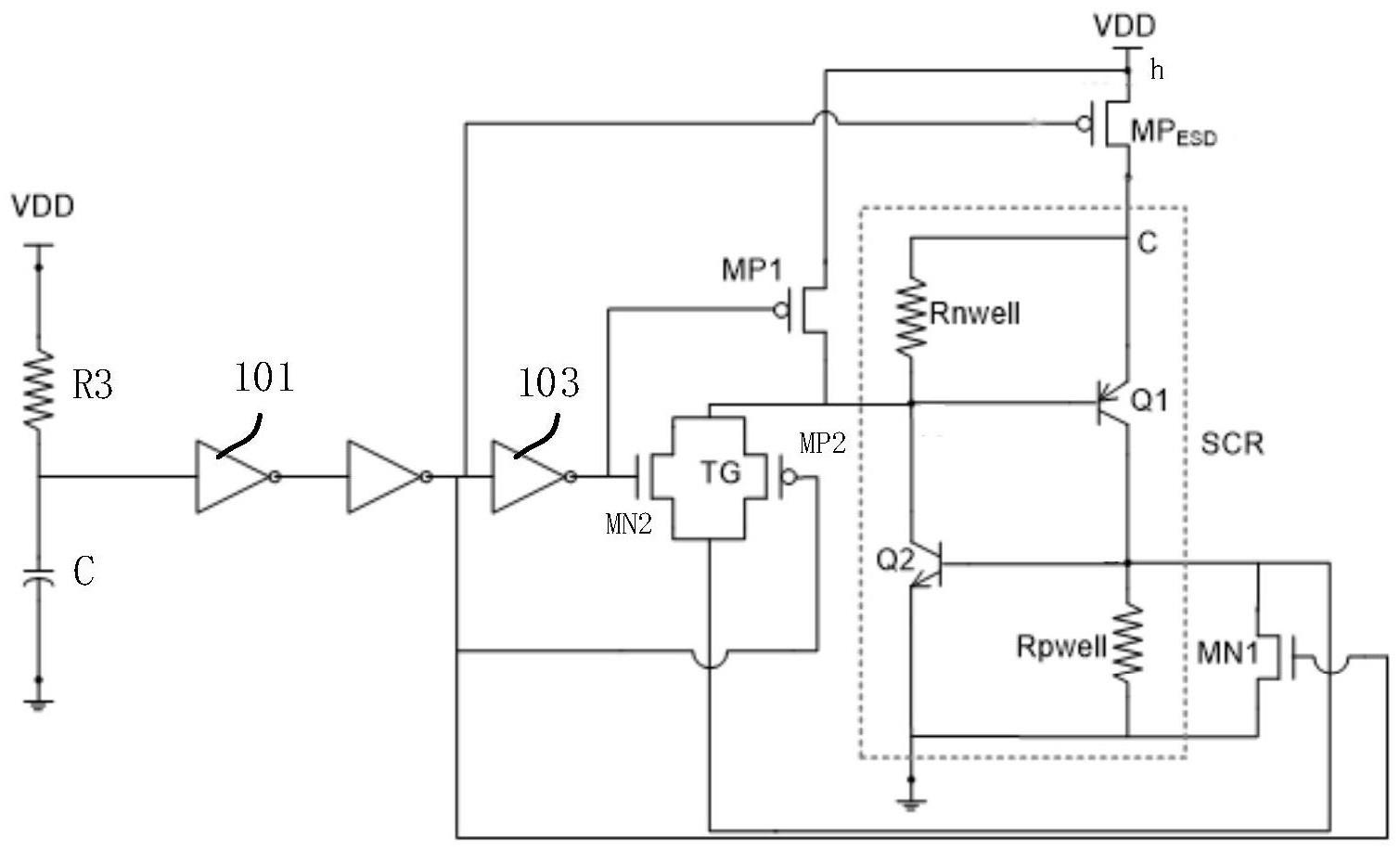

2、为了达到上述目的,本发明提供了一种静电释放保护电路,包括:第一pmos管、触发电路、若干反相器、传输门、第一三极管、第二三极管、第一电阻、第二电阻、上拉管和下拉管;其中,所述触发电路包括串联的电容和第三电阻,若干反相器依次串联,第一个为首反相器最后一个为尾反相器,所述首反相器输入接在所述电容和第三电阻之间,所述尾反相器的输出与所述传输门的nmos管和上拉管的栅极相连,所述尾反相器的输入与所述传输门的pmos管的栅极、下拉管的栅极以及第一pmos管的栅极相连;所述第一三极管的基极与所述第二三极管的集电极短接,所述第二三极管的基极与所述第一三极管的集电极短接,所述第二三极管的集电极通过所述第一电阻与所述第一三极管的发射极相连并共同连接第一pmos管的漏极,所述第一pmos管的源极接电源电压,所述第一三极管的集电极通过所述第二电阻与所述第二三极管的发射极相连并共同接地;所述传输门的第一控制端与所述上拉管的漏极和第一三极管的基极均相连,所述传输门的第二控制端与所述下拉管的漏极和第二三极管的基极均相连。

3、可选的,在所述的静电释放保护电路中,所述传输门由一pmos管和一nmos管并联形成。

4、可选的,在所述的静电释放保护电路中,所述反相器为3个,依次串联。

5、可选的,在所述的静电释放保护电路中,所述第三电阻阻值和电容容值的乘积的范围为0~2μs。

6、可选的,在所述的静电释放保护电路中,所述上拉管选为pmos管,所述下拉管选为nmos管。

7、本发明还提供了一种静电释放保护电路,包括:第一nmos管、触发电路、若干反相器、传输门、第一三极管、第二三极管、第一电阻、第二电阻、上拉管和下拉管;其中,所述触发电路包括串联的电容和第三电阻,若干反相器依次串联,第一个为首反相器最后一个为尾反相器,所述首反相器输入接在所述电容和第三电阻之间,所述尾反相器的输出与所述传输门的nmos管的栅极和上拉管的栅极以及第一nmos管的栅极相连,所述尾反相器的输入与所述传输门的pmos管的栅极和下拉管的栅极相连;所述第一三极管的基极与所述第二三极管的集电极短接,所述第二三极管的基极与所述第一三极管的集电极短接,所述第二三极管的集电极通过所述第一电阻与所述第一三极管的发射极相连并共同连接电源电压,所述第一三极管的集电极通过所述第二电阻与所述第二三极管的发射极相连并共同连接第一nmos管的源极,第一nmos管的漏极接地;所述传输门的第一控制端与所述上拉管的漏极和第一三极管的基极均相连,所述传输门的第二控制端与所述下拉管的漏极和第二三极管的基极均相连。

8、可选的,在所述的静电释放保护电路中,所述传输门由一pmos管和一nmos管并联而成。

9、可选的,在所述的静电释放保护电路中,所述反相器为3个,依次串联。

10、可选的,在所述的静电释放保护电路中,所述第三电阻阻值和电容容值的乘积的范围为0~2μs。

11、可选的,在所述的静电释放保护电路中,所述上拉管选为pmos管,所述下拉管选为nmos管。

12、在本发明提供的静电释放保护电路中,第一电阻、第二电阻、第一三极管和第二三极管组成可控硅整流器,在可控硅整流器连接的电源电压之间增加一个pmos管,拉高了第一pmos管和电源电压连接处的电压,使得此处的电压大于电源电压,避免了可控硅整流器出现闩锁效应,从而防止了芯片被损坏。或者,在可控硅整流器到地之间增加一个nmos管,拉高了可控硅整流器和电源电压连接处的电压,使得此处的电压大于电源电压,避免了可控硅整流器出现闩锁效应,从而防止了芯片被损坏。

技术特征:

1.一种静电释放保护电路,其特征在于,包括:第一pmos管、触发电路、若干反相器、传输门、第一三极管、第二三极管、第一电阻、第二电阻、上拉管和下拉管;所述触发电路包括串联的电容和第三电阻,若干反相器依次串联,第一个为首反相器最后一个为尾反相器,所述首反相器输入接在所述电容和第三电阻之间,所述尾反相器的输出与所述传输门的nmos管和上拉管的栅极相连,所述尾反相器的输入与所述传输门的pmos管的栅极、下拉管的栅极以及第一pmos管的栅极相连;所述第一三极管的基极与所述第二三极管的集电极短接,所述第二三极管的基极与所述第一三极管的集电极短接,所述第二三极管的集电极通过所述第一电阻与所述第一三极管的发射极相连并共同连接第一pmos管的漏极,所述第一pmos管的源极接电源电压,所述第一三极管的集电极通过所述第二电阻与所述第二三极管的发射极相连并共同接地;所述传输门的第一控制端与所述上拉管的漏极和第一三极管的基极均相连,所述传输门的第二控制端与所述下拉管的漏极和第二三极管的基极均相连。

2.如权利要求1所述的静电释放保护电路,其特征在于,所述传输门由一pmos管和一nmos管并联形成。

3.如权利要求1所述的静电释放保护电路,其特征在于,所述反相器为3个,依次串联。

4.如权利要求1所述的静电释放保护电路,其特征在于,所述第三电阻阻值和电容容值的乘积的范围为0~2μs。

5.如权利要求1所述的静电释放保护电路,其特征在于,所述上拉管选为pmos管,所述下拉管选为nmos管。

6.一种静电释放保护电路,其特征在于,包括:第一nmos管、触发电路、若干反相器、传输门、第一三极管、第二三极管、第一电阻、第二电阻、上拉管和下拉管;所述触发电路包括串联的电容和第三电阻,若干反相器依次串联,第一个为首反相器最后一个为尾反相器,所述首反相器输入接在所述电容和第三电阻之间,所述尾反相器的输出与所述传输门的nmos管的栅极和上拉管的栅极以及第一nmos管的栅极相连,所述尾反相器的输入与所述传输门的pmos管的栅极和下拉管的栅极相连;所述第一三极管的基极与所述第二三极管的集电极短接,所述第二三极管的基极与所述第一三极管的集电极短接,所述第二三极管的集电极通过所述第一电阻与所述第一三极管的发射极相连并共同连接电源电压,所述第一三极管的集电极通过所述第二电阻与所述第二三极管的发射极相连并共同连接第一nmos管的源极,第一nmos管的漏极接地;所述传输门的第一控制端与所述上拉管的漏极和第一三极管的基极均相连,所述传输门的第二控制端与所述下拉管的漏极和第二三极管的基极均相连。

7.如权利要求6所述的静电释放保护电路,其特征在于,所述传输门由一pmos管和一nmos管并联而成。

8.如权利要求6所述的静电释放保护电路,其特征在于,所述反相器为3个,依次串联。

9.如权利要求6所述的静电释放保护电路,其特征在于,所述第三电阻阻值和电容容值的乘积的范围为0~2μs。

10.如权利要求6所述的静电释放保护电路,其特征在于,所述上拉管选为pmos管,所述下拉管选为nmos管。

技术总结

本发明提供了一种静电释放保护电路,包括:电容和第三电阻串联,若干反相器串联,首反相器输入接在电容和第三电阻之间,尾反相器输出与传输门NMOS管和上拉管的栅极相连,尾反相器输入与传输门PMOS管、下拉管和第一PMOS管的栅极相连;第一三极管的基极与第二三极管的集电极短接,第二三极管的基极与第一三极管的集电极短接,第二三极管的集电极通过第一电阻与第一三极管的发射极相连并连接第一PMOS管的漏极,第一PMOS管的源极接电源电压,第一三极管的集电极通过第二电阻与第二三极管的发射极相连并接地;传输门第一控制端与上拉管的漏极和第一三极管的基极相连,传输门第二控制端与下拉管的漏极和第二三极管的基极相连。

技术研发人员:吕斌

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!