芯片封装结构和芯片封装方法与流程

本发明涉及芯片封装领域,尤其涉及芯片封装结构和芯片封装方法。

背景技术:

1、预塑封引线框架是一种新型的芯片封装用基板,可以用于对半导体裸芯片进行封装,其可以通过模塑材料将若干导电柱和/或电路包封其中并露出端面,不但能够根据芯片焊点的需要精确排布导电柱的位置,还兼具固定、绝缘、防尘、防水、防氧化、防腐蚀等保护效果。当芯片焊点被焊接至导电柱端面后,为了保护焊点,通常会向芯片底部注入填充胶以保护芯片焊点,避免在后续的工序中破裂。但由于填充胶具有一定的流动性,在注射填充胶的过程中难以控制其蔓延的范围,不但可能无法填满芯片底部空间、影响保护效果,还会对芯片周围的预塑封引线框架造成污染、影响产品可靠性,同时也浪费了填充胶、增加了成本。

技术实现思路

1、为了解决上述技术问题,本发明的目的是提供一种能够限制填充胶填充范围的芯片封装结构及其封装方法。

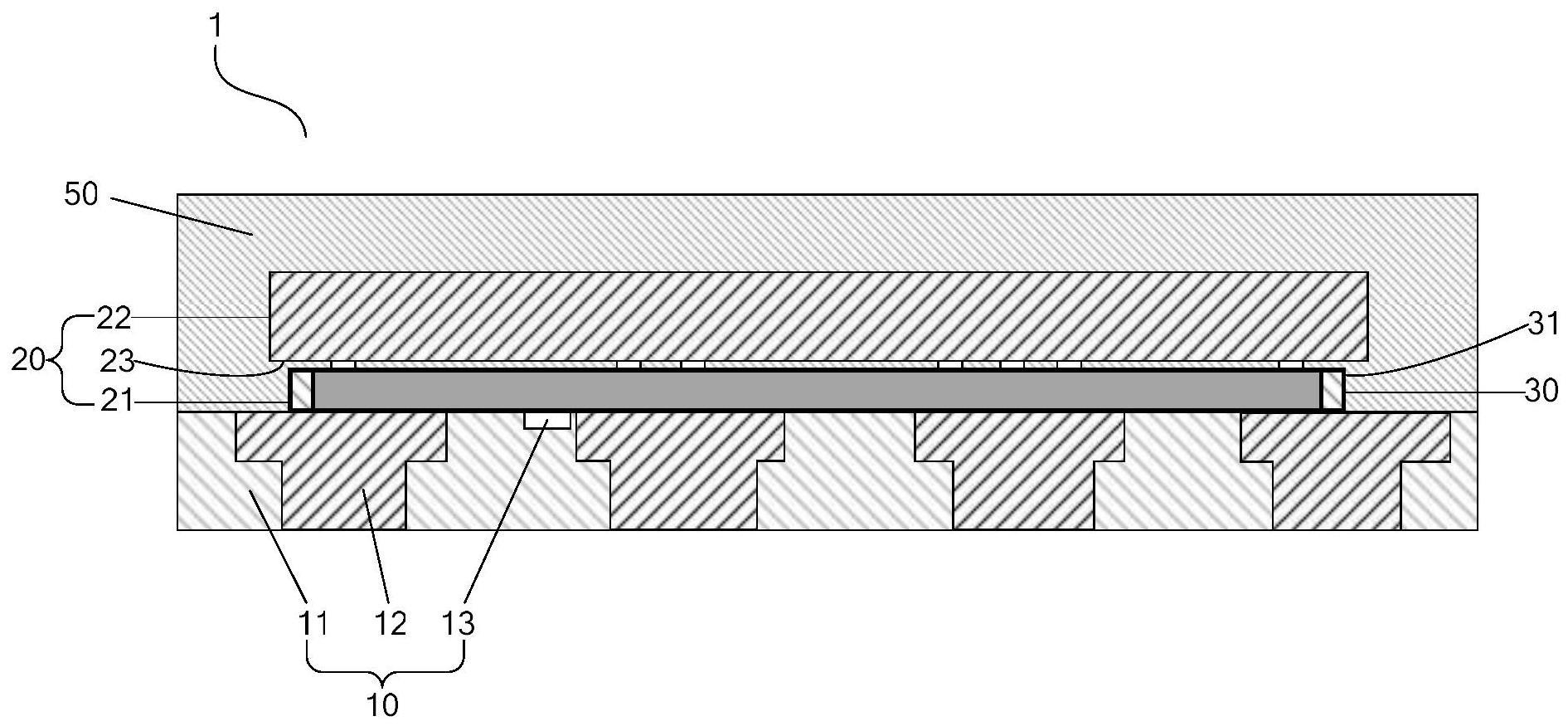

2、本发明提供了一种芯片封装结构,包括:预塑封引线框架,其包括绝缘填充层,以及埋嵌于所述绝缘填充层内并贯通所述绝缘填充层上下表面的多个导电体;芯片,其每个焊点分别与所述绝缘填充层上表面的所述多个导电体中的至少一个导电体电连接;以及挡墙,其设置于所述预塑封引线框架的上表面,所述挡墙具有环绕所述芯片的至少部分焊点的环形结构,所述挡墙和所述预塑封引线框架上表面限定注胶空间,其中,所述绝缘填充层还具有注胶通道,所述注胶通道连通所述注胶空间和所述挡墙外部的空间。

3、在一些实施例中,所述注胶通道为设置于所述绝缘填充层上表面的凹槽。

4、在一些实施例中,所述注胶通道为贯穿所述绝缘填充层上下表面的通孔。

5、在一些实施例中,所述注胶通道为贯穿所述挡墙侧壁内外侧的通孔。

6、在一些实施例中,所述挡墙的数量为两个以上。

7、在上述实施例中,每个所述挡墙环绕所述芯片的不同焊点,以形成多个注胶空间。

8、在一些实施例中,所述芯片封装结构还包括填充胶,所述填充胶填充所述注胶空间。

9、在上述实施例中,所述芯片封装结构还包括绝缘封装层,所述绝缘封装层设置于所述预塑封引线框架上表面的上方,并整体包封所述芯片。

10、在一些实施例中,所述挡墙的数量为两个以上,每个所述挡墙环绕所述芯片的不同焊点,以形成多个注胶空间,所述多个注胶空间包括第一注胶空间和第二注胶空间,且所述第一注胶空间和所述第二注胶空间的填充胶的导热性能不同。

11、在一些实施例中,所述挡墙可拆卸地设置于所述预塑封引线框架的上表面。

12、在上述各实施例中,所述芯片覆盖所述挡墙环绕的注胶空间。

13、在上述实施例中,所述挡墙的上沿与所述芯片本体的底面的距离小于所述预塑封引线框架的上表面与所述芯片本体的底面的距离的十分之一。

14、本发明另一方面提供了一种芯片封装方法,包括:用绝缘填充层包封多个导电体,使所述多个导电体的两个端面分别露出于所述绝缘填充层的上下表面,制成预塑封引线框架;在预塑封引线框架上表面设置挡墙,所述挡墙具有环绕所述芯片的至少部分焊点的环形结构,所述挡墙和所述预塑封引线框架上表面限定注胶空间;在所述绝缘填充层上制作注胶通道,所述注胶通道连通所述注胶空间和所述挡墙外部的空间;将芯片的每个焊点分别与所述绝缘填充层上表面的所述多个导电体中的至少一个导电体电连接。

15、在一些实施例中,在所述绝缘填充层上制作注胶通道,包括:在所述绝缘填充层上表面形成凹槽,将所述凹槽作为注胶通道。

16、在一些实施例中,在所述绝缘填充层上制作注胶通道,包括:在所述绝缘填充层形成贯通其上下表面的通孔,将所述通孔作为注胶通道。

17、在一些实施例中,所述芯片覆盖所述注胶空间。

18、在一些实施例中,在将芯片的每个焊点分别与所述绝缘填充层上表面的所述多个导电体中的至少一个导电体电连接后,所述方法还包括:通过所述注胶通道注入填充胶,填充所述注胶空间。

19、在上述实施例中,所述挡墙的数量为两个以上,每个所述挡墙环绕所述芯片的不同焊点,以形成多个注胶空间,所述多个注胶空间包括第一注胶空间和第二注胶空间,所述注胶通道包括第一注胶通道和第二注胶通道;通过所述注胶通道注入填充胶,填充所述注胶空间,包括:通过所述第一注胶通道注入第一填充胶,填充所述第一注胶空间;通过所述第二注胶通道注入第二填充胶,填充所述第二注胶空间;其中,所述第一填充胶与所述第二填充胶的导热性能不同。

20、在一些实施例中,通过所述注胶通道注入填充胶,填充所述注胶空间后,所述方法还包括:通过烘烤或风干使所述填充胶固化。

21、在一些实施例中,通过烘烤或风干使所述填充胶固化后,所述方法还包括:拆卸所述挡墙。

22、在一些实施例中,所述方法还包括:采用绝缘材料对所述芯片及所述预塑封引线框架上表面进行整体包封。

23、本发明通过在预塑封引线框架的绝缘填充层上设置挡墙以限定注胶空间,限制填充胶填充范围,能够节省填充胶并避免填充胶污染周围的预塑封引线框架。图1本发明还进一步在绝缘填充层上设置连通注胶空间和挡墙外部空间的注胶通道,使得向注胶空间注入填充胶的方式更加灵活,以获得更好的填充胶填充效果,也可以更加节省填充胶。

技术特征:

1.一种芯片封装结构,其特征在于,包括:

2.如权利要求1所述的芯片封装结构,其特征在于,所述注胶通道为设置于所述绝缘填充层上表面的凹槽。

3.如权利要求1所述的芯片封装结构,其特征在于,所述注胶通道为贯穿所述绝缘填充层上下表面的通孔。

4.如权利要求1所述的芯片封装结构,其特征在于,所述注胶通道为贯穿所述挡墙侧壁内外侧的通孔。

5.如权利要求1所述的芯片封装结构,其特征在于,所述挡墙的数量为两个以上。

6.如权利要求5所述的芯片封装结构,其特征在于,每个所述挡墙环绕所述芯片的不同焊点,以形成多个注胶空间。

7.如权利要求1所述的芯片封装结构,其特征在于,所述芯片封装结构还包括填充胶,所述填充胶填充所述注胶空间。

8.如权利要求7所述的芯片封装结构,其特征在于,所述芯片封装结构还包括绝缘封装层,所述绝缘封装层设置于所述预塑封引线框架上表面的上方,并整体包封所述芯片。

9.如权利要求7所述的芯片封装结构,其特征在于,所述挡墙的数量为两个以上,每个所述挡墙环绕所述芯片的不同焊点,以形成多个注胶空间,所述多个注胶空间包括第一注胶空间和第二注胶空间,且所述第一注胶空间和所述第二注胶空间的填充胶的导热性能不同。

10.如权利要求1所述的芯片封装结构,其特征在于,所述挡墙可拆卸地设置于所述预塑封引线框架的上表面。

11.如权利要求1-10中任一项所述的芯片封装结构,其特征在于,所述芯片覆盖所述挡墙环绕的注胶空间。

12.如权利要求11所述的芯片封装结构,其特征在于,所述挡墙的上沿与所述芯片本体的底面的距离小于所述预塑封引线框架的上表面与所述芯片本体的底面的距离的十分之一。

13.一种芯片封装方法,包括:

14.如权利要求13所述的芯片封装方法,其特征在于,在所述绝缘填充层上制作注胶通道,包括:

15.如权利要求13所述的芯片封装方法,其特征在于,在所述绝缘填充层上制作注胶通道,包括:

16.如权利要求13所述的芯片封装方法,其特征在于,所述芯片覆盖所述注胶空间。

17.如权利要求13所述的芯片封装方法,其特征在于,在将芯片的每个焊点分别与所述绝缘填充层上表面的所述多个导电体中的至少一个导电体电连接后,所述方法还包括:

18.如权利要求17所述的芯片封装方法,其特征在于,所述挡墙的数量为两个以上,每个所述挡墙环绕所述芯片的不同焊点,以形成多个注胶空间,所述多个注胶空间包括第一注胶空间和第二注胶空间,所述注胶通道包括第一注胶通道和第二注胶通道;通过所述注胶通道注入填充胶,填充所述注胶空间,包括:

19.如权利要求17所述的芯片封装方法,其特征在于,通过所述注胶通道注入填充胶,填充所述注胶空间后,所述方法还包括:

20.如权利要求17所述的芯片封装方法,其特征在于,通过烘烤或风干使所述填充胶固化后,所述方法还包括:

21.如权利要求17-20中任一项所述的芯片封装方法,其特征在于,所述方法还包括:

技术总结

本发明公开了一种芯片封装结构和芯片封装方法,其中,芯片封装结构包括:预塑封引线框架,其包括绝缘填充层,以及埋嵌于绝缘填充层内并贯通绝缘填充层上下表面的多个导电体;芯片,其每个焊点分别与绝缘填充层上表面的多个导电体中的至少一个导电体电连接;以及挡墙,其设置于预塑封引线框架的上表面,挡墙具有环绕芯片的至少部分焊点的环形结构,挡墙和预塑封引线框架上表面限定注胶空间,绝缘填充层还具有连通注胶空间和挡墙外部的空间的注胶通道。本发明的芯片封装结构具有节省填充胶,以及避免填充胶污染周围的预塑封引线框架的特点。

技术研发人员:范荣,刘庭,张月升,濮虎

受保护的技术使用者:江苏长电科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!