光机电模组、半导体封装组件及其制造方法与流程

本申请涉及半导体封装,尤其涉及一种光机电模组、半导体封装组件及其制造方法。

背景技术:

1、现有技术中,半导体封装的方式主要有板上芯片封装(chips on board,简称cob)、倒装封装(flip chip)和芯片级封装(chip scale package,简称csp),cob封装技术是先将半导体芯片粘接在电路板表面,再采用导线电连接半导体芯片和电路板上的焊垫;flip chip封装技术是在芯片的焊垫上先植金球,再将金球与电路板上的焊垫接合;csp封装技术是先对半导体芯片进行3d封装,再于半导体芯片下方植锡球,通过锡球焊接在电路板上。

2、cob封装技术中,由于芯片与电路板的焊垫之间需要保持一定距离,且芯片上方需要保留一定空间,从而不利于半导体封装结构的小型化。并且,半导体芯片通过胶粘在电路板表面,不可避免地会产生变型组装工差问题,进而影响到像素平面的平整度与各结构之间的高度差异,造成光程的差异,影响成像质量。另外,当应用于摄像模组时,在影像感测芯片像素越来越大的情况下,影像感测器的成像区与电路板的焊垫的距离越来越近,光线很容易打到导线而反射到成像区,造成杂散光。flip chip封装技术中,半导体芯片的焊垫上的金球需要有一定的高度方能补偿电路板的变形,电路板需要凸出到芯片上方,在影像感测芯片的像素越来越大的状况下,设计难度较大。csp封装技术中,半导体芯片在经3d封装后,厚度方向上的尺寸增大,且仍需要采用smt技术等焊接于电路板上,导致整个封装结构的尺寸无法缩小。现有的各种半导体封装技术导致半导体芯片的成本无法下降,封装后的尺寸无法缩小。

技术实现思路

1、有鉴于此,本申请提供一种半导体封装组件及其制造方法,以解决上述问题。

2、另外,本申请还有必要提供一种应用上述半导体封装组件的光机电模组。

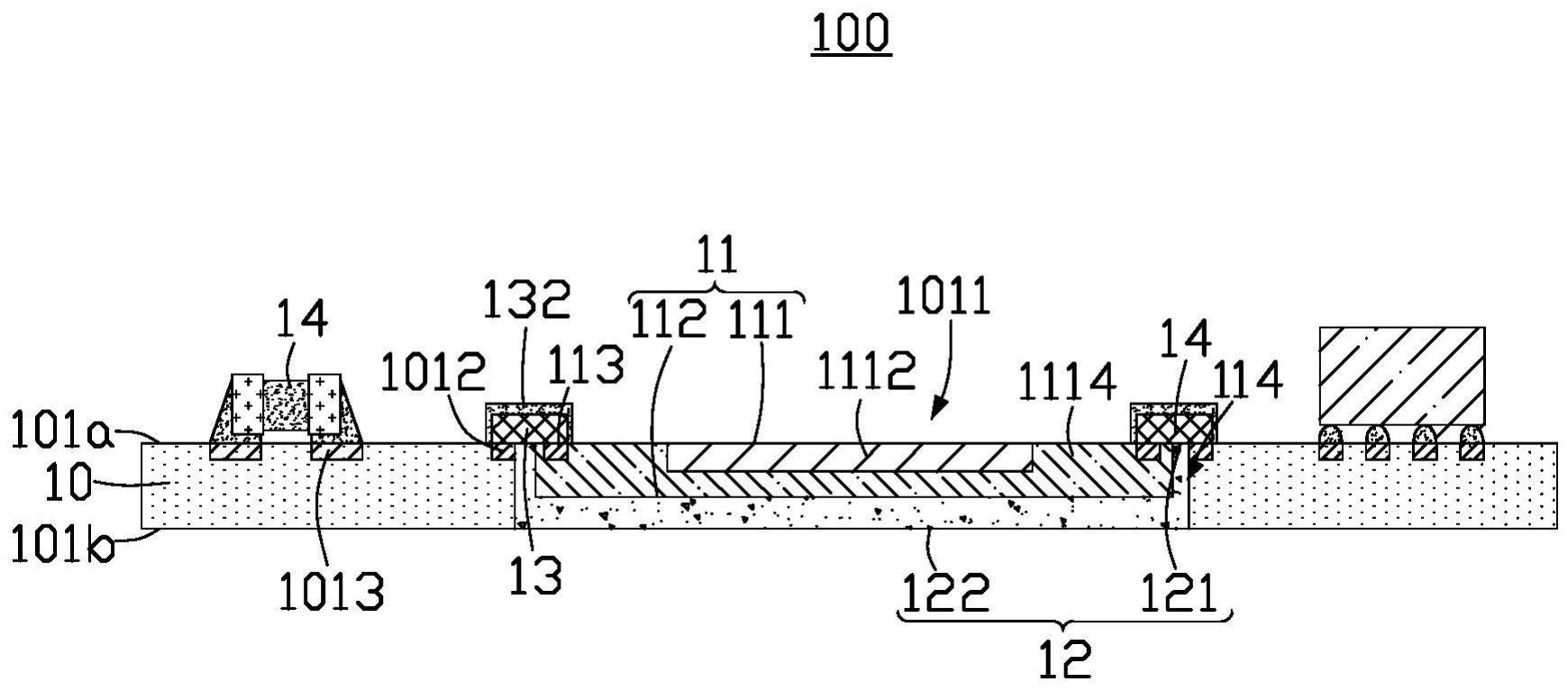

3、本申请提供了一种半导体封装组件,包括电路板、至少一芯片、塑封体和导线,所述电路板具有相对的第一表面和第二表面,所述第一表面朝所述第二表面凹设有至少一收容孔,所述第一表面上设有多个焊垫;所述芯片设于所述收容孔内,且所述芯片和所述电路板通过间隙隔开;所述芯片包括相对的有源面和无源面,所述有源面与所述第一表面朝向同一侧,所述有源面设有多个引脚;所述塑封体至少设于所述间隙并粘接所述芯片与所述收容孔的孔壁,所述导线贴设于所述塑封体背离所述第二表面的第三表面且所述导线电连接所述焊垫和所述引脚。

4、本申请还提供另一种半导体封装组件,包括芯片、塑封体和导线,所述芯片包括相对的有源面和无源面,所述有源面设有多个引脚,所述塑封体包覆所述芯片的所述无源面和侧面,所述塑封体包括与所述芯片的所述有源面朝向同一侧的第三表面,所述第三表面设有多个焊垫,所述导线贴设于所述塑封体的所述第三表面且所述导线电连接所述焊垫和所述引脚。

5、本申请还提供一种半导体封装组件的制造方法,包括以下步骤:

6、提供一电路板,所述电路板具有相对的第一表面和第二表面,所述第一表面朝所述第二表面凹设有至少一收容孔,所述第一表面上设有多个焊垫;

7、于所述电路板的所述第一表面或所述第二表面设置一载板,于所述收容孔内设置一芯片,且所述芯片和所述电路板通过间隙隔开;所述芯片包括相对的有源面和无源面,所述有源面设有多个引脚,所述第一表面和所述有源面朝向同一侧;

8、至少于所述间隙内填充树脂形成塑封体以粘接所述芯片与所述收容孔的孔壁,并移除所述载板;

9、于所述塑封体背离所述第二表面的第三表面贴设导线以电连接所述焊垫和所述引脚。

10、本申请还提供一种光机电模组,包括上述半导体封装组件。

11、本申请中提供的半导体封装组件通过于所述电路板内开设收容孔,并将芯片设于所述收容孔内,且设置塑封体进行保护,使得所述芯片和所述电路板在同一平面,可有效降低整个封装组件的高度、降低成本,且通过提供一个平整且高度一致的像素平面,可有效提升成像质量。相较于传统的打金线连接,采用平面的导线电连接所述芯片和所述电路板,可有效减少杂散光,提高成像质量。另外,后续设置主动元件和/或被动元件时可以更靠近芯片,电性特性更好,整个所述半导体封装组件的尺寸更小型化、薄型化。

技术特征:

1.一种半导体封装组件,其特征在于,包括:

2.如权利要求1所述的半导体封装组件,其特征在于,所述焊垫设于所述第一表面靠近所述芯片的边缘处,所述引脚与所述焊垫相邻设置且设于所述有源面的边缘处。

3.如权利要求1所述的半导体封装组件,其特征在于,所述收容孔贯穿所述第一表面和所述第二表面,所述塑封体还覆盖所述芯片的所述无源面,所述芯片的所述有源面和所述电路板的所述第一表面以及所述塑封体的所述第三表面平齐,所述塑封体覆盖所述芯片的无源面的部分背离所述芯片的表面与所述电路板的第二表面平齐。

4.如权利要求1所述的半导体封装组件,其特征在于,所述有源面位于所述第一表面与所述第二表面之间,所述第三表面为一倾斜面连接所述第一表面与所述第二表面;

5.如权利要求1所述的半导体封装组件,其特征在于,所述半导体封装组件还包括绝缘保护层,所述绝缘保护层覆盖所述导线并与所述第三表面粘接,所述导线位于所述绝缘保护层与所述第三表面之间。

6.如权利要求1所述的半导体封装组件,其特征在于,所述焊垫表面设有第一金属块,所述引脚表面设有第二金属块;

7.如权利要求1所述的半导体封装组件,其特征在于,所述芯片的所述无源面贴设于所述收容孔的底壁。

8.一种半导体封装组件,其特征在于,包括:

9.一种半导体封装组件的制造方法,其特征在于,包括以下步骤:

10.如权利要求9所述的半导体封装组件的制造方法,其特征在于,步骤“于所述收容孔内设置一芯片”包括:

11.一种光机电模组,其特征在于,包括如权利要求1至8中任一项所述的半导体封装组件。

12.如权利要求11所述的光机电模组,其特征在于,还包括光学元件和胶体,所述光学元件通过所述胶体粘接于所述电路板与所述芯片的结合处,并与所述芯片间隔设置。

技术总结

一种光机电模组、半导体封装组件及其制造方法,该半导体封装组件包括电路板、至少一芯片、塑封体和导线,电路板具有相对的第一表面和第二表面,所述第一表面朝所述第二表面凹设有至少一收容孔,所述第一表面上设有多个焊垫;芯片设于所述收容孔内,且所述芯片和所述电路板通过间隙隔开;所述芯片包括相对的有源面和无源面,所述有源面与所述第一表面朝向同一侧,所述有源面设有多个引脚;塑封体至少设于所述间隙并粘接所述芯片与所述收容孔的孔壁;导线贴设于所述塑封体背离所述第二表面的第三表面且所述导线电连接所述焊垫和所述引脚。该半导体封装组件有利于产品的小型化和薄型化,且有利于提高成像质量、降低生产成本。

技术研发人员:许信彦,冯自立

受保护的技术使用者:信扬科技(佛山)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!