一种三维存算一体化芯片的制作方法

本申请涉及半导体器件,具体地,涉及一种三维存算一体化芯片。

背景技术:

1、存算一体技术概念的形成,最早可以追溯到上个世纪70年代。随着近几年云计算和人工智能(ai)应用的发展,面对计算中心的数据洪流,数据搬运慢、搬运能耗大等问题成为了计算的关键瓶颈。在过去二十年,处理器性能以每年大约55%的速度提升,内存性能的提升速度每年只有10%左右。结果长期下来,不均衡的发展速度造成了当前的存储速度严重滞后于处理器的计算速度。在传统计算机的设定里,存储模块是为计算服务的,因此设计上会考虑存储与计算的分离与优先级。但是如今,存储和计算不得不整体考虑,以最佳的配合方式为数据采集、传输和处理服务。这里面,存储与计算的再分配过程就会面临各种问题,而它们主要体现为存储墙、带宽墙和功耗墙问题。

2、虽然多核(例如cpu)/众核(例如gpu)并行加速技术也能提升算力,但在后摩尔时代,存储带宽制约了计算系统的有效带宽,芯片算力增长步履维艰。从处理单元外的存储器提取数据,搬运时间往往是运算时间的成百上千倍,整个过程的无用能耗大概在60%-90%之间,能效非常低,“存储墙”成为了数据计算应用的一大障碍。特别是,深度学习加速的最大挑战就是数据在计算单元和存储单元之间频繁的移动。

3、现有的存算一体化芯片是将cpu芯片和dram芯片采用3d封装的方式,将dram与cpu芯片进行集成。3d封装的存算一体化芯片有一定的技术效果,由于3d封装后互联线增加,集成后cpu芯片与dram芯片之前的互联速度将得到极大的提升,并且由于线路的增加,带宽增加。并且由于更短的连线,可以降低传输损耗和传输延迟。但是3d封装的存算一体化芯片仍然具有很多问题。

4、3d封装工艺步骤为:1.首先在wafer工艺上采用tsv(through silicon via)工艺。2.将芯片正面进行封装。3.然后将芯片背面减薄漏出tsv;4.将漏出的tsv进行处理,然后将dram(动态随机存取内存)和逻辑芯片进行金属互联;5.最后合封到一个封装材料内。

5、3d封装的存算一体化芯片由于采用了tsv工艺和wafer减薄工艺,所以其厚度一般在50um以上,tsv通孔的深度需要在50um以上,这影响了器件的互联速率。此外,由于采用tsv工艺,tsv通孔的宽度较大,这会影响tsv使用的灵活性,相当于降低了芯片间互联的带宽。另外,由于芯片厚度较厚,所以难以实现多层的互联,所以对于现有的技术的提升有限。最后,由于器件采用tsv工艺连接存储芯片,其散热路径不如背面接地的芯片。

6、3d封装存算一体化芯片,cpu芯片计算单元的计算速度仍然已经远远超过了dram芯片存储单元的存储速度,所以数据在计算单元与存储单元之间搬运以及存储单元之间的搬运拖累了整体处理器的性能。

7、因此,传统的3d封装存算一体化芯片不能适应芯片的发展方向,急需真正的3d存算一体化芯片,是本领域技术人员急需要解决的技术问题。

8、在背景技术中公开的上述信息仅用于加强对本申请的背景的理解,因此其可能包含没有形成为本领域普通技术人员所知晓的现有技术的信息。

技术实现思路

1、本申请实施例提供了一种三维存算一体化芯片,以解决传统的3d封装存算一体化芯片不能适应芯片的发展方向的技术问题。

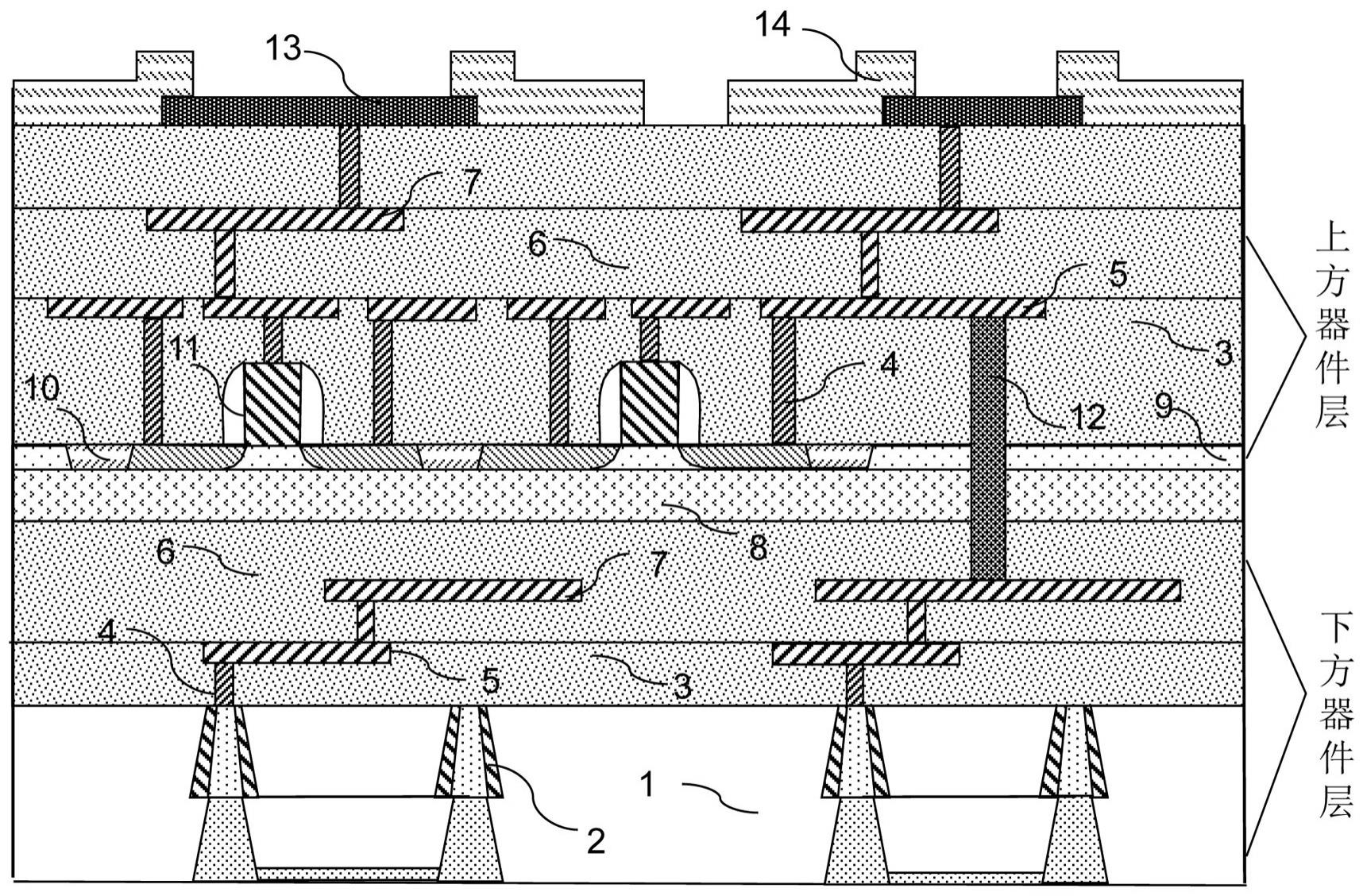

2、本申请实施例提供了一种三维存算一体化芯片,包括:

3、下方器件层;

4、形成在下方器件层上方的上方器件层;

5、其中,下方器件层和上方器件层中一个为具有多个分布式排列计算单元的逻辑功能层,另一个为具有多个分布式排列存储单元的存储层。

6、本申请实施例由于采用以上技术方案,具有以下技术效果:

7、本申请实施例的三维存算一体化芯片,本质上是一个芯片,在垂向方向自下而上设置下方器件层和上方器件层。其中一个为具有多个分布式排列计算单元的逻辑功能层,另一个为具有多个分布式排列存储单元的存储层。逻辑功能层具有多个分布式排列的计算单元,这样,需要进行的计算量能够被分配到各个计算单元分别进行,使得算力较高。另一方面,存储层具有多个分布式排列的存储单元,使得存储能力较大。现有技术中,逻辑功能是由独立的逻辑芯片完成,存储功能是由独立的存储芯片完成,逻辑芯片和存储芯片通过3d封装工艺封装在一起,逻辑芯片和存储芯片各自都有一个衬底,衬底本身厚度需要较大,使得3d封装的存算一体化芯片的厚度较大。本申请实施例的三维存算一体化芯片,本质上是一个芯片,这样自身厚度需要较大的衬底只需要有一个即可,就使得本申请实施例的三维存算一体化芯片的厚度能够控制的较小,三维存算一体化芯片的厚度带来的优势在于后续的逻辑功能层和存储层之间在垂向的连接能够通过更短的连接实现,逻辑功能层和存储层之间的传输损耗和传输延迟能够较小。

技术特征:

1.一种三维存算一体化芯片,其特征在于,包括:

2.根据权利要求1所述的三维存算一体化芯片,其特征在于,所述下方器件层为底部器件层,所述上方器件层为上方第一器件层;

3.根据权利要求1所述的三维存算一体化芯片,其特征在于,所述下方器件层为底部器件层,所述底部器件层为逻辑功能层;

4.根据权利要求3所述的三维存算一体化芯片,其特征在于,所述底部器件层包括自下而上设置的底部衬底、逻辑器件层、底部绝缘层;其中,多个分布式排列的所述计算单元设置在逻辑器件层内,所述底部绝缘层中具有与逻辑器件层的计算单元连接的电连接结构。

5.根据权利要求4所述的三维存算一体化芯片,其特征在于,上方第h器件层包括自下而上设置的第h半导体层、第h存储电路层、第h绝缘层;其中,多个分布式排列的所述存储单元设置在第h存储电路层内,所述第h绝缘层中具有与第h存储电路层的存储单元连接的电连接结构,h遍取从1到n的值;其中,本层的绝缘层的电连接结构和上一层的绝缘层的电连接结构的电连接;

6.根据权利要求5所述的三维存算一体化芯片,其特征在于,还包括:

7.根据权利要求6所述的三维存算一体化芯片,其特征在于,还包括:

8.根据权利要求7所述的三维存算一体化芯片,其特征在于,所述第h半导体层具有贯穿第h半导体层的器件隔离,器件隔离包围在存储电路层的存储单元的外侧;

9.根据权利要求8所述的三维存算一体化芯片,其特征在于,所述第h半导体层为第h薄硅层;所述第h薄硅层厚度的取值范围为大于等于2纳米小于等于220纳米;

10.根据权利要求9所述的三维存算一体化芯片,其特征在于,在形成第h存储电路层的存储单元过程中的离子注入后的退火工艺和消除应力的退火工艺中,采用低热预算闪光毫秒退火工艺,低热预算闪光毫秒退火工艺退火温度的取值范围为大于等于750°c小于等于1200°c;

11.根据权利要求8所述的三维存算一体化芯片,其特征在于,所述底部器件层还包括:

12.根据权利要求10所述的三维存算一体化芯片,其特征在于,所述底部绝缘层包括自下而上设置的氧化物绝缘层和低介电常数绝缘层;

13.根据权利要求12所述的三维存算一体化芯片,其特征在于,形成在第h存储电路层的存储单元的源极和漏极中需要设置竖向钨通孔的位置的欧姆接触。

14.根据权利要求13所述的三维存算一体化芯片,其特征在于,所述第h绝缘层包括自下而上设置的氧化硅绝缘层和低介电常数绝缘层;

15.根据权利要求14所述的三维存算一体化芯片,其特征在于,还包括退火阻挡层,退火阻挡层用于遮盖本层的器件层的结构,且所述退火阻挡层避开竖向通孔以不与竖向通孔连接,以阻挡位于上方的器件层制备过程中退火工艺的退火光对本层的器件层退火阻挡层之下的结构进行加热;

16.根据权利要求15所述的三维存算一体化芯片,其特征在于,本层的器件层的退火阻挡层遮盖本层的器件层的功能器件;

17.根据权利要求16所述的三维存算一体化芯片,其特征在于,所述底部器件层的退火阻挡层位于所述底部绝缘层的低介电常数绝缘层内,且位于所述底部绝缘层中低介电常数绝缘层的金属互连线的高度之上。

18.根据权利要求17所述的三维存算一体化芯片,其特征在于,所述上方第一存储层的退火阻挡层位于第一绝缘层的低介电常数绝缘层内,且位于所述第一绝缘层中低介电常数绝缘层的金属互连线的高度之上;

技术总结

本申请实施例提供了一种三维存算一体化芯片,包括:下方器件层;形成在下方器件层上方的上方器件层;其中,下方器件层和上方器件层中一个为具有多个分布式排列计算单元的逻辑功能层,另一个为具有多个分布式排列存储单元的存储层。本申请实施例解决了传统的3D封装存算一体化芯片不能适应芯片的发展方向的技术问题。

技术研发人员:岳丹诚,张耀辉

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!