半导体装置的制作方法

本发明涉及一种半导体装置。

背景技术:

1、已知有在半导体基板的下表面设置有具有多个掺杂浓度峰的缓冲区(或场截止层)的半导体装置(例如参照专利文献1和2)。

2、现有技术文献

3、专利文献1:us2015/0214347

4、专利文献2:wo2018/135448

技术实现思路

1、技术问题

2、在半导体装置中,优选抑制关断时的浪涌电压。

3、技术方案

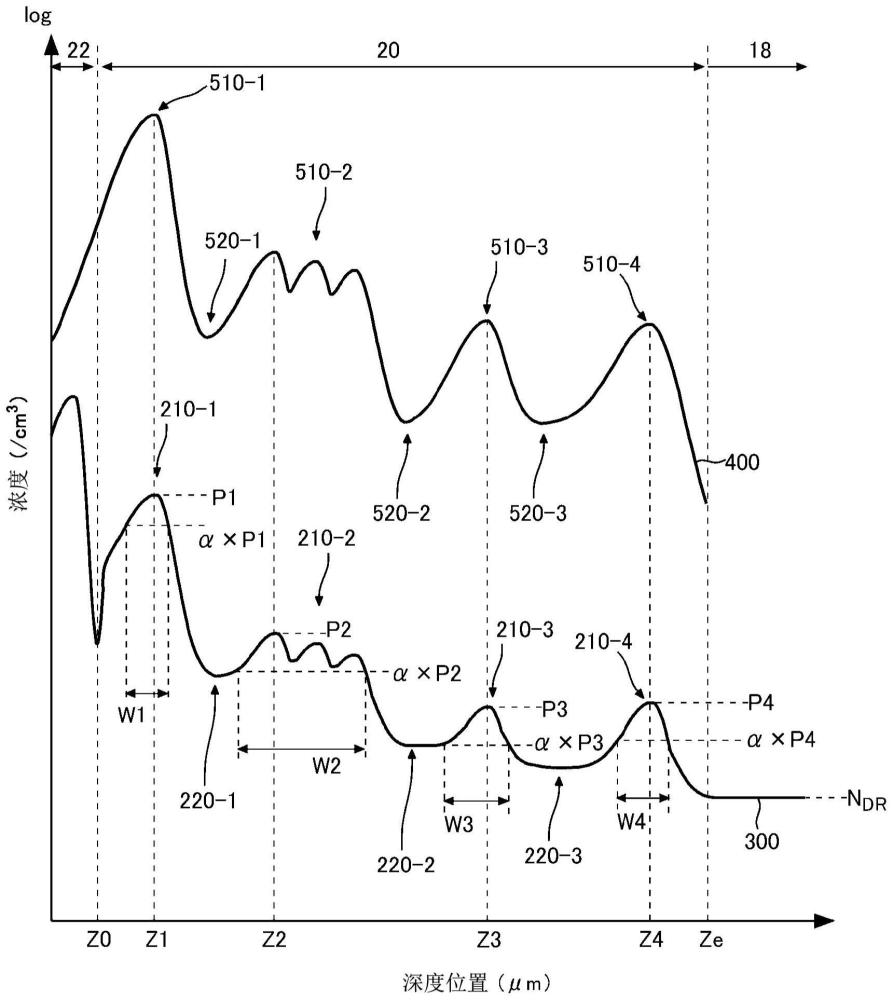

4、为了解决上述问题,在本发明的第一方式中,提供一种半导体装置。半导体装置可以具备半导体基板,其具有上表面和下表面,并设置有第一导电型的漂移区。半导体装置可以具备第一导电型的缓冲区,其设置于所述半导体基板的所述下表面与所述漂移区之间,在所述半导体基板的深度方向上具有三个以上的掺杂浓度峰,且所述缓冲区的浓度比所述漂移区的浓度高。在上述任一半导体装置中,所述三个以上的掺杂浓度峰可以包括距所述半导体基板的所述下表面最远的最深峰和距所述半导体基板的所述下表面第二近的第二峰。在上述任一半导体装置中,在所述深度方向上,所述第二峰的峰宽可以为所述最深峰的峰宽的2倍以上。

5、在上述任一半导体装置中,所述第二峰可以在所述深度方向上包括多个子峰。在上述任一半导体装置中,所述三个以上的掺杂浓度峰可以包括距所述半导体基板的所述下表面的距离第二大的第二深峰。在上述任一半导体装置中,在所述深度方向上相邻的两个所述子峰之间的间隔可以小于所述第二深峰与所述最深峰之间的距离。

6、在上述任一半导体装置中,所述第二峰可以在所述深度方向上包括多个子峰。在上述任一半导体装置中,在所述深度方向上相邻的两个所述子峰之间的间隔可以为所述最深峰的半峰全宽的2倍以下。

7、在上述任一半导体装置中,所述第二峰的所述深度方向上的所述掺杂浓度的分布可以具有多个凹陷部,在各个所述子峰之间配置有一个所述凹陷部。在上述任一半导体装置中,至少一个所述凹陷部的所述掺杂浓度可以大于所述多个子峰的所述掺杂浓度的最大值的0.1倍。

8、在上述任一半导体装置中,所述缓冲区的所述深度方向上的所述掺杂浓度的分布可以具有多个谷部,在各个所述掺杂浓度峰之间配置有一个所述谷部。在上述任一半导体装置中,所述多个谷部可以包括最靠近所述半导体基板的所述下表面的第一谷部。在上述任一半导体装置中,至少一个所述凹陷部的所述掺杂浓度可以高于所述第一谷部的所述掺杂浓度。

9、在上述任一半导体装置中,所述缓冲区的所述深度方向上的所述掺杂浓度的分布可以具有多个谷部,在各个所述掺杂浓度峰之间配置有一个所述谷部。在上述任一半导体装置中,所述多个谷部可以包括最靠近所述半导体基板的所述上表面的最深谷部。在上述任一半导体装置中,至少一个所述凹陷部的所述掺杂浓度可以为所述最深谷部的所述掺杂浓度的2倍以上。

10、在上述任一半导体装置中,所述多个子峰可以包括最靠近所述半导体基板的所述下表面的第一子峰、第二靠近所述下表面的第二子峰、以及第三靠近所述下表面且浓度比所述第二子峰的浓度低的第三子峰。在上述任一半导体装置中,所述第三子峰的掺杂浓度相对于所述第二子峰的掺杂浓度的比率可以小于所述第二子峰的掺杂浓度相对于所述第一子峰的掺杂浓度的比率。

11、在上述任一半导体装置中,所述多个子峰可以包括最靠近所述半导体基板的所述下表面的第一子峰、第二靠近所述下表面的第二子峰、以及第三靠近所述下表面且浓度比所述第二子峰的浓度低的第三子峰。在上述任一半导体装置中,所述第二子峰与所述第三子峰在所述深度方向上的距离可以大于所述第一子峰与所述第二子峰在所述深度方向上的距离。

12、在上述任一半导体装置中,所述三个以上的掺杂浓度峰可以包括最靠近所述半导体基板的所述下表面的第一峰。在上述任一半导体装置中,所述多个子峰可以包括最靠近所述半导体基板的所述下表面的第一子峰。在上述任一半导体装置中,在所述深度方向上相邻的两个所述子峰之间的间隔可以小于所述第一峰与所述第一子峰之间的距离。

13、在上述任一半导体装置中,所述第二峰中的所述子峰的个数可以为四个以下。

14、在上述任一半导体装置中,所述第二峰的所述深度方向上的所述掺杂浓度的分布可以包括一个以上的子峰和一个以上的弯曲部。

15、在上述任一半导体装置中,至少一个所述弯曲部的所述掺杂浓度可以为所述一个以上的子峰的所述掺杂浓度的最大值的0.1倍以上。

16、在上述任一半导体装置中,所述缓冲区的所述深度方向上的所述掺杂浓度的分布可以具有多个谷部,在各个所述掺杂浓度峰之间配置有一个所述谷部。在上述任一半导体装置中,所述多个谷部可以包括最靠近所述半导体基板的所述下表面的第一谷部。在上述任一半导体装置中,至少一个所述弯曲部的所述掺杂浓度可以高于所述第一谷部的所述掺杂浓度。

17、在上述任一半导体装置中,所述缓冲区的所述深度方向上的所述掺杂浓度的分布可以具有多个谷部,在各个所述掺杂浓度峰之间配置有一个所述谷部。在上述任一半导体装置中,所述多个谷部可以包括最靠近所述半导体基板的所述上表面的最深谷部。在上述任一半导体装置中,至少一个所述弯曲部的所述掺杂浓度可以为所述最深谷部的所述掺杂浓度的2倍以上。

18、在上述任一半导体装置中,所述三个以上的掺杂浓度峰可以包括最靠近所述半导体基板的所述下表面的第一峰和第三靠近所述半导体基板的所述下表面的第三峰。在上述任一半导体装置中,所述第二峰的掺杂浓度可以小于所述第一峰的所述掺杂浓度,且大于所述第三峰的所述掺杂浓度。

19、在上述任一半导体装置中,所述第二峰的所述峰宽可以为所述最深峰的所述峰宽的5倍以下。

20、在上述任一半导体装置中,所述三个以上的掺杂浓度峰可以包括最靠近所述半导体基板的所述下表面的第一峰。在上述任一半导体装置中,所述第二峰的所述峰宽可以为所述深度方向上的所述第一峰与所述最深峰之间的距离的0.5倍以下。

21、上述

技术实现要素:

并未列举本发明的全部必要特征。另外,这些特征组的子组合也能够成为发明。

技术特征:

1.一种半导体装置,其特征在于,具备:

2.根据权利要求1所述的半导体装置,其特征在于,

3.根据权利要求1所述的半导体装置,其特征在于,

4.根据权利要求2或3所述的半导体装置,其特征在于,

5.根据权利要求4所述的半导体装置,其特征在于,

6.根据权利要求4所述的半导体装置,其特征在于,

7.根据权利要求2或3所述的半导体装置,其特征在于,

8.根据权利要求2或3所述的半导体装置,其特征在于,

9.根据权利要求2或3所述的半导体装置,其特征在于,

10.根据权利要求2或3所述的半导体装置,其特征在于,

11.根据权利要求1所述的半导体装置,其特征在于,

12.根据权利要求11所述的半导体装置,其特征在于,

13.根据权利要求11或12所述的半导体装置,其特征在于,

14.根据权利要求11或12所述的半导体装置,其特征在于,

15.根据权利要求1至3、11以及12中任一项所述的半导体装置,其特征在于,

16.根据权利要求1至3、11以及12中任一项所述的半导体装置,其特征在于,

17.根据权利要求1至3、11以及12中任一项所述的半导体装置,其特征在于,

技术总结

本发明提供一种抑制浪涌电压的半导体装置。该半导体装置具备第一导电型的缓冲区,其设置于半导体基板的下表面与漂移区之间,在半导体基板的深度方向上具有三个以上的掺杂浓度峰,且该缓冲区的浓度比漂移区的浓度高,三个以上的掺杂浓度峰包括距半导体基板的下表面最远的最深峰和距半导体基板的下表面第二近的第二峰,在深度方向上,第二峰的峰宽为最深峰的峰宽的2倍以上。

技术研发人员:唐本祐树,三塚要

受保护的技术使用者:富士电机株式会社

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!