一种抗单粒子辐射加固VDMOS器件结构

本发明涉及一种垂直双扩散金属-氧化物-半导体场效应晶体管,具体涉及一种抗单粒子辐射加固vdmos器件结构。

背景技术:

1、vdmos(vertical double-diffused mosfet,垂直双扩散金属-氧化物-半导体场效应晶体管)器件广泛应用于航天器电源系统中,起到功率转换和功率变换的作用,为航天器的正常工作提供必需的能源。然而,由于其固有的寄生晶体管和栅氧化层结构,vdmos器件在空间辐射环境中容易发生单粒子烧毁(single event burnout,seb)和单粒子栅穿(single event gate rupture,segr),这两种效应都是破坏性效应,会造成vdmos器件的永久性失效。相关研究表明,vdmos器件在抗总剂量和抗瞬时剂量率方面已经取得了突破性进展,因而vdmos器件抗单粒子辐射能力的不足成为制约其宇航应用的关键因素。

2、为了保证航天器的在轨稳定运行,必须对vdmos器件进行一定的抗单粒子辐射加固设计才能搭载到航天器上,在该过程中,需要同步提升vdmos器件的抗单粒子烧毁和抗单粒子栅穿能力,并且兼顾vdmos器件的电学特性。然而,现有的研究中,往往只关注于vdmos器件的某一种抗单粒子能力(单粒子烧毁或单粒子栅穿)的提升,并且一些加固技术会使得vdmos器件的电学特性产生明显的退化,这显然不满足宇航应用需求。

技术实现思路

1、本发明针对现有vdmos器件抗单粒子辐射加固设计中往往只关注于vdmos器件的某一种抗单粒子能力(单粒子烧毁或单粒子栅穿)的提升,并且一些加固技术会使得vdmos器件的电学特性产生明显的退化这一技术问题,而提出一种抗单粒子辐射加固vdmos器件结构,其是基于倒掺杂体区和高k栅介质层的抗单粒子辐射加固vdmos器件结构,该结构可以在同步提升vdmos器件的抗单粒子烧毁和抗单粒子栅穿能力的同时,保持vdmos器件的漏-源击穿电压、阈值电压、特征导通电阻等关键电学参数不会发生明显的退化。

2、本发明的技术方案如下:

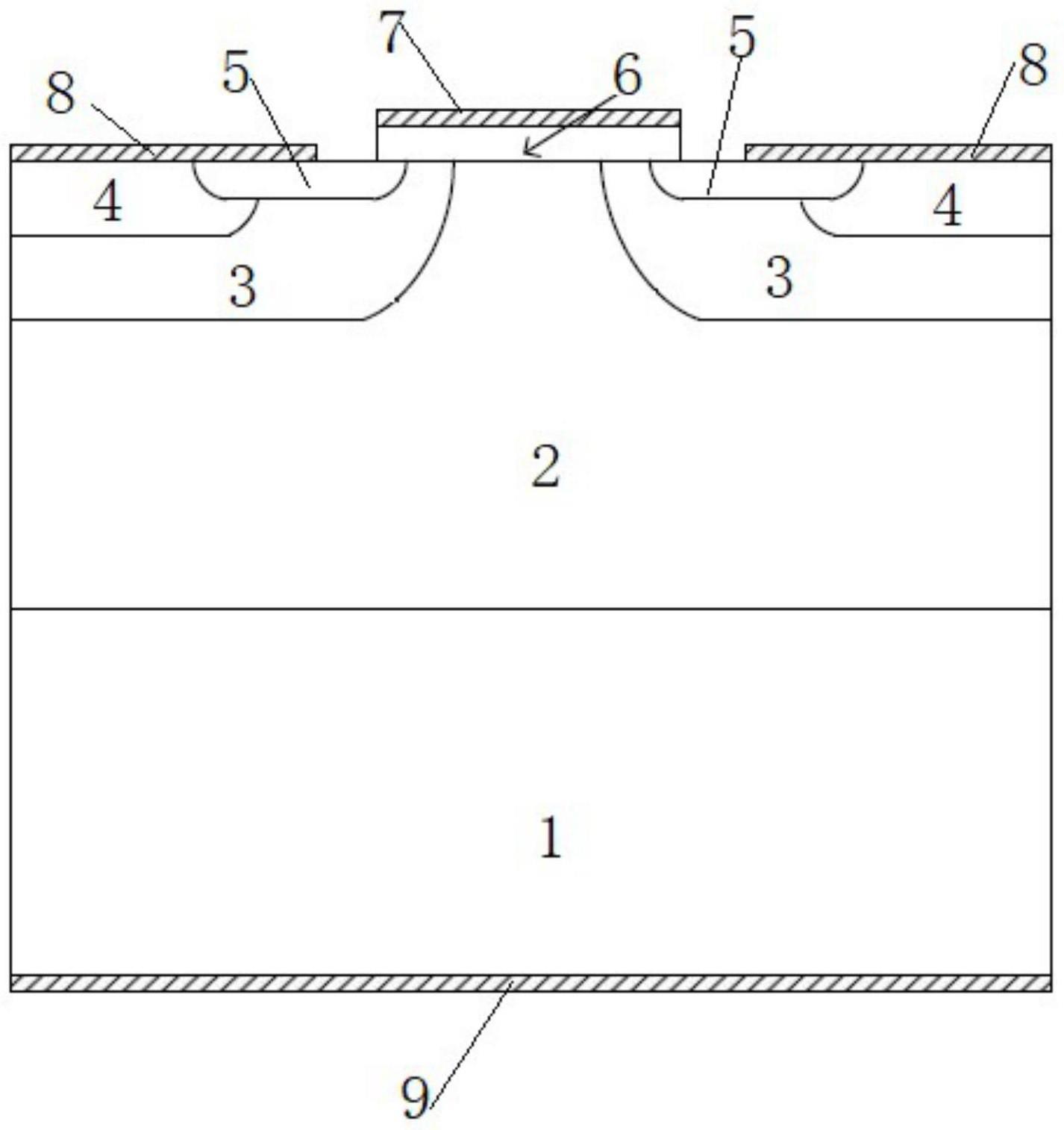

3、一种抗单粒子辐射加固vdmos器件结构,包括衬底和位于衬底上方的外延层,其特殊之处在于:

4、还包括倒掺杂体区、接触区、源区、高k栅介质层、多晶硅栅、源极金属接触和漏极金属接触;

5、所述高k栅介质层位于外延层的上方中部,多晶硅栅位于高k栅介质层的上方,用作栅电极;倒掺杂体区位于外延层内的上表面的两侧,源区位于外延层内的上表面且位于倒掺杂体区内,倒掺杂体区和源区分布在多晶硅栅两侧,两者在多晶硅栅下方的横向结深之差形成沟道,接触区位于外延层内的上表面且位于倒掺杂体区内,并与源区邻接,分布在器件两侧,源极金属接触位于接触区上方并覆盖部分源区,漏极金属接触位于衬底下表面;

6、所述衬底、外延层、源区均为n型掺杂;

7、所述倒掺杂体区和接触区均为p型掺杂。

8、进一步地,所述高k栅介质层采用高k材料制备。

9、进一步地,所述源区的纵向结深为0.1μm~1μm;

10、所述倒掺杂体区的纵向结深为2μm~7μm;

11、所述接触区的纵向结深为1μm~1.5μm。

12、进一步地,所述衬底的掺杂浓度、体区、接触区以及源区的掺杂浓度大于外延层的掺杂浓度;

13、所述倒掺杂体区的峰值掺杂浓度大于沟道区的掺杂浓度。

14、进一步地,所述源区的表面峰值掺杂浓度为1e20cm-3;

15、所述接触区的表面峰值掺杂浓度为1e19cm-3。

16、进一步地,所述衬底的电阻率为0.002ω·cm~0.005ω·cm。

17、进一步地,所述衬底的厚度为280μm±20μm。

18、进一步地,所述多晶硅栅为n型掺杂,掺杂浓度为1e20cm-3。

19、本发明的有益效果:

20、1、本发明中,倒掺杂体区是采用倒掺杂分布,沟道区的掺杂浓度较低,而倒掺杂体区内部掺杂浓度较高(倒掺杂体区的峰值掺杂浓度大于沟道区的掺杂浓度),可同时满足高驱动电流和抑制寄生晶体管导通的要求;此外,采用高k材料替代二氧化硅材料作为栅介质层,在相同栅电容条件下高k栅介质层能够做得更厚,从而提升了vdmos器件的抗单粒子栅穿能力。

21、2、本发明所提出的基于倒掺杂体区和高k栅介质层的抗单粒子辐射加固vdmos器件结构能够在同步提升vdmos器件的抗单粒子烧毁和抗单粒子栅穿能力的情况下,保持vdmos器件的漏-源击穿电压、阈值电压、特征导通电阻等关键电学参数不会发生明显的退化,从而更好地满足宇航电子系统对于vdmos器件的电学性能和抗辐射性能的指标需求。

技术特征:

1.一种抗单粒子辐射加固vdmos器件结构,包括衬底(1)和位于衬底(1)上方的外延层(2),其特征在于:

2.根据权利要求1所述的一种抗单粒子辐射加固vdmos器件结构,其特征在于:所述高k栅介质层(6)采用高k材料制备。

3.根据权利要求2所述的一种抗单粒子辐射加固vdmos器件结构,其特征在于:

4.根据权利要求3所述的一种抗单粒子辐射加固vdmos器件结构,其特征在于:

5.根据权利要求4所述的一种抗单粒子辐射加固vdmos器件结构,其特征在于:

6.根据权利要求5所述的一种抗单粒子辐射加固vdmos器件结构,其特征在于:

7.根据权利要求6所述的一种抗单粒子辐射加固vdmos器件结构,其特征在于:

8.根据权利要求1-7任一所述的一种抗单粒子辐射加固vdmos器件结构,其特征在于:

技术总结

本发明涉及一种抗单粒子辐射加固VDMOS器件结构;针对现有设计往往只关注于VDMOS器件的某一种抗单粒子能力的提升,并且一些加固技术会使得VDMOS器件的电学特性产生明显退化的问题;包括衬底和位于衬底上方的外延层;高K栅介质层位于外延层的上方中部,多晶硅栅位于高K栅介质层的上方;倒掺杂体区位于外延层内上表面的两侧,源区位于外延层内上表面且位于倒掺杂体区内,倒掺杂体区和源区分布在多晶硅栅两侧,两者横向结深之差形成沟道,接触区位于外延层内的上表面且位于倒掺杂体区内,并与源区邻接,源极金属接触位于接触区上方并覆盖部分源区,漏极金属接触位于衬底下表面;衬底、外延层、源区为N型掺杂;倒掺杂体区和接触区为P型掺杂。

技术研发人员:廖新芳,王晨,刘毅,徐长卿,杨银堂

受保护的技术使用者:西安电子科技大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!