阵列基板的制备方法、阵列基板以及显示面板与流程

本公开涉及显示,特别涉及一种阵列基板的制备方法、阵列基板以及显示面板。

背景技术:

1、微米级发光二极管(micro light emitting diode,micro-led)具有分辨率高、亮度高、寿命长和色域广等明显优势,在增强现实(augmented reality,ar)、虚拟现实(virtual reality,vr)和微型显示等领域中逐渐得到普及和应用。由micro-led形成的像素单元,在制备过程中通常使用光刻胶,通过对光刻胶图案化,然后刻蚀出相应图形区域的像素单元。

2、由于上述制备过程中使用光刻胶,后续要将光刻胶去除,如果光刻胶不能去除干净,将会影响像素单元的电学接触,导致开启电压变大等电学问题。另外,在光刻胶去除的过程中,容易对像素单元的侧壁造成损伤,影响像素单元的发光效率。

技术实现思路

1、为了解决上述技术问题或者至少部分地解决上述技术问题,本公开提供了一种阵列基板的制备方法、阵列基板以及显示面板,解决了由于采用光刻胶,造成像素单元的电学接触受到影响,导致开启电压变大等电学问题,以及对像素单元的侧壁造成损伤,影响像素单元的发光效率的问题。

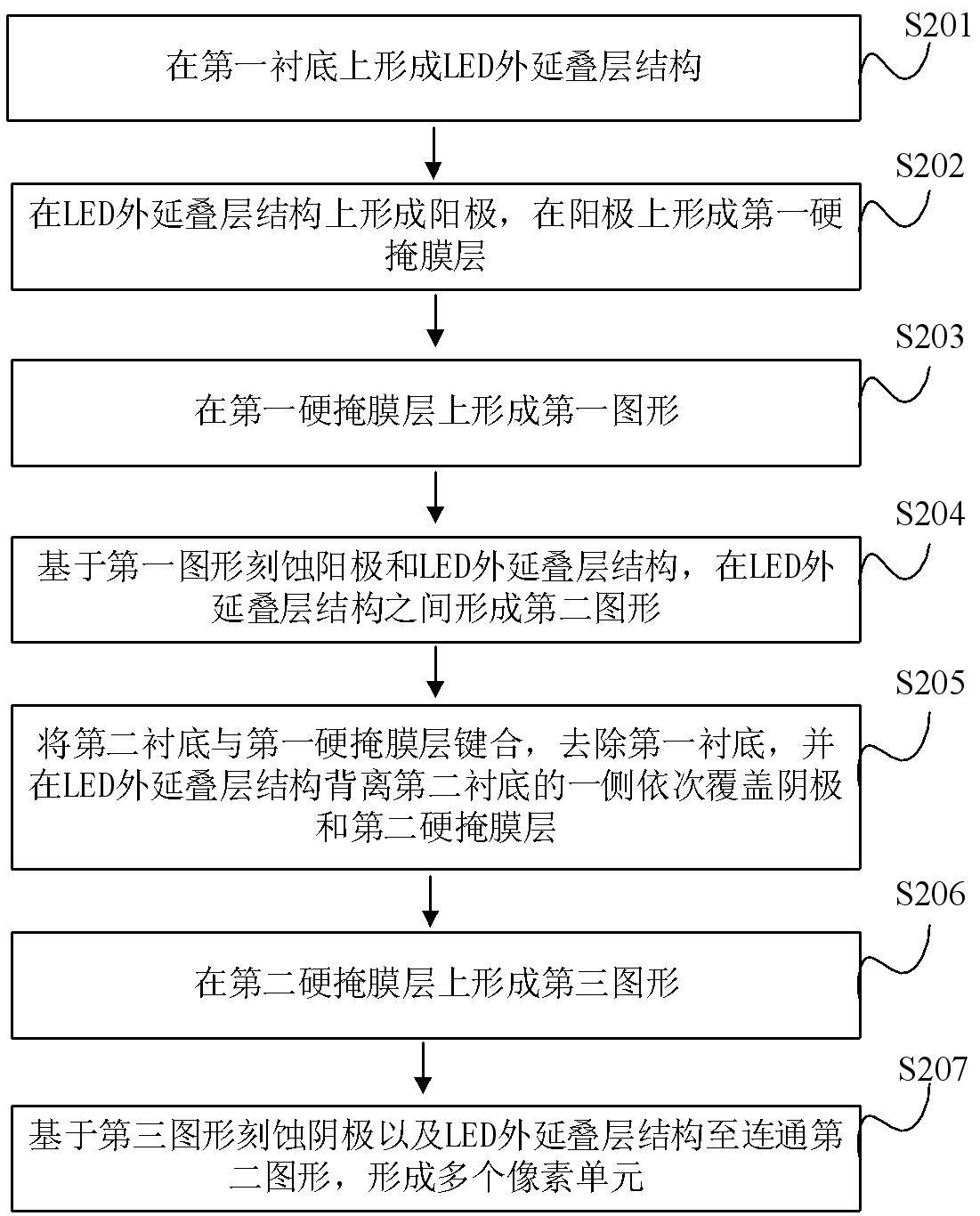

2、第一方面,本公开提供了一种阵列基板的制备方法,包括:

3、在第一衬底上形成led外延叠层结构;

4、在所述led外延叠层结构上形成阳极,在所述阳极上形成第一硬掩膜层;

5、在所述第一硬掩膜层上形成第一图形;

6、基于所述第一图形刻蚀所述阳极和所述led外延叠层结构,在所述led外延叠层结构之间形成第二图形;

7、将第二衬底与所述第一硬掩膜层键合,去除所述第一衬底,并在所述led外延叠层结构背离所述第二衬底的一侧依次覆盖阴极和第二硬掩膜层;

8、在所述第二硬掩膜层上形成第三图形;

9、基于所述第三图形刻蚀所述阴极以及所述led外延叠层结构至连通所述第二图形,形成多个像素单元。

10、在一些实施例中,在所述led外延叠层结构上形成阳极,在所述阳极上形成第一硬掩膜层,包括:

11、通过物理气相沉积法在所述led外延叠层结构上沉积所述阳极;

12、通过化学气相沉积法在所述阳极上沉积所述第一硬掩膜层。

13、在一些实施例中,在所述第一硬掩膜层上形成第一图形,包括:

14、在所述第一硬掩膜层覆盖光刻胶层;

15、通过曝光显影,保留预设区域的光刻胶层;

16、刻蚀所述第一硬掩膜层,在所述第一硬掩膜层上形成第一图形;

17、去除所述光刻胶层。

18、在一些实施例中,在所述第二硬掩膜层上形成第三图形,包括:

19、在所述第二硬掩膜层覆盖光刻胶层;

20、通过曝光显影,保留预设区域的光刻胶层;

21、刻蚀所述第二硬掩膜层,在所述第二硬掩膜层上形成第三图形;

22、去除所述光刻胶层。

23、在一些实施例中,形成所述第一硬掩膜层和所述第二硬掩膜层的材料包括氮化硅和氧化硅中的至少一种。

24、在一些实施例中,所述阳极的材料包括氮化钛和氮化钽中的至少一种;所述阴极的材料包括氧化铟锡。

25、第二方面,本公开还提供了一种阵列基板,包括:

26、第二衬底以及所述第二衬底上阵列排布的像素单元,相邻所述像素单元之间间隔预设距离;

27、第一硬掩膜层和第二硬掩膜层,所述像素单元的阳极通过所述第一硬掩膜层与所述第二衬底连接,所述像素单元的阴极与所述第二硬掩膜层连接。

28、在一些实施例中,所述像素单元包括电子传输层、发光层和空穴传输层。

29、在一些实施例中,所述阳极作为反射层。

30、第三方面,本公开还提供了一种显示面板,包括如第二方面所述的阵列基板。

31、本公开实施例提供的阵列基板的制备方法包括:在第一衬底上形成led外延叠层结构;在led外延叠层结构上形成阳极,在阳极上形成第一硬掩膜层;在第一硬掩膜层上形成第一图形;基于第一图形刻蚀阳极和led外延叠层结构,在led外延叠层结构之间形成第二图形;将第二衬底与第一硬掩膜层键合,去除第一衬底,并在led外延叠层结构背离第二衬底的一侧依次覆盖阴极和第二硬掩膜层;在第二硬掩膜层上形成第三图形;基于第三图形刻蚀阴极以及led外延叠层结构至连通第二图形,形成多个像素单元。由此,通过在阳极上覆盖第一硬掩膜层,在阴极上覆盖第二硬掩膜层,将第一硬掩膜层和第二硬掩膜层作为保护层进行图案化,在形成像素单元后,无需去除第一硬掩膜层和第二硬掩膜层,避免了相关技术中使用光刻胶层,后续将光刻胶层去除,若光刻胶不能去除干净,例如空穴传输层上残留有光刻胶,在空穴传输层上制备阳极时,将会影响制备的像素单元的电学接触,导致开启电压变大等电学问题。以及避免了相关技术中在光刻胶去除的过程中,使用显影液,显影液接触刚刻蚀形成的像素单元的侧壁,对像素单元的侧壁造成损伤的问题,从而影响像素单元的发光效率。由此,本公开实施例提供的技术方案,解决了由于采用光刻胶,造成像素单元的电学接触受到影响,导致开启电压变大等电学问题,以及对像素单元的侧壁造成损伤,影响像素单元的发光效率的问题。

技术特征:

1.一种阵列基板的制备方法,其特征在于,包括:

2.根据权利要求1所述的阵列基板的制备方法,其特征在于,在所述led外延叠层结构上形成阳极,在所述阳极上形成第一硬掩膜层,包括:

3.根据权利要求1所述的阵列基板的制备方法,其特征在于,在所述第一硬掩膜层上形成第一图形,包括:

4.根据权利要求1所述的阵列基板的制备方法,其特征在于,在所述第二硬掩膜层上形成第三图形,包括:

5.根据权利要求1所述的阵列基板的制备方法,其特征在于,形成所述第一硬掩膜层和所述第二硬掩膜层的材料包括氮化硅和氧化硅中的至少一种。

6.根据权利要求1所述的阵列基板的制备方法,其特征在于,所述阳极的材料包括氮化钛和氮化钽中的至少一种;所述阴极的材料包括氧化铟锡。

7.一种阵列基板,其特征在于,包括:

8.根据权利要求7所述的阵列基板,其特征在于,所述像素单元包括电子传输层、发光层和空穴传输层。

9.根据权利要求7所述的阵列基板,其特征在于,所述阳极作为反射层。

10.一种显示面板,其特征在于,包括如权利要求7-9任一项所述的阵列基板。

技术总结

本公开涉及显示技术领域,特别涉及一种阵列基板的制备方法、阵列基板以及显示面板。阵列基板的制备方法包括形成LED外延叠层结构;在LED外延叠层结构上依次形成阳极和第一硬掩膜层;在第一硬掩膜层上形成第一图形;在LED外延叠层结构形成第二图形;将第二衬底与第一硬掩膜层键合,去除第一衬底并在LED外延叠层结构背离第二衬底的一侧依次覆盖阴极和第二硬掩膜层;在第二硬掩膜层上形成第三图形;刻蚀阴极以及LED外延叠层结构至连通第二图形形成多个像素单元。本公开的技术方案,解决了由于采用光刻胶造成像素单元的电学接触受到影响,导致开启电压变大等电学问题,以及对像素单元的侧壁造成损伤,影响像素单元的发光效率的问题。

技术研发人员:温海键,张羽,岳大川,蔡世星,李小磊,伍德民

受保护的技术使用者:季华实验室

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!