半导体结构及其制备方法与流程

本申请涉及半导体,具体地,涉及一种半导体结构及其制备方法。

背景技术:

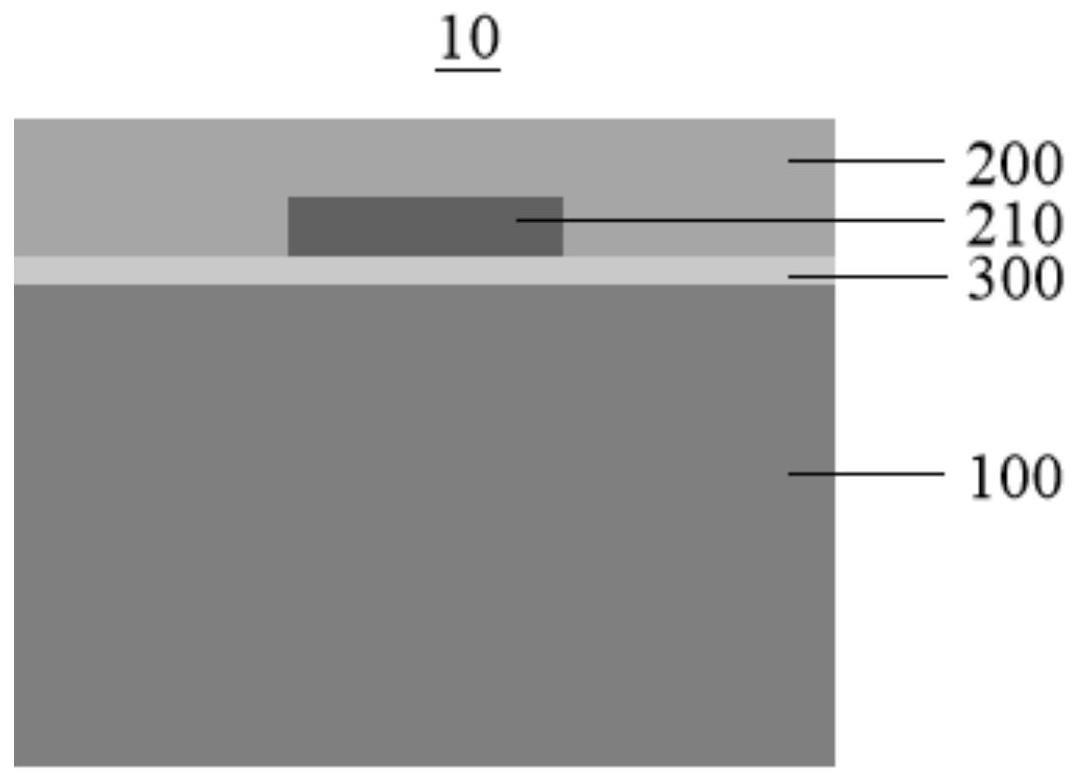

1、如图1所示,目前半导体结构中的埋氧层是遍布整层晶圆的,即在顶层硅下方具有整层的埋氧层,而晶体管等功能器件一般位于顶层硅表面。

2、晶体管在工作时会产生碰撞电离效应:即晶体管在漏端电压等大电压的作用下产生强电场,载流子在该强电场的作用下轰击半导体中的原子,从而产生不期望的电子和空穴对,产生的电子和空穴对继续碰撞原子从而产生更多的电子和空穴对。由于整片埋氧层的存在,在碰撞电离效应中产生的电子和空穴对只能沉积到顶层硅中,从而对处于顶层硅表面的器件造成性能影响。

3、因此,目前亟需一种对顶层硅表面器件性能影响较弱的半导体结构。

技术实现思路

1、为了解决上述技术问题,本申请实施例中提供了一种半导体结构及其制备方法。

2、本申请实施例的第一个方面,提供了一种半导体结构,包括:

3、由下及上堆叠的支撑衬底和顶层基体;其中所述顶层基体中包含多个相互独立,且间隔设置的埋氧层单元;各所述埋氧层单元的厚度均小于所述顶层基体的厚度;所述顶层基体用于制备功能器件;所述顶层基体由单晶半导体材料制成。

4、在本申请一个可选实施例中,该半导体结构还包括:

5、富陷阱层,铺设于所述支撑衬底与所述顶层基体之间,且与各所述埋氧层单元相贴合。

6、在本申请一个可选实施例中,所述富陷阱层由多晶硅材料或者非晶硅材料制成。

7、在本申请一个可选实施例中,所述富陷阱层的厚度为200纳米~2微米。

8、在本申请一个可选实施例中,所述支撑衬底由高阻硅材料制成。

9、本申请实施例的第二个方面,提供了一种半导体结构的制备方法,用于制备如上任一项所述的半导体结构,该方法包括:

10、制备第一晶圆;其中,所述第一晶圆包括初始基体层,以及在所述初始基体层中设置的多个相互独立,且间隔设置的埋氧层单元;各所述埋氧层单元的厚度均小于所述顶层基体的厚度;所述初始基体层用于制备功能器件;所述初始基体层由单晶半导体材料制成;

11、制备第二晶圆;其中,所述第二晶圆包含支撑衬底;

12、将所述第一晶圆与所述第二晶圆进行键合,得到中间半导体结构;其中,所述中间半导体结构中的所述埋氧层单元与所述支撑衬底相贴合;

13、对所述中间半导体结构进行修正处理,得到目标半导体结构;其中,所述目标半导体结构包括:由下及上堆叠的支撑衬底和顶层基体;其中,所述顶层基体中包含多个相互独立,且间隔设置的埋氧层单元。

14、在本申请一个可选实施例中,在所述将所述第一晶圆与所述第二晶圆进行键合,得到中间半导体结构之前,该方法还包括:

15、在所述第二晶圆表面形成富陷阱层;

16、对应的,所述将所述第一晶圆与所述第二晶圆进行键合,得到中间半导体结构,包括:

17、将所述第一晶圆与所述第二晶圆中的所述富陷阱层表面键合,得到所述中间半导体结构;其中,所述中间半导体结构中的所述埋氧层单元与所述富陷阱层相贴合。

18、在本申请一个可选实施例中,该半导体结构的制备方法还包括:

19、将所述富陷阱层表面的粗糙度处理至预设目标值。

20、在本申请一个可选实施例中,所述对所述中间半导体结构进行修正处理,得到目标半导体结构,包括:

21、将所述中间半导体结构的所述初始基体层研磨至目标厚度,得到所述目标半导体结构。

22、在本申请一个可选实施例中,所述制备第一晶圆,包括:

23、采用浅沟槽工艺制备图形化的第一初始晶圆;

24、根据预设投影射程位置在所述第一初始晶圆中注入氢离子,得到所述第一晶圆;

25、对应的,所述对所述中间半导体结构进行修正处理,得到目标半导体结构,包括:

26、将所述中间半导体结构从预设投影射程位置剥离所述第一晶圆中的部分初始基体层,得到包含剩余初始基体层的所述目标半导体结构。

27、在本申请一个可选实施例中,所述采用浅沟槽工艺制备图形化的第一初始晶圆,包括:

28、在所述初始基体层表面制备第一氧化硅层;

29、在所述第一氧化硅层表面制备氮化硅层;

30、在所述氮化硅层刻蚀凹槽;其中,所述凹槽贯穿所述第一氧化硅层并延伸至所述初始基体层;

31、在刻蚀后的晶圆表面形成第二氧化硅层;

32、对当前晶圆进行研磨处理,得到表面平整的所述第一初始晶圆。

33、在本申请一个可选实施例中,在所述氮化硅层刻蚀凹槽之后,该方法还包括:

34、基于氢氟酸溶液对刻蚀后的晶圆进行漂洗。

35、在本申请一个可选实施例中,所述在刻蚀后的晶圆表面形成第二氧化硅层,包括:

36、基于热氧化工艺在刻蚀后的晶圆表面形成第一厚度的氧化硅层;

37、基于硅酸乙酯工艺在形成的氧化硅层表面生长第二厚度的氧化硅层,得到所述第二氧化硅层;其中,所述第二厚度大于所述第一厚度。

38、本申请实施例提供的半导体结构,顶层基体中的各埋氧层单元相互独立,且相互间隔设置,第一方面,各个埋氧层单元之间存在间隔空隙,一旦处于顶层基体上晶体管产生碰撞电离效应,在该碰撞电离效应中产生的电子和空穴对可以沿该间隔空隙引导至支撑衬底,从而避免产生的电子和空穴积累在顶层基体中而对顶部的晶体管等顶部功能器件造成性能影响,提高晶体管等器件的鲁棒性;第二方面,传统埋氧层覆盖整片晶圆,对顶部的晶体管等器件的导热性产生影响,本申请实施例中的各埋氧层单元相互独立,且相互间隔设置,各个埋氧层单元之间存在间隔空隙,可以提供散热空间,使得顶部功能器件产生的焦耳热流向支撑衬底,抑制器件的自加热效应,提高半导体结构的散热性能;第三方面,传统埋氧层覆盖整片晶圆,大面积氧化物的存在容易产生浮体效应(导致器件的阈值电压发生漂移,工作状态不稳定),本申请实施例中的各埋氧层单元相互独立,且相互间隔设置,各个埋氧层单元之间单独存在,从而可以抑制,甚至消除浮体效应,进而实现稳定顶部功能器件阈值电压的效果。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,还包括:

3.根据权利要求2所述的半导体结构,其特征在于,所述富陷阱层由多晶硅材料或者非晶硅材料制成。

4.根据权利要求2所述的半导体结构,其特征在于,所述富陷阱层的厚度为200纳米~2微米。

5.根据权利要求1所述的半导体结构,其特征在于,所述支撑衬底由高阻硅材料制成。

6.一种半导体结构的制备方法,其特征在于,用于制备权利要求1-5任一项所述的半导体结构,所述方法包括:

7.根据权利要求6所述的半导体结构的制备方法,其特征在于,在所述将所述第一晶圆与所述第二晶圆进行键合,得到中间半导体结构之前,所述方法还包括:

8.根据权利要求7所述的半导体结构的制备方法,其特征在于,所述方法还包括:

9.根据权利要求6所述的半导体结构的制备方法,其特征在于,所述对所述中间半导体结构进行修正处理,得到目标半导体结构,包括:

10.根据权利要求6所述的半导体结构的制备方法,其特征在于,所述制备第一晶圆,包括:

11.根据权利要求10所述的半导体结构的制备方法,其特征在于,所述采用浅沟槽工艺制备图形化的第一初始晶圆,包括:

12.根据权利要求11所述的半导体结构的制备方法,其特征在于,在所述在所述氮化硅层刻蚀凹槽之后,所述方法还包括:

13.根据权利要求11所述的半导体结构的制备方法,其特征在于,所述在刻蚀后的晶圆表面形成第二氧化硅层,包括:

技术总结

本申请实施例提供了一种半导体结构及其制备方法,涉及半导体技术领域。该半导体结构包括:由下及上堆叠的支撑衬底和顶层基体;其中所述顶层基体中包含多个相互独立,且间隔设置的埋氧层单元;各所述埋氧层单元的厚度均小于所述顶层基体的厚度;所述顶层基体用于制备功能器件。各个埋氧层单元相互独立,且间隔设置,一旦处于顶层基体上晶体管等功能器件产生碰撞电离效应,在该碰撞电离效应中产生的电子和空穴对可以沿埋氧层单元之间的间隔空隙流到支撑衬底,从而避免产生的电子和空穴积累在顶层基体中而对顶部的晶体管等顶部功能器件造成性能影响,提高晶体管等功能器件的鲁棒性。

技术研发人员:岳丹诚,蒋天浩

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!