一种基于重离子掺杂的亚微米超结制造方法与流程

本发明属于半导体工艺制造,涉及一种基于重离子掺杂的亚微米超结制造方法。

背景技术:

1、目前,功率半导体器件已成为现代工业控制和国防装备的基础之一,其应用领域越来越广。纵向双扩散金属氧化物半导体场效应晶体管(vdmos)是功率处理与转换的主力器件之一,具有输入阻抗高、开关速度快、损耗小、驱动功率小、频率特性好等优点,已成为目前应用最为广泛的新型功率器件。其中,超结vdmos保持传统功率mosfet器件优秀性能的同时,更具备了较低导通损耗这一独特优势。但是由于常规的掺磷的n型区与掺硼的n型区在高温热过程,例如外延温度1000度时,由于杂质的互扩散导致超结器件的条宽不能缩小,浓度无法进一步提高,比导通电阻较大。如何在工艺制造中提高超结vdmos的掺杂浓度,减小元胞宽度,在保证耐压的同时进一步降低比导通电阻,是进一步发展要解决的核心问题。

2、本发明针对背景技术的不足之处,提出一种基于重离子掺杂的亚微米超结制造方法。本发明的核心思想是解决超结器件在高温外延时,超结元胞宽度由于磷、硼杂质的扩散系数高导致互扩散严重,为了保持高耐压,不得不增大条宽,但是导致比导通电阻降低的问题。本发明旨在给出一种基于重离子掺杂的亚微米超结制造方法,p型区采用重离子掺杂,降低扩散系数和比导通电阻。原理是由于重离子与轻离子的扩散系数不同,重离子具有扩散系数低、补偿小的特点,且能在保持耐压一定的条件下提高掺杂浓度,降低比导通电阻。

技术实现思路

1、为实现上述发明目的,本发明技术方案如下:

2、一种基于重离子掺杂的亚微米超结制造方法,所述制造方法包括如下步骤:

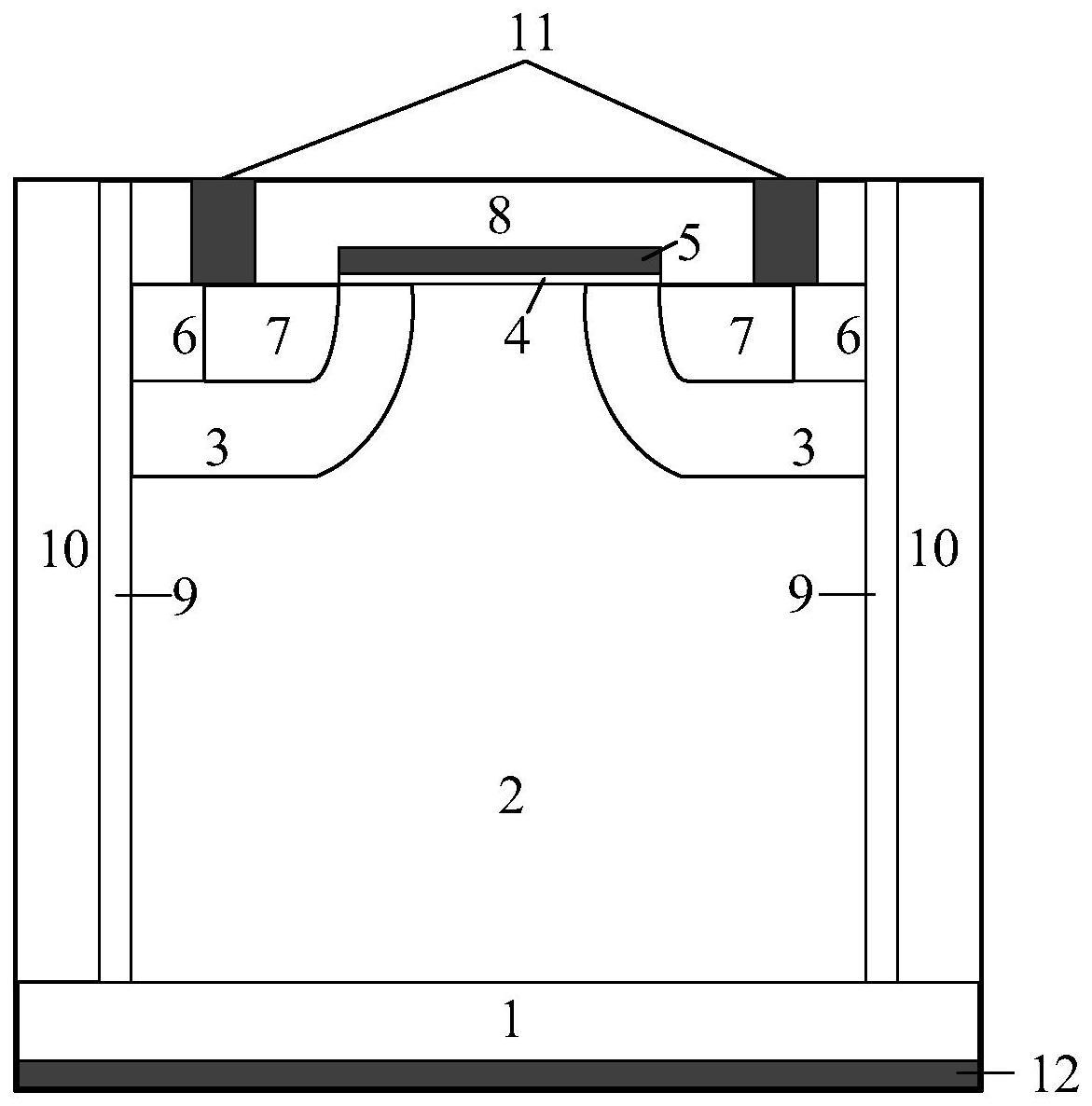

3、步骤1:选择具有第二导电类型重掺杂区(1)的衬底片,外延形成第二导电类型柱区(2)形成超结的n型区;

4、步骤2:在第二导电类型柱区(2)表面通过离子注入并推结形成第一导电类型阱区(3);

5、步骤3:在表面制备第一介质栅氧化层(4)和栅电极(5);

6、步骤4:通过自对准工艺,在第一导电类型阱区(3)表面离子注入并推结形成第一导电类型重掺杂区(6)和第二导电类型重掺杂区(7);

7、步骤5:在表面淀积介质并通过cmp工艺平坦化形成第二介质氧化层(8);

8、步骤6:对第二介质氧化层(8)两侧进行刻蚀,之后以表面未刻蚀的第二介质氧化层作为硬掩膜版,对第二导电类型柱区(2)进行沟槽刻蚀,之后侧壁注入第一导电类型重离子,形成第一导电类型柱区(9);

9、步骤7:通过淀积工艺将侧壁注入后的留下的孔填满第三介质氧化层(10);

10、步骤8:在器件上表面打孔并注入金属形成源电极(11);

11、步骤9:背面金属化形成漏电极(12)。

12、作为优选方式,步骤6中的第一导电类型重离子可以是镓,铟,铊。基于重离子扩散系数小,采用重离子可以减小杂质的扩散,优化器件电学参数。

13、作为优选方式,步骤6中,沟槽刻蚀采用高深宽比的刻槽工艺,使步骤7中的孔尽可能的窄,再通过侧壁注入形成的第一导电类型柱区(9)宽度0.1~0.5微米,实现了亚微米级超结的形成。

14、作为优选方式,步骤6与步骤7形成的第一导电类型柱区(9)与第三介质氧化层(10)的形成可以在步骤4形成第一导电类型重掺杂区(6)和第二导电类型重掺杂区(7)之前。

15、作为优选方式,步骤7中进行填孔的材料可以是多晶硅、二氧化硅介质或者高k介质。

16、作为优选方式,步骤6中的第一导电类型柱区(9)也可以高能离子注入形成。通过在表面淀积20μm的多晶硅作为硬掩膜,然后在多晶硅上刻孔,多次高能离子注入重离子形成第一导电类型柱区(9)。

17、作为优选方式,在步骤6沟槽刻蚀时不刻蚀到第二导电类型重掺杂区(1)表面,在所述第二导电类型柱区(2)两侧形成半超结结构和半超结半导体器件。

18、作为优选方式,步骤6槽内注入重离子也可以在槽底和侧壁一起注入,也可以先在槽底注入低掺杂的第一导电类型离子,之后在侧壁注入重离子。

19、作为优选方式,二极管、igbt等功率半导体器件均可采用该制造方法。

20、作为优选方式,该制造方法可运用在碳化硅、氮化镓等第三代半导体器件。

21、本发明的有益效果为:提出一种基于重离子掺杂的亚微米超结制造方法,解决超结在高温外延时,超结元胞宽度由于磷、硼杂质的扩散系数高导致互扩散严重,为了保持高耐压,不得不增大条宽,但是导致比导通电阻降低。解决途径之一是采取特殊工艺降低外延温度,但是会带来成本极大提高。本发明旨在提出一种基于重离子掺杂的亚微米超结制造方法,从采用重离子来降低扩散系数的方面解决该问题。本发明提出的重离子掺杂的亚微米超结,p型区采用重离子进行侧壁注入,形成条宽较窄的高浓度p柱,且通过用多晶硅与介质进行填孔。由于重离子相较于轻离子(磷、硼)的扩散系数小的多,在形成超结后,在p型区和n型区的交界界面处重离子具有补偿小的特点,能够提高界面处的掺杂浓度,降低比导通电阻。且介质与多晶硅在孔中的加入能优化超结的体内电场,该制造方法能够在保持耐压优化的条件下提高掺杂浓度,降低比导通电阻。

技术特征:

1.一种基于重离子掺杂的亚微米超结制造方法,其特征是,所述制造方法包括如下步骤:

2.根据权利要求1所述的一种基于重离子掺杂的亚微米超结制造方法,其特征在于:步骤6中的第一导电类型重离子可以是镓,铟,铊。基于重离子扩散系数小,采用重离子可以减小杂质的扩散,优化器件电学参数。

3.根据权利要求1所述的一种基于重离子掺杂的亚微米超结制造方法,其特征在于:步骤6中,沟槽刻蚀采用高深宽比的刻槽工艺,使步骤7中的孔尽可能的窄,再通过侧壁注入形成的第一导电类型柱区(9)宽度0.1~0.5微米,实现了亚微米级超结的形成。

4.根据权利要求1所述的一种基于重离子掺杂的亚微米超结制造方法,其特征在于:步骤6与步骤7形成的第一导电类型柱区(9)与第三介质氧化层(10)的形成可以在步骤4形成第一导电类型重掺杂区(6)和第二导电类型重掺杂区(7)之前。

5.根据权利要求1所述的一种基于重离子掺杂的亚微米超结制造方法,其特征在于:步骤7中进行填孔的材料可以是多晶硅、二氧化硅介质或者高k介质。

6.根据权利要求1所述的一种基于重离子掺杂的亚微米超结制造方法,其特征在于:步骤6中的第一导电类型柱区(9)也可以高能离子注入形成。通过在表面淀积20μm的多晶硅作为硬掩膜,然后在多晶硅上刻孔,多次高能离子注入重离子形成第一导电类型柱区(9)。

7.根据权利要求1所述的一种基于重离子掺杂的亚微米超结制造方法,其特征在于:在步骤6沟槽刻蚀时不刻蚀到第二导电类型重掺杂区(1)表面,在所述第二导电类型柱区(2)两侧形成半超结结构和半超结半导体器件。

8.根据权利要求1所述的一种基于重离子掺杂的亚微米超结制造方法,其特征在于:步骤6槽内注入重离子也可以在槽底和侧壁一起注入,也可以先在槽底注入低掺杂的第一导电类型离子,之后在侧壁注入重离子。

9.根据权利要求1所述的一种基于重离子掺杂的亚微米超结制造方法,其特征在于:二极管、igbt等功率半导体器件均可采用该制造方法。

10.根据权利要求1所述的一种基于重离子掺杂的亚微米超结制造方法,其特征在于:该制造方法可运用在碳化硅、氮化镓等第三代半导体器件。

技术总结

本发明涉及种一种基于重离子掺杂的亚微米超结制造方法,器件结构包括漏电极、栅电极、源电极,第一导电类型重掺杂区、第二导电类型重掺杂区,第二导电类型柱区、第一导电类型柱区,第一导电类型阱区,第一介质栅氧化层、第二介质氧化层,第三介质氧化层。在N柱与器件表面结构形成后,用介质层作为硬掩膜版挖槽,在槽中用第一导电类型重离子进行侧壁注入形成亚微米级条宽的P柱,之后用多晶硅或介质进行填孔。由于重离子的扩散系数小,能够提高界面处的掺杂浓度,降低比导通电阻。且介质或多晶硅在孔中的加入能优化超结的体内电场,该制造方法能够在保持耐压优化的条件下提高掺杂浓度,降低比导通电阻。

技术研发人员:张娅林,章文通

受保护的技术使用者:无锡用芯微电子科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!