一种具有不同栅极氧化厚度的水平分裂栅SiCVMOS及制备方法与流程

本发明涉及半导体,具体涉及一种具有不同栅极氧化厚度的水平分裂栅sic vmos及制备方法。

背景技术:

1、相较于以硅为代表的第一代半导体材料和以砷化镓为代表的第二代半导体材料,第三代半导体材料碳化硅具有带隙宽、击穿场强高、热导率高、饱和电子迁移速率高、物理化学性能稳定等特性,可适用于高温,高频,大功率和极端环境。sic mosfet是早已充分实现商品化的碳化硅器件。碳化硅具有更大的禁带宽度和更高的临界击穿场强。相比同等条件下的硅功率器件,碳化硅器件的耐压程度约为硅材料的10倍。另外,碳化硅器件的电子饱和速率较高、正向导通电阻小、功率损耗较低,适合大电流大功率运用,降低对散热设备的要求。相对于其它第三代半导体(如gan)而言,碳化硅能够较方便的通过热氧化形成二氧化硅。所以碳化硅被认为是新一代高效能电力电子器件重要的发展方向,在新能源汽车、轨道交通、机车牵引、智能电网等领域具有广阔的应用前景。

2、trench mosfet(沟槽式金属氧化物半导体场效应管)是在vdmos(垂直双扩散金属氧化物半导体场效应晶体管)的基础上发展起来的。trench mosfet和平面型功率器件相比,栅极形成在垂直的沟槽中,因此在单位面积上能够得到更多的集成单元,有更多的沟道,能大大的降低器件的导通内阻,通过减小body结深以减小沟道长度,而减小沟道长度会使得body结深变浅,从而影响器件的反向漏电性能,反向漏电变大则会增加器件的关断损耗,因此会影响器件的可靠性。

3、在实际应用中,通常将sictrench mosfet与sbd或jfet反并联集成,可以起到反向续流作用,但是其制作工艺较为复杂,并且还易引起可靠性问题,而且芯片面积有所增大,还不能够满足目前的工业需求。为了减小晶体管器件的尺寸、降低导通电阻、降低动态损耗、提高节能的特性以及提高晶体管的性价比,目前需要一种新型结构的vdmos来适应市场上对于晶体管器件的新要求。

技术实现思路

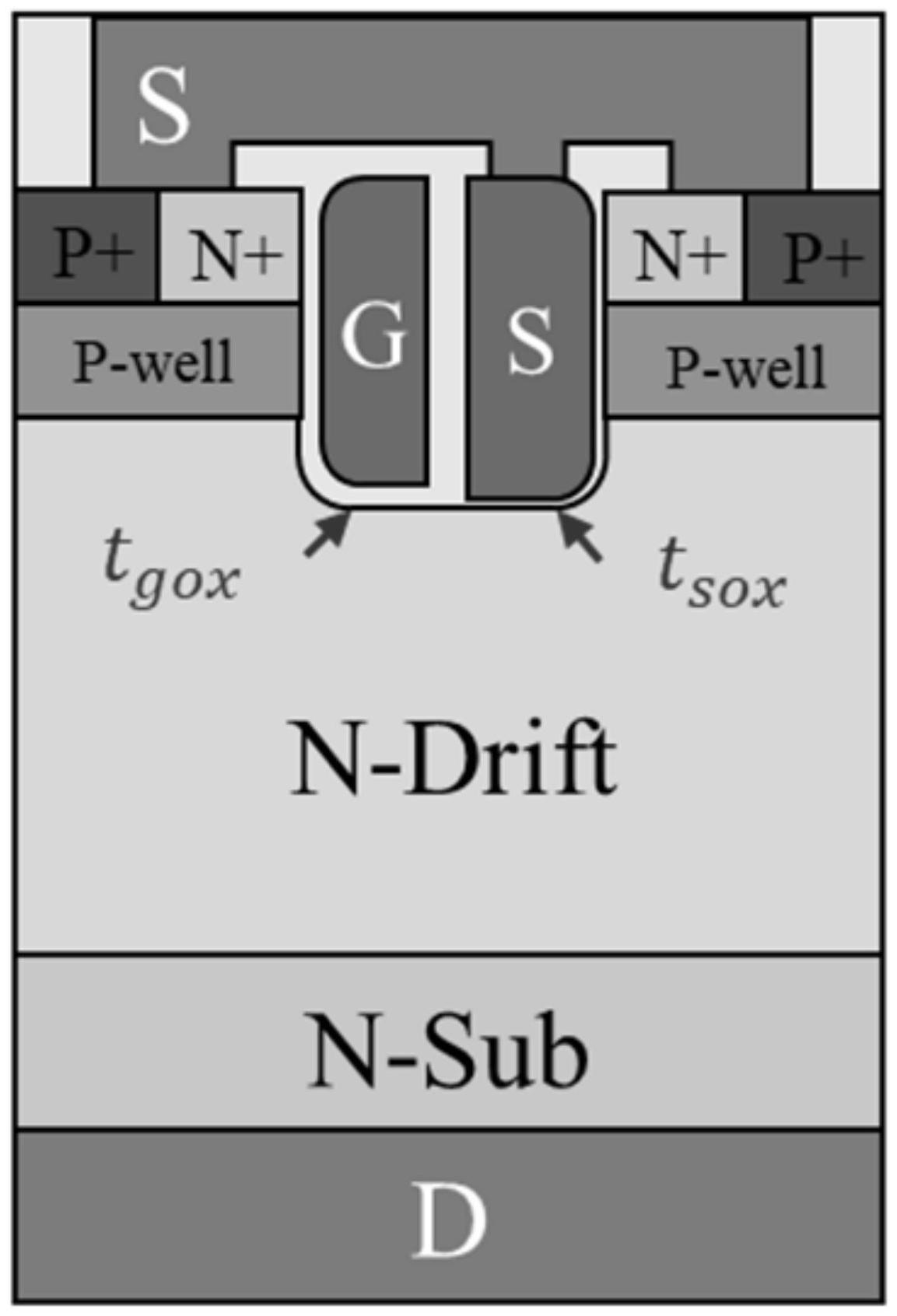

1、本发明的目的是提供一种具有不同栅极氧化厚度的水平分裂栅sic vmos及制备方法,该sic vmos中的沟槽栅极由控制沟道开启的普通栅极g和控制反向续流通道的分裂栅极s组成,源极接0电位或负电位时,源极分裂栅s一侧的pwell不形成沟道,具有高阻特性,源极接正电位反向导通时,源极分裂栅s在p-well层感应出反型层,形成导电通道,从而提高了器件的反向续流能力。

2、一种具有不同栅极氧化厚度的水平分裂栅sic vmos,包括:第一氧化层、栅极和第一分裂栅极;

3、所述第一氧化层包裹所述栅极和所述第一分裂栅极;

4、在第一n+层和p-well层上开设通孔;

5、在n-drift层上层开设沟槽;

6、所述沟槽与所述通孔连接;

7、所述栅极和所述第一分裂栅极位于所述沟槽中;

8、位于第一分裂栅极和沟槽壁面之间的所述第一氧化层的厚度小于位于栅极和沟槽壁面之间的所述第一氧化层的厚度。

9、优选地,位于第一分裂栅极和沟槽壁面之间的所述第一氧化层的厚度为15-25nm。

10、优选地,位于栅极和沟槽壁面之间的所述第一氧化层的厚度为45-55nm。

11、优选地,还包括:源极、漏极、n型衬底、第一p+层;

12、所述漏极位于所述n型衬底下方;

13、所述n型衬底位于所述n-drift层下方;

14、所述n-drift层位于所述p-well下方;

15、所述p-well层位于所述第一p+层和所述第一n+层下方;

16、所述第一p+层和所述第一n+层位于所述源极下方;

17、所述源极与所述分裂栅极连接。

18、优选地,还包括:p+屏蔽层;

19、所述p+屏蔽层位于所述沟槽下方。

20、优选地,还包括:由源极向n-drift层延伸的多个第二分裂栅极、第二氧化层和第二p+层;

21、所述第二分裂栅极被所述第二氧化层包覆;

22、所述第二氧化层被所述第二p+层包覆;

23、所述第二p+层与所述第一n+层、所述p-well层和所述n-drift层邻接。

24、优选地,还包括:第三p+层、第四p+层、第二n+层和第三n+层;

25、所述第三p+层包括与所述第二n+层侧壁的第一端部、位于所述沟槽和所述n-drift层之间的第二端部和位于所述第二n+层与所述n-drift层之间的本体;

26、所述第四p+层与所述第三n+层、所述p-well层和所述n-drift层邻接;

27、所述第二n+层位于所述第一分裂栅极和所述第三p+层的第一端部之间;

28、所述第三n+层位于所述栅极和所述第四p+层之间。

29、一种具有不同栅极氧化厚度的水平分裂栅sic vmos制备方法,包括:

30、在n-drift层上层掺杂形成p-well层、第一p+层和第一n+层;

31、在所述p-well层和所述第一n+层上蚀刻通孔,在所述n-drift层上层蚀刻沟槽,所述沟槽与所述通孔连接;

32、在所述沟槽中沉积氧化物和多晶硅;

33、蚀刻所述多晶硅,并在所述沟槽中回填所述氧化物;

34、二次沉积所述多晶硅,沉积源极和漏极。

35、优选地,在所述沟槽中沉积氧化物和多晶硅包括:在所述沟槽中沉积厚度为15-25nm的栅极氧化物。

36、优选地,在所述沟槽中回填所述氧化物包括:在所述沟槽中回填厚度为20-40nm的所述氧化物。

37、本发明通过将位于第一分裂栅极和沟槽壁面之间的所述第一氧化层的厚度设计小于位于栅极和沟槽壁面之间的所述第一氧化层的厚度,能够使当sic vdmos的源极接零电位或负电位,漏极接高电位时,与源极相连的分裂栅s一侧的p-well层不形成沟道,具有高阻特性,当sic vdmos的源极接正电位,漏极接零电位或者负电位反向导通时,与源极相连的分裂栅s能够在p-well层感应出反型层,形成了从n-drift层到第一n+层再到源极的导电通道,起到了反向续流的作用,该导电通道在反向传导期间具有更小的开启电压,从而提高了sic vdmos的反向续流能力,并且相较于现有技术中通过sic mosfet与sbd或jfet反并联集成的做法具有芯片面积小,可靠性高,制造成本低,关断损耗小的优点。

技术特征:

1.一种具有不同栅极氧化厚度的水平分裂栅sic vmos,其特征在于,包括:第一氧化层、栅极和第一分裂栅极;

2.根据权利要求1所述的一种具有不同栅极氧化厚度的水平分裂栅sic vmos,其特征在于,所述位于第一分裂栅极和沟槽壁面之间的所述第一氧化层的厚度为15-25nm。

3.根据权利要求1所述的一种具有不同栅极氧化厚度的水平分裂栅sic vmos,其特征在于,所述位于栅极和沟槽壁面之间的所述第一氧化层的厚度为45-55nm。

4.根据权利要求1所述的一种具有不同栅极氧化厚度的水平分裂栅sic vmos,其特征在于,还包括:源极、漏极、n型衬底、第一p+层;

5.根据权利要求1所述的一种具有不同栅极氧化厚度的水平分裂栅sic vmos,其特征在于,还包括:p+屏蔽层;

6.根据权利要求1所述的一种具有不同栅极氧化厚度的水平分裂栅sic vmos,其特征在于,还包括:由源极向n-drift层延伸的多个第二分裂栅极、第二氧化层和第二p+层;

7.根据权利要求1所述的一种具有不同栅极氧化厚度的水平分裂栅sic vmos,其特征在于,还包括:第三p+层、第四p+层、第二n+层和第三n+层;

8.一种具有不同栅极氧化厚度的水平分裂栅sic vmos制备方法,其特征在于,包括:

9.根据权利要求8所述的一种具有不同栅极氧化厚度的水平分裂栅sic vmos制备方法,其特征在于,所述在所述沟槽中沉积氧化物和多晶硅包括:在所述沟槽中沉积厚度为15-25nm的栅极氧化物。

10.根据权利要求8所述的一种具有不同栅极氧化厚度的水平分裂栅sic vmos制备方法,其特征在于,所述在所述沟槽中回填所述氧化物包括:在所述沟槽中回填厚度为20-40nm的所述氧化物。

技术总结

本发明提供一种具有不同栅极氧化厚度的水平分裂栅SiC VMOS及制备方法,该SiC VMOS包括:第一氧化层、栅极和第一分裂栅极;所述第一氧化层包裹所述栅极和所述第一分裂栅极;在第一N+层和P‑well层上开设通孔;在N‑drift层上层开设沟槽;所述沟槽与所述通孔连接;所述栅极和所述第一分裂栅极位于所述沟槽中;位于第一分裂栅极和沟槽壁面之间的所述第一氧化层的厚度小于位于栅极和沟槽壁面之间的所述第一氧化层的厚度。本发明中的沟槽栅极由控制沟道开启的普通栅极G和控制反向续流通道的分裂栅极S组成,当源极接正电位反向导通时,源极分裂栅S在P‑well层感应出反型层,形成导电通道,从而提高了器件的反向续流能力。

技术研发人员:乔凯

受保护的技术使用者:天狼芯半导体(成都)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!