具有稳健的亚阈值操作的MOSFET晶体管的制作方法

本发明涉及具有一个或多个金属氧化物半导体(mos)晶体管的集成电路的制造。

背景技术:

1、可以预期用于低电流模拟集成电路的晶体管在亚阈值电压下工作。晶体管匹配通常会影响模拟电路的性能和精度。晶体管的寄生组件可能会影响晶体管的匹配能力。例如,某些与沟道相关的寄生组件可能会降低晶体管的阈值电压,从而影响晶体管在亚阈值操作中的性能和精度。

技术实现思路

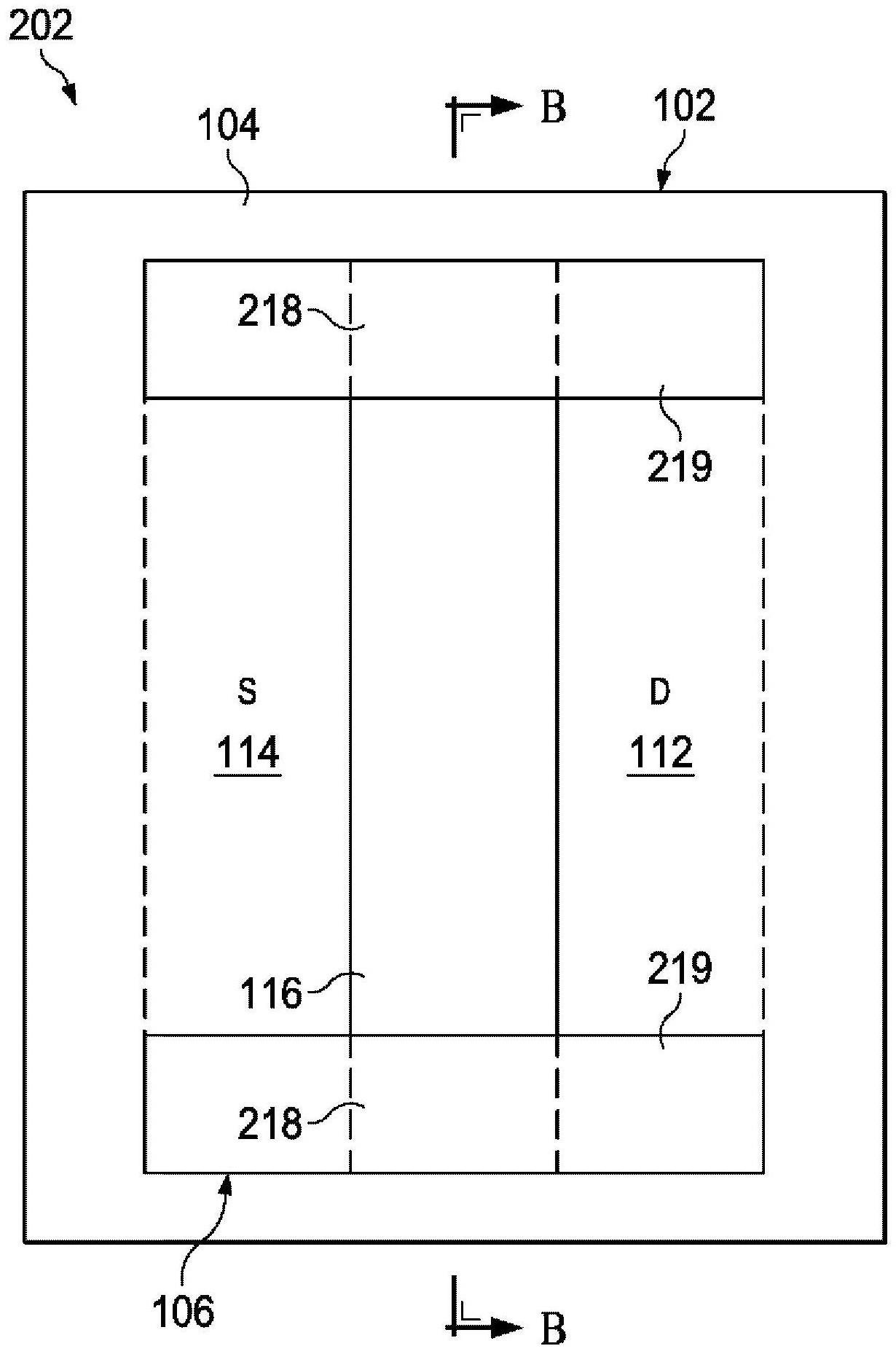

1、在具有形成在衬底上的若干个晶体管区的集成电路的一个示例实施方式中,晶体管区彼此间隔开,并且每个晶体管区由纵向尺度和横向尺度限定。每个晶体管区包括沟道区、端子区和边缘阻挡区。沟道区沿着横向尺度定位,并且该沟道区包括沿着纵向尺度的沟道边缘区。端子区邻近沟道区定位,并且端子区用第一导电类型的第一掺杂剂掺杂。边缘阻挡区沿着纵向尺度定位并且与沟道边缘区相邻。边缘阻挡区用与第一导电类型相反的第二导电类型的第二掺杂剂掺杂。此外,所描述的集成电路包括位于晶体管的沟道区上方的栅电极。

2、在具有形成在衬底上的若干个n沟道晶体管区的集成电路的另一个示例实施方式中,晶体管区彼此间隔开,并且每个晶体管区由纵向尺度和横向尺度限定。每个晶体管区包括沟道区、端子区和边缘阻挡区。沟道区沿着横向尺度定位,并且该沟道区包括沿着纵向尺度的沟道边缘区。端子区邻近沟道区定位,并且端子区用n型掺杂剂掺杂。边缘阻挡区沿着纵向尺度定位并且与沟道边缘区相邻。边缘阻挡区用p型掺杂剂掺杂。此外,所描述的集成电路包括位于晶体管的沟道区上方的栅电极。

3、在具有形成在衬底上的若干个晶体管区的集成电路的又一个示例实施方式中,晶体管区彼此间隔开,并且每个晶体管区由纵向尺度和横向尺度限定。每个晶体管区包括沟道区和边缘恢复区。沟道区沿着横向尺度定位,并且该沟道区包括沿着纵向尺度的沟道边缘区。沟道区用掺杂剂掺杂并具有第一掺杂浓度。边缘恢复区与沟道边缘区重叠,并且该边缘恢复区用相同的掺杂剂掺杂并且具有高于第一掺杂浓度的第二掺杂浓度。此外,所描述的集成电路包括位于晶体管的沟道区上方的栅电极。

技术特征:

1.一种形成集成电路的方法,包括:

2.根据权利要求1所述的方法,进一步包括:

3.根据权利要求2所述的方法,进一步包括:

4.根据权利要求1所述的方法,其中所述边缘阻挡区具有所述第一导电类型,具有与所述第一掺杂浓度基本相同的第四掺杂浓度。

5.根据权利要求4所述的方法,其中形成所述端子区和所述边缘阻挡区包括沿着所述沟道区形成所述端子区,以及选择性地回归所述端子区的与所述沟道边缘区相邻的部分。

6.根据权利要求1所述的方法,其中所述边缘阻挡区具有所述第一导电类型,具有比所述第一掺杂浓度高的第四掺杂浓度。

7.根据权利要求6所述的方法,其中形成所述边缘阻挡区包括用具有所述第一导电类型的掺杂剂和具有限定所述边缘阻挡区的开口的掩模选择性地掺杂所述阱。

8.根据权利要求1所述的方法,进一步包括:

9.根据权利要求8所述的方法,其中形成所述间隔件包括在所述阱的顶表面上并且侧向地在所述边缘阻挡区和所述端子区之间沉积绝缘层,所述端子区在所述间隔件下方与所述边缘阻挡区间隔开。

10.根据权利要求1所述的方法,其中形成所述栅极结构包括在所述沟道区上方形成氧化物层,以及在所述氧化物层上方形成栅电极。

11.根据权利要求10所述的方法,其中形成所述栅极结构进一步包括形成延伸栅电极,所述延伸栅电极从所述栅电极延伸并且在所述端子区和所述边缘阻挡区之间的间隔件区上方。

12.根据权利要求1所述的方法,其中在形成所述栅极结构之后形成所述边缘阻挡区。

13.一种集成电路,包括:

14.根据权利要求13所述的集成电路,进一步包括:

15.根据权利要求14所述的集成电路,进一步包括:

16.根据权利要求13所述的集成电路,其中所述边缘阻挡区具有所述第一导电类型,具有与所述第一掺杂浓度基本相同的所述第四掺杂浓度。

17.根据权利要求13所述的集成电路,其中所述边缘阻挡区具有所述第一导电类型,具有比所述第一掺杂浓度高的第四掺杂浓度。

18.根据权利要求1所述的集成电路,进一步包括:

19.根据权利要求18所述的集成电路,其中所述间隔件包括绝缘层,所述绝缘层沉积在所述阱的顶表面上并且侧向地在所述边缘阻挡区和所述端子区之间,所述端子区在所述间隔件下方与所述边缘阻挡区间隔开。

20.根据权利要求13所述的集成电路,其中所述栅极结构包括在所述沟道区上方的氧化物层和在所述氧化物层上方的栅电极。

21.根据权利要求20所述的集成电路,其中所述栅极结构进一步包括延伸栅电极,所述延伸栅电极从所述栅电极延伸并且在所述端子区和所述边缘阻挡区之间的间隔件区上方。

技术总结

本申请公开具有稳健的亚阈值操作的MOSFET晶体管。在具有形成在衬底上的晶体管区(106)的集成电路的所描述示例中,每个晶体管区(106)包括沟道区(116)和端子区(112,114)。沟道区(116)沿着横向尺度定位,并且其包括沿着纵向尺度的沟道边缘区。端子区(112,114)邻近沟道区(116)定位,并且其用第一导电类型的第一掺杂剂掺杂。每个晶体管区(106)可以包括边缘阻挡区,该边缘阻挡区沿着纵向尺度定位并且与沟道边缘区相邻。边缘阻挡区用与第一导电类型相反的第二导电类型的第二掺杂剂掺杂。沟道区(116)用掺杂剂掺杂并具有第一掺杂浓度。每个晶体管区(106)可以包括边缘恢复区(218),该边缘恢复区(218)与沟道边缘区重叠并且具有高于第一掺杂浓度的第二掺杂浓度。

技术研发人员:X·吴,C·M·汤普森

受保护的技术使用者:德克萨斯仪器股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!