具有分段浮置区的硅控整流器的制作方法

本发明通常涉及半导体装置及集成电路制造,尤其涉及用于硅控整流器的结构以及形成用于硅控整流器的结构的方法。

背景技术:

1、集成电路可能暴露于随机静电放电(electrostatic discharge;esd)事件,这可能潜在地将大且有害的esd电流引导至该集成电路的敏感装置。esd事件是指不可预测的静电放电,在该静电放电期间,高电流在短时间内被引导至该集成电路。esd事件可能发生于制造后芯片处理(post-manufacturing chip handling)期间或芯片安装于电路板或其它承载件上以后。esd事件可能源自各种来源,例如人体、机器组件,或芯片承载件。

2、可采取预防措施来保护该集成电路免受esd事件的影响。一种这样的预防措施是片上(on-chip)保护电路,其经设计以在esd事件期间避免损伤该集成电路的敏感装置。若发生esd事件,则触发该保护电路的保护装置进入低阻抗状态,以将esd电流传导至地并由此将该esd电流分流远离该集成电路的敏感装置。该保护装置保持钳制于其低阻抗状态直至该esd电流耗尽且esd电压被放电至可接受的水平。

3、被部署于esd保护电路中的一种常见类型的保护装置是硅控整流器(silicon-controlled rectifier;scr)。在其静止高阻抗状态下,该scr将电流传导限制于泄漏电流。不过,超过设计阈值的电压脉冲(称为触发电压)启动该scr的阳极与阴极之间的正向电流传导。即使在移除该触发电压之后,只要该正向电流保持于另一设计阈值(称为保持电流)之上,该scr仍保持钳制于其低阻抗状态。当与该esd事件相关联的该正向电流下降至该保持电流以下时,该scr返回至其静止高阻抗状态。

4、需要改进的用于硅控整流器的结构以及形成用于硅控整流器的结构的方法。

技术实现思路

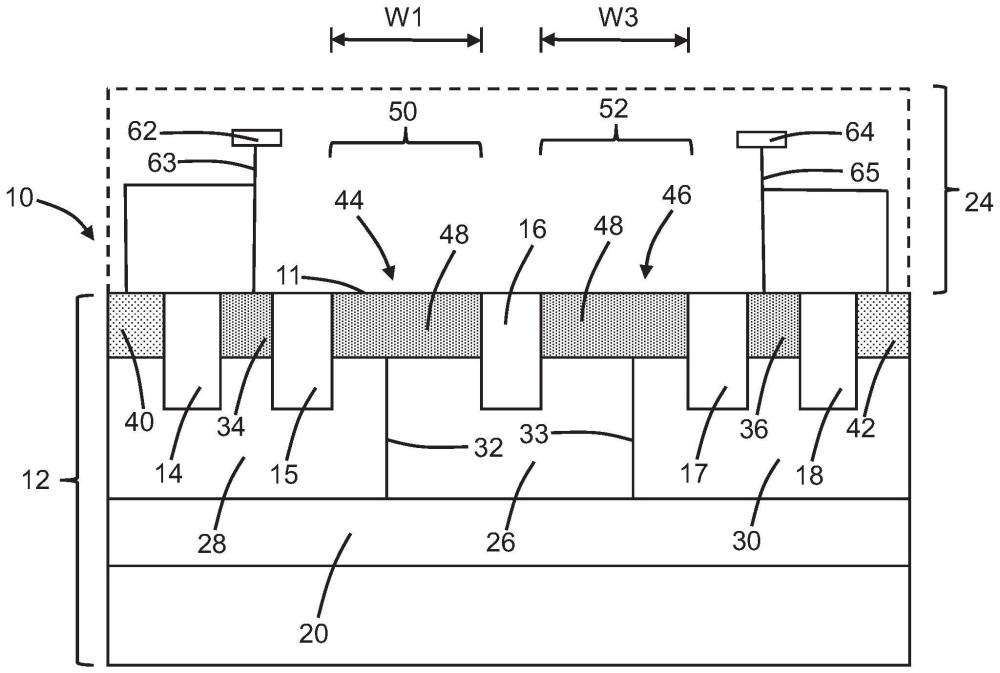

1、在一个实施例中,提供一种用于硅控整流器的结构。该结构包括位于半导体衬底中的第一阱、第二阱,以及第三阱。该第一阱及该第二阱具有第一导电类型,且该第三阱具有与该第一导电类型相反的第二导电类型。该第三阱设置于该第一阱与该第二阱之间。该结构还包括第一端子以及第二端子,该第一端子包括位于该第一阱中的第一掺杂区,该第二端子包括位于该第二阱中的第二掺杂区。该第一掺杂区具有该第二导电类型,且该第二掺杂区具有该第一导电类型。该结构还包括位于该第三阱中的第三掺杂区。该第三掺杂区包括第一片段及第二片段,且该第一片段通过该第一阱的部分及该第三阱的部分与该第二片段隔开。

2、在一个实施例中,提供一种用于硅控整流器的结构。该结构包括位于半导体衬底中的第一阱及第二阱。该第一阱具有第一导电类型,且该第二阱具有与该第一导电类型相反的第二导电类型。该第二阱邻接该第一阱。该结构还包括第一端子以及第二端子,该第一端子包括位于该第一阱中的第一掺杂区,该第二端子包括位于该第二阱中的第二掺杂区。该第一掺杂区具有该第二导电类型,且该第二掺杂区具有该第一导电类型。该结构还包括第三掺杂区,该第三掺杂区包括第一片段及第二片段。该第一片段通过该第一阱的部分及该第二阱的部分与该第二片段隔开。该第一片段及该第二片段分别包括第一部分及第二部分,其中,该第一部分位于该第一阱及该第二阱中,且该第二部分位于该第一阱中。

3、在一个实施例中,提供一种形成用于硅控整流器的结构的方法。该方法包括在半导体衬底中形成第一阱、第二阱,以及第三阱。该第一阱及该第二阱具有第一导电类型,且该第三阱具有与该第一导电类型相反的第二导电类型。该第三阱设置于该第一阱与该第二阱之间。该方法还包括形成包括位于该第一阱中的第一掺杂区的第一端子,以及形成包括位于该第二阱中的第二掺杂区的第二端子。该第一掺杂区具有该第二导电类型,且该第二掺杂区具有该第一导电类型。该方法还包括在该第三阱中形成第三掺杂区。该第三掺杂区包括第一片段及第二片段,且该第一片段通过该第一阱的部分及该第三阱的部分与该第二片段隔开。

技术特征:

1.一种用于硅控整流器的结构,其特征在于,该结构包括:

2.如权利要求1所述的结构,其特征在于,还包括:

3.如权利要求2所述的结构,其特征在于,该第一浅沟槽隔离区设置于该第三阱中。

4.如权利要求3所述的结构,其特征在于,该第一阱在设置于该第一浅沟槽隔离区与该第二浅沟槽隔离区间的界面邻接该第三阱,且该第一片段及该第二片段分别包括自该第一浅沟槽隔离区延伸至该界面的第一部分。

5.如权利要求4所述的结构,其特征在于,该第一片段的该第一部分及该第二片段的该第一部分在该界面邻接该第一阱的相应部分。

6.如权利要求4所述的结构,其特征在于,该第一片段及该第二片段分别包括自该第一浅沟槽隔离区完全延伸至该第二浅沟槽隔离区的第二部分。

7.如权利要求6所述的结构,其特征在于,该第一片段的该第二部分及该第二片段的该第二部分延伸跨越部分位于该第一阱中且部分位于该第三阱中的该界面。

8.如权利要求4所述的结构,其特征在于,该第一片段及该第二片段具有该第二导电类型。

9.如权利要求2所述的结构,其特征在于,该第一浅沟槽隔离区设置于该第一阱中。

10.如权利要求9所述的结构,其特征在于,该第一阱在设置于该第一浅沟槽隔离区与该第二浅沟槽隔离区间的界面邻接该第三阱,且该第一片段及该第二片段分别包括自该第一浅沟槽隔离区延伸至该界面的第一部分。

11.如权利要求10所述的结构,其特征在于,该第一片段的该第一部分及该第二片段的该第一部分在该界面邻接该第三阱的相应第一部分。

12.如权利要求10所述的结构,其特征在于,该第一片段及该第二片段分别包括自该第一浅沟槽隔离区完全延伸至该第二浅沟槽隔离区的第二部分。

13.如权利要求12所述的结构,其特征在于,该第一片段的该第二部分及该第二片段的该第二部分延伸跨越部分位于该第一阱中且部分位于该第三阱中的该界面。

14.如权利要求10所述的结构,其特征在于,该第一片段及该第二片段具有该第一导电类型。

15.如权利要求1所述的结构,其特征在于,该第三掺杂区被配置为电性浮置。

16.如权利要求1所述的结构,其特征在于,还包括:

17.如权利要求16所述的结构,其特征在于,还包括:

18.如权利要求17所述的结构,其特征在于,还包括:

19.一种用于硅控整流器的结构,其特征在于,该结构包括:

20.一种形成用于硅控整流器的结构的方法,其特征在于,该结构包括:

技术总结

本发明涉及具有分段浮置区的硅控整流器,提供用于硅控整流器的结构以及形成用于硅控整流器的结构的方法。该结构包括位于半导体衬底中的第一阱、第二阱,以及第三阱。该第三阱设置于该第一阱与该第二阱间。第一端子包括位于该第一阱中的第一掺杂区,且第二端子包括位于该第二阱中的第二掺杂区。该第一阱、该第二阱,以及该第二掺杂区具有第一导电类型,且该第三阱及该第一掺杂区具有与该第一导电类型相反的第二导电类型。该结构还包括位于该第三阱中的第三掺杂区。该第三掺杂区包括第一片段及第二片段,且该第一片段通过该第一阱的部分及该第三阱的部分与该第二片段隔开。

技术研发人员:阿杰伊,R·K·杰恩,P·马哈詹,A·扎卡

受保护的技术使用者:格芯(美国)集成电路科技有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!