基于Fin结构的GaN高电子迁移率晶体管及其制备方法

本发明属于半导体,具体涉及一种基于fin结构的gan高电子迁移率晶体管及其制备方法。

背景技术:

1、gan(氮化镓)作为第三代半导体材料,具有禁带宽度大、击穿场强高、耐高温、耐辐照、电子迁移率大及饱和电子速度大等特点,使其制作gan基高电子迁移率晶体管(hemt)器件在卫星通讯、5g基站、军事雷达及新能源汽车等领域有着广泛的应用。对于gan基hemt器件而言,解决非线性问题是当下研究的重点。

2、近些年来,研究员们为解决gan基hemt器件的非线性问题,提出了许多有效的解决方案。图1所示为传统的鳍式三维栅结构,该结构可以使沟道三面都有栅极,这就加强了栅极对沟道的控制能力,一方面可以解决短沟道效应,另一方面可以减小器件的源电阻rs在大电流下的快速增加,从而改善器件的线性度。图2所示为传统的侧栅结构,其与鳍式三维栅器件不同在于只在器件沟道两侧有栅极控制,没有顶部的平面栅控制,从而消除了平面栅所带来的峰值电场,且两侧的侧栅对沟道的耗尽也是渐变的,类似于场效应晶体管的工作原理,从而改善器件的线性性能。

3、虽然传统的鳍式三维栅结构与侧栅结构可以改善器件的线性度,但是仅限于鳍片宽度较窄的情况下(通常小于400nm),当鳍片宽度变大,对于鳍式三维栅器件而言,沟道两旁的侧栅就会失去意义,对于侧栅器件而言,鳍片宽度变大会导致器件关不断。所以在使用鳍式三维栅结构与侧栅结构去改善器件线性度的时候,就需要刻蚀一定数量的隔离槽,在隔离槽宽度不变的时,鳍片宽度越小,需要刻蚀的隔离槽数目就越多,这样一来虽然器件的线性度得到了改善,但是这也造成了器件最后输出电流的损失。此外,由于引入更多的隔离槽数目使得器件的刻蚀损伤也变大。

4、综上,如何在大的鳍片宽度(≥400nm)上改善器件线性度,同时,提高器件的输出电流并减小器件的刻蚀损伤是目前亟待解决的问题。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种基于fin结构的gan高电子迁移率晶体管及其制备方法。本发明要解决的技术问题通过以下技术方案实现:

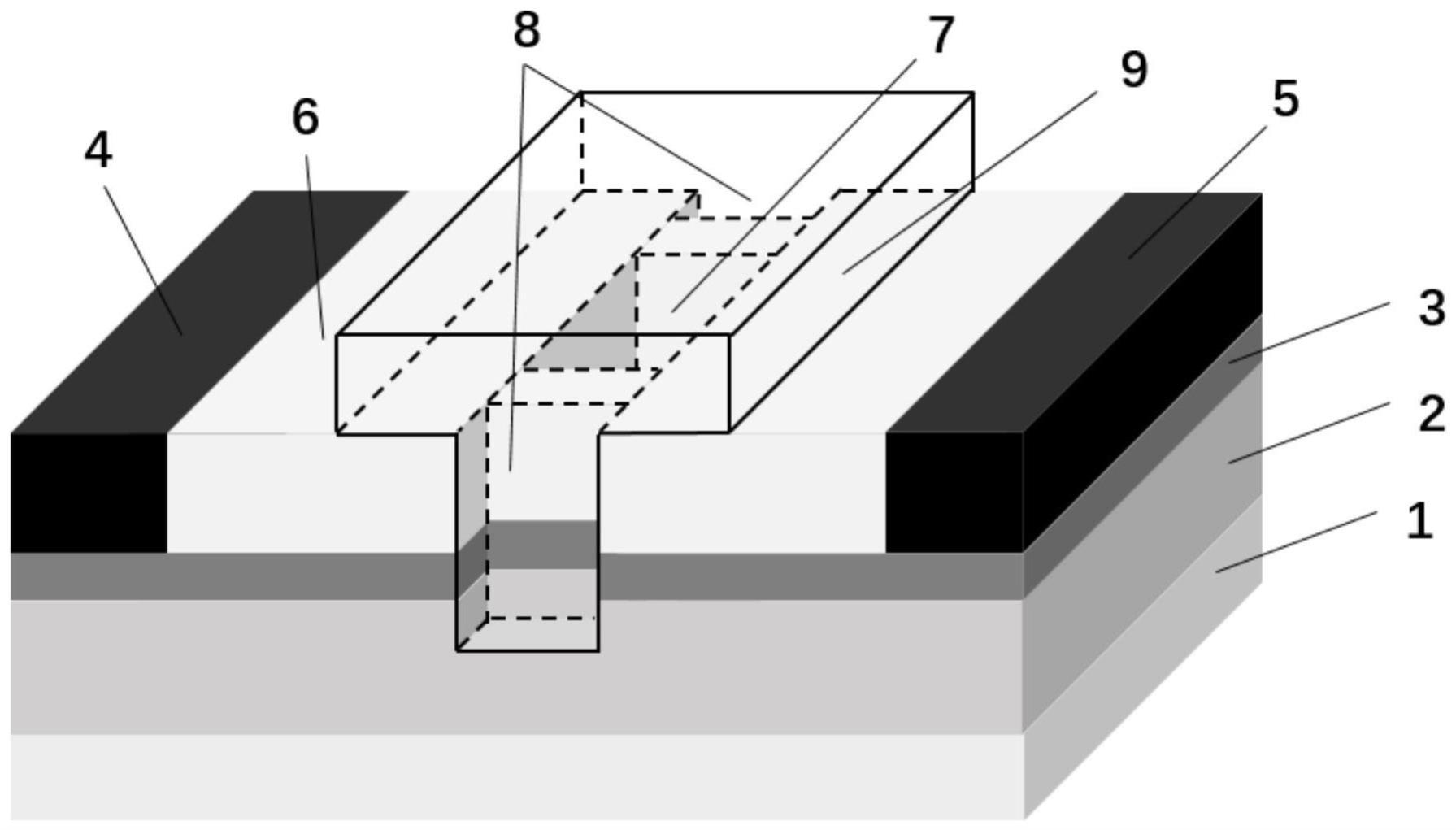

2、第一方面,本发明提供了一种基于fin结构的gan高电子迁移率晶体管,包括:自下而上依次设置的衬底、gan缓冲层和势垒层;所述势垒层上方的一端设有源极,另一端设有漏极;所述源极和所述漏极之间的势垒层上面设有钝化层;其中,

3、所述钝化层中间设有栅脚槽,所述栅脚槽的两侧设有隔离槽;所述栅脚槽自所述钝化层的上表面向下延伸至所述势垒层中;所述隔离槽自所述钝化层的上表面向下延伸至所述缓冲层中;

4、所述栅脚槽和所述隔离槽内均设有栅,分别形成顶部平面栅和侧栅,从而形成鳍片式三维栅结构;

5、所述栅脚槽和所述隔离槽的长度相等;所述栅脚槽的宽度小于鳍片的宽度。

6、在本发明的一个实施例中,所述栅极为t型栅结构。

7、在本发明的一个实施例中,所述势垒层的厚度为20nm,所述栅脚槽延伸至所述势垒层中的深度为10nm。

8、在本发明的一个实施例中,所述势垒层的材料包括algan。

9、第二方面,本发明提供了一种基于fin结构的gan高电子迁移率晶体管的制备方法,包括以下步骤:

10、提供一衬底,并在所述衬底上外延gan缓冲层和势垒层;

11、在所述势垒层两端制备源极和漏极;

12、在所述势垒层上的源极和漏极之间形成钝化层;

13、在所述钝化层中间刻蚀栅脚槽;所述栅脚槽自所述钝化层的上表面向下延伸至所述势垒层中;

14、在所述钝化层上栅脚槽的两侧刻蚀隔离槽;所述隔离槽自所述钝化层的上表面向下延伸至所述缓冲层中;

15、在所述栅脚槽和所述隔离槽内制备栅极,以形成包括顶部平面栅和侧栅的鳍片式三维栅结构,从而完成器件制备。

16、在本发明的一个实施例中,在所述栅脚槽和所述隔离槽内制备栅极,包括:

17、在样品表面光刻栅帽图形;

18、基于所述栅帽图形在所述栅脚槽和所述隔离槽内制备t型栅极。

19、本发明的有益效果:

20、1、本发明提供的基于fin结构的gan高电子迁移率晶体管设计了鳍片式三维栅结构,并将处于顶部的平面栅极宽度小于鳍片的宽度;一方面,该结构利用顶部平面栅与侧栅对沟道控制能力的不同,将鳍片下方的沟道分为两种阈值电压不同的沟道,采用跨导补偿的方法去改善器件的线性度;另一方面,该结构可以辅助侧栅将沟道中间的2deg给耗尽,保证器件在改善线性度的同时可以被关断。采用本发明的鳍式三维栅结构在大的鳍片宽度(≥400nm)上去改善器件线性度的同时,可以提高有效沟道在总器件栅宽中的占比,从而提高器件最终输出电流;

21、2、本发明提供基于fin结构的gan高电子迁移率晶体管设计的鳍片式三维栅结构,相比传统鳍式三维栅与侧栅器件,还可以减小引入的隔离槽数目,从而减小器件的刻蚀损伤。

22、以下将结合附图及实施例对本发明做进一步详细说明。

技术特征:

1.一种基于fin结构的gan高电子迁移率晶体管,其特征在于,包括:自下而上依次设置的衬底(1)、gan缓冲层(2)和势垒层(3);所述势垒层(3)上方的一端设有源极(4),另一端设有漏极(5);所述源极(4)和所述漏极(5)之间的势垒层(3)上面设有钝化层(6);其中,

2.根据权利要求1所述的基于fin结构的gan高电子迁移率晶体管,其特征在于,所述栅极(9)为t型栅结构。

3.根据权利要求1所述的基于fin结构的gan高电子迁移率晶体管,其特征在于,所述势垒层(3)的厚度为20nm,所述栅脚槽(7)延伸至所述势垒层(3)中的深度为10nm。

4.根据权利要求1所述的基于fin结构的gan高电子迁移率晶体管,其特征在于,所述势垒层(3)的材料包括algan。

5.一种基于fin结构的gan高电子迁移率晶体管的制备方法,其特征在于,包括以下步骤:

6.根据权利要求5所述的基于fin结构的gan高电子迁移率晶体管的制备方法,其特征在于,在所述栅脚槽和所述隔离槽内制备栅极,包括:

技术总结

本发明公开了一种基于Fin结构的GaN高电子迁移率晶体管及其制备方法,该器件结构包括自下而上依次设置的衬底、GaN缓冲层和势垒层;势垒层上方的一端设有源极,另一端设有漏极;源极和漏极之间的势垒层上面设有钝化层;其中,钝化层中间设有栅脚槽,栅脚槽的两侧设有隔离槽;栅脚槽自钝化层的上表面向下延伸至势垒层中;隔离槽自钝化层的上表面向下延伸至缓冲层中;栅脚槽和隔离槽内均设有栅极,分别形成顶部平面栅和侧栅,从而形成鳍片式三维栅结构;栅脚槽和隔离槽的长度相等;栅脚槽的宽度小于鳍片的宽度。该结构在大鳍片宽度上可以实现线性度好、输出电流高以及栅极泄漏电流小的GaN高电子迁移率晶体管。

技术研发人员:张鹏,刘加志,宓珉翰,马晓华,赵文

受保护的技术使用者:西安电子科技大学

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!