一种屏蔽栅沟槽VDMOS器件及其制造方法与流程

本发明涉及功率半导体器件,尤其涉及一种屏蔽栅沟槽vdmos器件。

背景技术:

1、屏蔽栅场效应晶体管(sgfet)是一种特殊类型的场效应晶体管(简称fet)。它是由金属栅极、源极、漏极和屏蔽层组成的。一般的fet由栅极和沟道之间的绝缘层来控制电流流动,但在sgfet中,引入了屏蔽层来改善器件性能。屏蔽层的作用是将栅极与沟道之间的电场分隔开,减少电荷积累和漏电流,减少栅极与源极之间的电容耦合效应,从而提高晶体管的开关速度和工作稳定性。降低漏电流:屏蔽层有效地减少了漏电流,提高了器件的工作稳定性。由于其导通电阻低、开关速度高以及抗干扰能力强,广泛应用于功率器件和电源领域。

2、然而,sgfet也存在一些限制,相对于传统的晶体管来说,制造和设计上更为复杂,主要是屏蔽栅结构的形成工艺比较复杂;例如,在屏蔽栅沟槽vdmos的形成屏蔽栅与控制沟槽栅两层多晶结构的隔离氧化层结构工艺中,先后需经过氧化层淀积工艺,cmp工艺,湿法腐蚀工艺形成隔离氧化层;由于上述工艺的原因,形成的隔离氧化层结构比较平整,隔离氧化层与沟槽侧壁硅成90度夹角,如图5所示,在后续的栅氧化工艺中,由于此直角结构的限制,再加上栅氧化工艺过程中产生的氧化层的厚度本身就不易控制,因此极易造成栅极多晶硅层底部拐角处栅氧化层较薄,抗电场击穿能力较差,进而造成产品可靠性较差的问题。

技术实现思路

1、为克服上述屏蔽栅场效应晶体管及其制造方法所存在的缺陷,本发明要解决的技术问题是提供一种栅氧化层厚度均匀,抗电场击穿能力强的屏蔽栅沟槽vdmos器件及其制造方法。

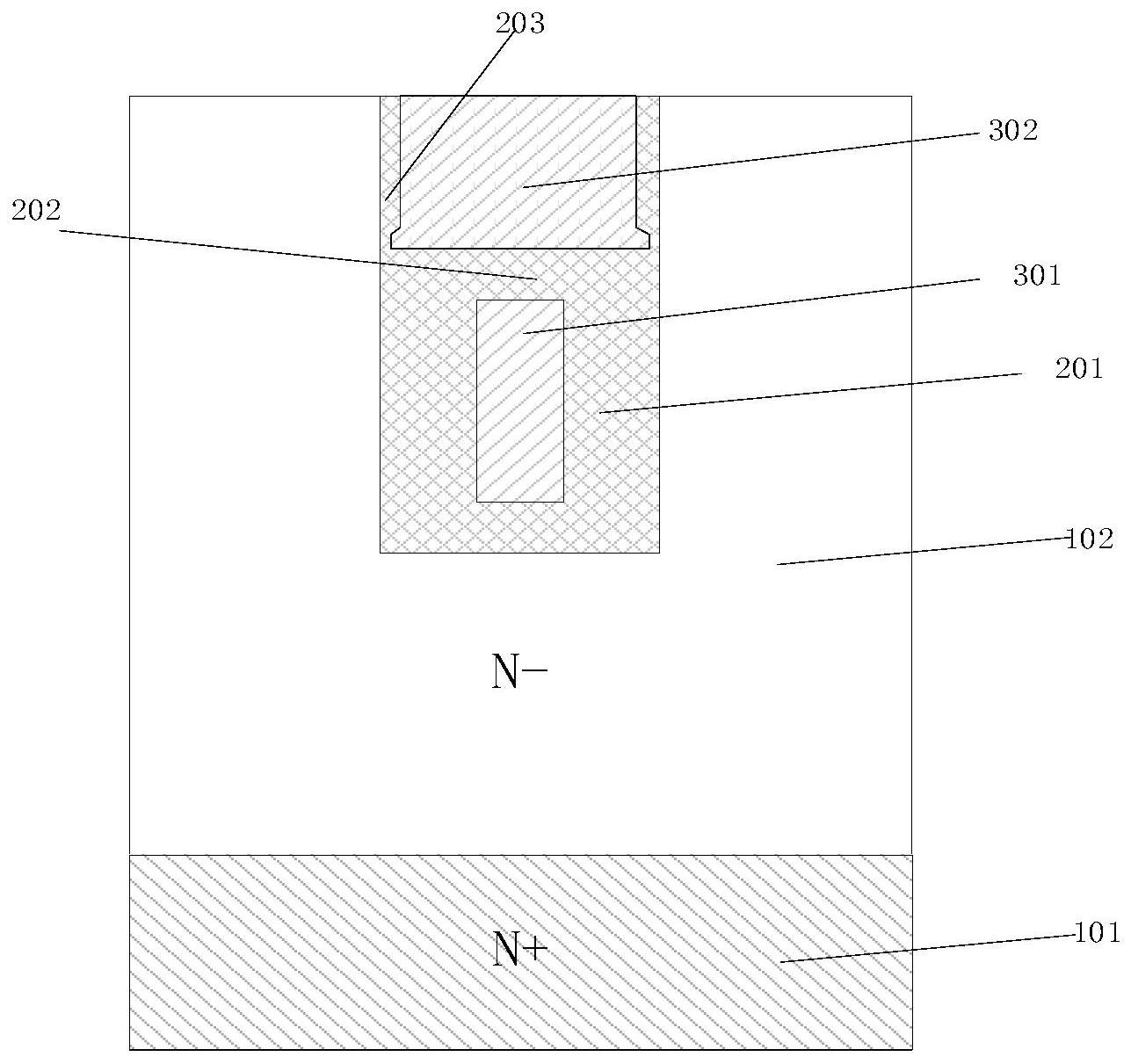

2、就屏蔽栅沟槽vdmos器件而言,本发明为解决所述技术问题的屏蔽栅沟槽vdmos器件包括:n-漂移区,所述漂移区设置有沟道,所述沟道内设置有栅极多晶硅和源极多晶硅;所述栅氧化层靠近所述层间氧化层的边部的厚度不小于所述栅氧化层远离所述层间氧化层的边部的厚度。

3、作为上述屏蔽栅沟槽vdmos器件的改进,所述栅极多晶硅的底壁与侧壁间圆滑过渡连接,所述栅氧化层靠近所述层间氧化层的边部的厚度由从所述沟道侧壁向远离所述沟道侧壁的方向逐渐变厚。

4、作为上述屏蔽栅沟槽vdmos器件的改进,所述沟道的侧壁与所述栅氧化层之间留有氮化硅材质的薄膜。

5、与相关技术相比,本发明的屏蔽栅vdmos的隔离氧化层与沟槽拐角部位具有较厚的栅氧化层结构,栅氧化层靠近所述层间氧化层的边部呈圆弧结构,并且底部氧化层厚度要高于顶部栅氧化层厚度,进而避免了传统工艺带来的氧化层不均匀的缺陷;因此本发明的屏蔽栅vdmos的栅氧化层可以有效提高屏蔽栅vdmos的抗esd能力(面对静电放电时的耐受能力)和抗冲击能力(面对瞬态冲击或脉冲电压时的耐受能力),增强器件可靠性。

6、就屏蔽栅沟槽vdmos器件的制造方法而言,本发明为解决所述技术问题的屏蔽栅沟槽vdmos器件的制造方法包括如下步骤:

7、在晶圆表面进行沟槽刻蚀;

8、进行热氧化工艺,在所述沟槽内生成场氧化层;

9、进行多晶硅淀积并反刻,在所述场氧化层中形成屏蔽层源极多晶硅;

10、进行氧化层淀积对所述沟槽进行填充,在所述屏蔽层源极多晶硅上方形成初始层间氧化层;

11、对所述初始层间氧化层进行氧化层表面平整处理及湿法腐蚀处理,使所述初始层间氧化层上表面距离所述屏蔽层源极多晶硅一定深度,形成层间氧化层;

12、进行栅氧化工艺,在所述层间氧化层上方形成栅氧化层;

13、进行多晶硅的淀积并反刻,在所述栅氧化层内形成栅极多晶硅层。

14、作为上述屏蔽栅沟槽vdmos器件制造方法的改进,所述层间氧化层的截面形状为两边高,中间低的弧形结构。

15、作为上述屏蔽栅沟槽vdmos器件制造方法的改进,所述层间氧化层的上表面的切面与n-漂移区侧壁所在平面的夹角大于90°。

16、作为上述屏蔽栅沟槽vdmos器件制造方法的改进,所述层间氧化层的上表面的切面与n-漂移区侧壁所在平面的夹角范围介于160-180°之内。

17、作为上述屏蔽栅沟槽vdmos器件制造方法的改进,所述栅氧化层靠近所述层间氧化层的边部的厚度不小于所述栅氧化层远离所述层间氧化层的边部的厚度。

18、作为上述屏蔽栅沟槽vdmos器件制造方法的改进,所述栅极多晶硅的底壁与侧壁间圆滑过渡连接,所述栅氧化层靠近所述层间氧化层的边部的厚度由从所述沟道侧壁向远离所述沟道侧壁的方向逐渐变厚。

19、作为上述屏蔽栅沟槽vdmos器件制造方法的改进,在形成所述层间氧化层之前,

20、进行sin淀积,并反刻,在所述沟槽侧壁形成sin层。

21、作为上述屏蔽栅沟槽vdmos器件制造方法的改进,再进行一次湿法腐蚀氧化层工艺,形成所述层间氧化层。

22、与相关技术相比,本发明的屏蔽栅沟槽vdmos器件制造方法通过制备碗状的隔离氧化层,使隔离氧化层与器件的沟槽的拐角部位的夹角远大于90°,使得拐角部位处在进行栅氧化工艺时的热氧化速率提高,从而能够形成较厚且更加均匀的栅氧化层结构,进而避免了传统工艺带来的栅极多晶硅层底部拐角处栅氧化层较薄,抗电场击穿能力较差,产品可靠性较差的问题。

技术特征:

1.一种屏蔽栅沟槽vdmos器件,其特征在于,包括:

2.根据权利要求1所述的屏蔽栅沟槽vdmos器件,其特征在于,

3.根据权利要求1所述的屏蔽栅沟槽vdmos器件,其特征在于,

4.一种屏蔽栅沟槽vdmos器件的制造方法,其特征在于,包括如下步骤:

5.根据权利要求4所述的屏蔽栅沟槽vdmos器件的制造方法,其特征在于,

6.根据权利要求5所述的屏蔽栅沟槽vdmos器件的制造方法,其特征在于,

7.根据权利要求4所述的屏蔽栅沟槽vdmos器件的制造方法,其特征在于,

8.根据权利要求7所述的屏蔽栅沟槽vdmos器件的制造方法,其特征在于,

9.根据权利要求4至6任一项所述的屏蔽栅沟槽vdmos器件的制造方法,其特征在于,

10.根据权利要求9所述的屏蔽栅沟槽vdmos器件的制造方法,其特征在于,

技术总结

本发明一种屏蔽栅沟槽VDMOS器件,该器件包括N‑漂移区,漂移区设置有沟道,沟道内设置有栅极多晶硅和源极多晶硅;栅极多晶硅与源极多晶硅通过层间氧化层隔离,栅极多晶硅与N‑漂移区之间通过栅氧化层隔离;栅氧化层靠近层间氧化层的边部的厚度不小于栅氧化层远离层间氧化层的边部的厚度。该制造方法包括如下步骤:沟槽刻蚀;热氧化工艺生成场氧化层;多晶硅淀积并反刻形成源极多晶硅;氧化层淀积形成初始层间氧化层;表面平整及湿法腐蚀处理形成层间氧化层;栅氧化工艺形成栅氧化层;多晶硅的淀积并反刻形成栅极多晶硅层。本发明栅氧化层结构可以有效降低栅极多晶层底部电场峰值,进一步增强器件可靠性。

技术研发人员:单亚东,胡丹,谢刚

受保护的技术使用者:广微集成技术(深圳)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!