DDRIO版图结构、集成电路版图及半导体器件的制作方法

本申请涉及集成电路领域,具体涉及一种ddrio版图结构、集成电路版图及半导体器件。

背景技术:

1、ddrio(double data rate input or output,双倍率输入输出)是芯片中的一种重要部件,又称为双倍速率同步动态随机访问存储器模拟输入输出模块。ddrio通常用于芯片的内部控制逻辑和外部存储颗粒之间的数据传输。ddrio通常是一个库,内部包括多个具有不同电路功能的io单元。在设计ddrio结构时,大多是基于单个io内部电路来设计,这使得单个io结构根据内部电路的不同而有所不同,当电路较为复杂时,io结构复杂,容易引起混乱,不利于ddrio结构的高效设计和开发;同时,由于io结构不同,io拼接时容易引起drc(design rule check,设计规则检查)问题。

技术实现思路

1、本申请的一个目的在于提出一种ddrio版图结构、集成电路版图及半导体器件,以提高ddrio版图结构的设计效率。

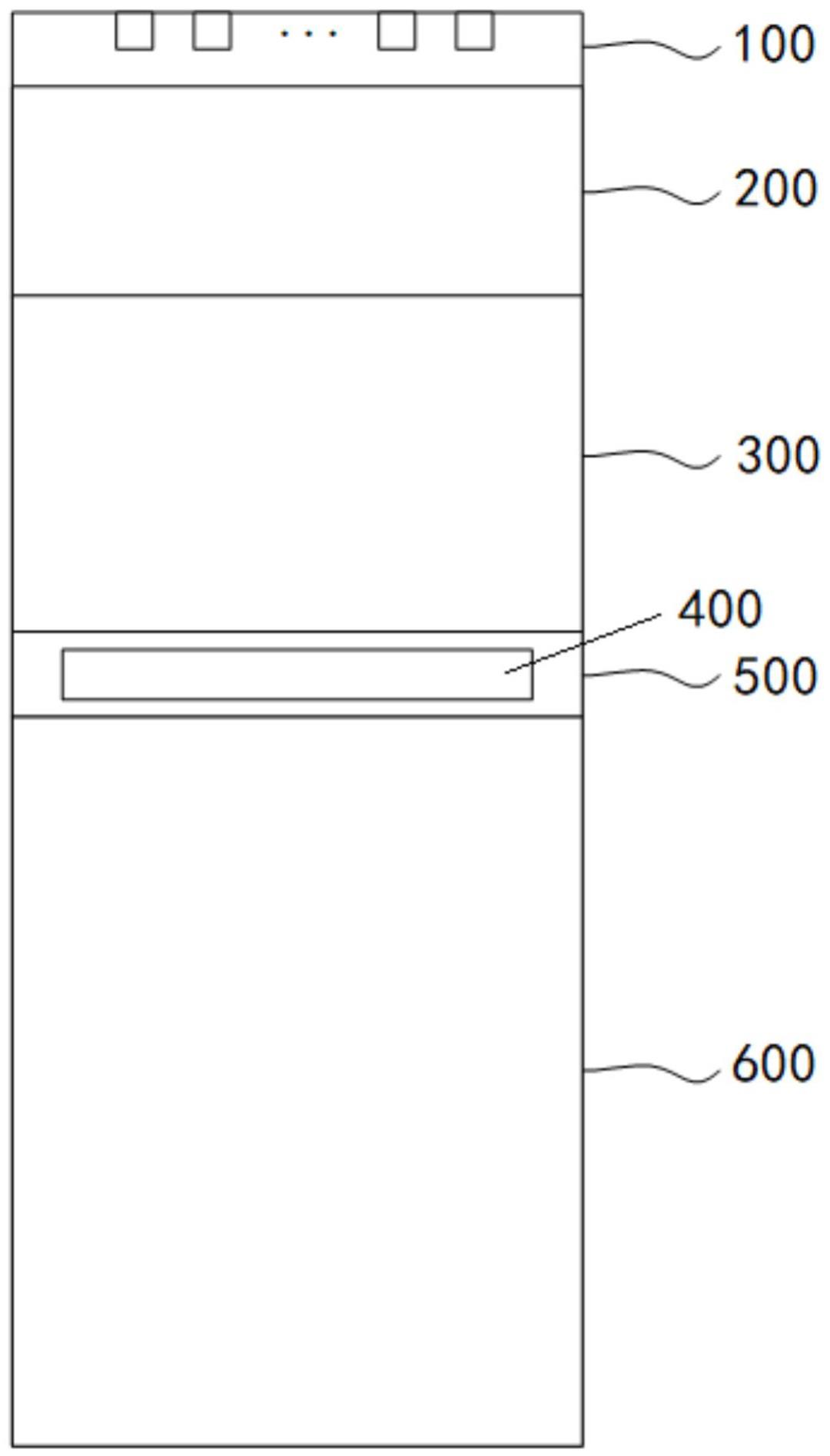

2、根据本申请实施例的一方面,公开了一种ddrio版图结构,包括:

3、内部信号区,位于所述ddrio版图结构的上部边缘处,用于布设与芯片内部结构连接的信号线;

4、低压器件区,位于所述内部信号区下方,用于放置低压器件;

5、高压器件区,位于所述低压器件区下方,用于放置高压器件;

6、静电放电器件区,位于所述高压器件区下方,用于放置静电放电器件;

7、外部信号区,位于所述静电放电器件区的最上层,用于布设与芯片外部结构连接的信号线;

8、稳压电容区,位于所述静电放电器件区的下方,用于放置高压电源的稳压电容;

9、所述内部信号区、所述低压器件区、所述高压器件区、所述静电放电器件区和所述稳压电容区的宽度相等。

10、在本申请的一个实施例中,所述ddrio版图结构还包括io边缘结构,所述io边缘结构位于所述ddrio版图结构的左边缘和右边缘,所述io边缘结构包括p型或n型的条状衬底接触,所述条状衬底接触的类型与所述io边缘结构处所述ddrio版图结构的内部器件类型相反。

11、在本申请的一个实施例中,所述条状衬底接触的中心线与所述ddrio版图结构边缘处的边缘线重合。

12、在本申请的一个实施例中,所述内部信号区包括多条第一信号线和反接二极管,所述第一信号线包括在所述ddrio版图结构高度方向上相邻的两层金属;所述反接二极管的正极性端接地,所述反接二极管的负极性端连接所述金属;所述第一信号线的宽度大于或等于最小走线宽度的两倍与最小走线间距之和,所述最小走线宽度为所述芯片内部结构中与所述内部信号区连接的信号线的最小宽度,所述最小走线间距为所述芯片内部结构中与所述内部信号区连接的两根信号线之间的最小间距。

13、在本申请的一个实施例中,所述静电放电器件区包括第一级器件、静电保护电阻和第二级器件,所述静电保护电阻连接于所述第一级器件和所述第二级器件之间;所述第一级器件与所述外部信号区连接,所述第二级器件与所述高压器件区。

14、在本申请的一个实施例中,所述静电放电器件区包括p型二极管、n型二极管、电源线和地线,所述外部信号区包括第二信号线;所述p型二极管和所述n型二极管沿所述ddrio版图结构的宽度方向分布,所述电源线位于所述p型二极管之上,所述地线位于所述n型二极管之上,所述第二信号线位于所述电源线和所述地线之间。

15、在本申请的一个实施例中,所述稳压电容区包括多种类型的器件电容,同一种类型的器件电容的高度在同一个高度范围内。

16、在本申请的一个实施例中,所述低压器件区、所述高压器件区、所述静电放电器件区和所述稳压电容区包括电源线,所述电源线沿所述ddrio版图结构的宽度方向布设。

17、在本申请的一个实施例中,所述内部信号区、所述低压器件区、所述高压器件区和所述稳压电容区在与所述ddrio版图结构的长度方向平行的边缘处设有隔离区。

18、在本申请的一个实施例中,所述隔离区包括条状衬底接触,所述条状衬底接触的中心线与所述边缘处的边缘线重合。

19、根据本申请实施例的一方面,提供一种集成电路版图,包括多个本申请任意实施例提供的ddrio版图结构,拼接后相邻两个所述ddrio版图结构的边缘线重合。

20、根据本申请实施例的一方面,提供一种半导体器件,所述半导体器件的部分或全部基于本申请提供的集成电路版图制成。

21、在本申请实施例提供的技术方案中,通过将ddrio版图结构划分为内部信号区、低压器件区、高压器件区、静电放电器件区、外部信号区和稳压电容区,各区域在ddrio版图结构的长度方向上依次分布,并保持各区域宽度相等,使得ddrio版图结构清晰明了,可以快速定位io单元所包含的各器件所在区域,有效缩减ddrio版图的结构设计时间,提高设计效率。

22、本申请的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本申请的实践而习得。

23、应当理解的是,以上的一般描述和后文的细节描述仅是示例性的,并不能限制本申请。

技术特征:

1.一种ddrio版图结构,其特征在于,包括:

2.根据权利要求1所述的ddrio版图结构,其特征在于,所述ddrio版图结构还包括io边缘结构,所述io边缘结构位于所述ddrio版图结构的左边缘和右边缘,所述io边缘结构包括p型或n型的条状衬底接触,所述条状衬底接触的类型与所述io边缘结构处所述ddrio版图结构的内部器件类型相反。

3.根据权利要求2所述的ddrio版图结构,其特征在于,所述条状衬底接触的中心线与所述ddrio版图结构边缘处的边缘线重合。

4.根据权利要求1所述的ddrio版图结构,其特征在于,所述内部信号区包括多条第一信号线和反接二极管;

5.根据权利要求1所述的ddrio版图结构,其特征在于,所述静电放电器件区包括第一级器件、静电保护电阻和第二级器件,所述静电保护电阻连接于所述第一级器件和所述第二级器件之间;所述第一级器件与所述外部信号区连接,所述第二级器件与所述高压器件区连接。

6.根据权利要求1所述的ddrio版图结构,其特征在于,所述静电放电器件区包括p型二极管、n型二极管、电源线和地线,所述外部信号区包括第二信号线;所述p型二极管和所述n型二极管沿所述ddrio版图结构的宽度方向分布,所述电源线位于所述p型二极管之上,所述地线位于所述n型二极管之上,所述第二信号线位于所述电源线和所述地线之间。

7.根据权利要求1所述的ddrio版图结构,其特征在于,所述稳压电容区包括多种类型的器件电容,同一种类型的器件电容的高度在同一个高度范围内。

8.根据权利要求1所述的ddrio版图结构,其特征在于,所述低压器件区、所述高压器件区、所述静电放电器件区和所述稳压电容区包括电源线,所述电源线沿所述ddrio版图结构的宽度方向布设。

9.一种集成电路版图,其特征在于,包括多个如权利要求1至8任意一项所述的ddrio版图结构,拼接后相邻两个所述ddrio版图结构的边缘线重合。

10.一种半导体器件,其特征在于,所述半导体器件的部分或全部基于如权利要求9所述的集成电路版图制成。

技术总结

本申请提供了一种DDRIO版图结构,包括:内部信号区,位于DDRIO版图结构的上部边缘处,用于布设与芯片内部结构连接的信号线;低压器件区,位于内部信号区下方;高压器件区,位于低压器件区下方;静电放电器件区,位于高压器件区下方,用于放置静电放电器件;外部信号区,位于静电放电器件区的最上层,用于布设与芯片外部结构连接的信号线;稳压电容区,位于静电放电器件区的下方,用于放置高压电源的稳压电容;内部信号区、低压器件区、高压器件区、静电放电器件区和稳压电容区的宽度相等。本申请技术方案提供的DDRIO版图结构清晰明了,可以快速定位IO单元所包含的各器件所在区域,有效缩减DDRIO版图的结构设计时间,提高设计效率。

技术研发人员:李长猛

受保护的技术使用者:牛芯半导体(深圳)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!