倒装芯片堆叠结构及其形成方法与流程

本公开总体上涉及半导体,并且更具体地涉及用于多芯片封装的方法。

背景技术:

1、芯片封装是现代半导体微型化的重要方面。多个集成电路(ic)被装到单个封装中,以实现同构或异构芯片集成。例如,存储芯片和控制逻辑单元可以被集成到单个封装中,以实现更低的制作成本、减小的器件占据空间和改善的器件性能。为了解决平面存储单元中的密度限制,开发出了三维(3d)存储架构。然而,随着器件特征尺寸和封装尺寸接近下限,创建足够数量的输入/输出(i/o)触点变得越来越具有挑战性,尤其是对于通过字线和位线的阵列对存储位寻址的平面存储芯片或3d存储芯片而言。

技术实现思路

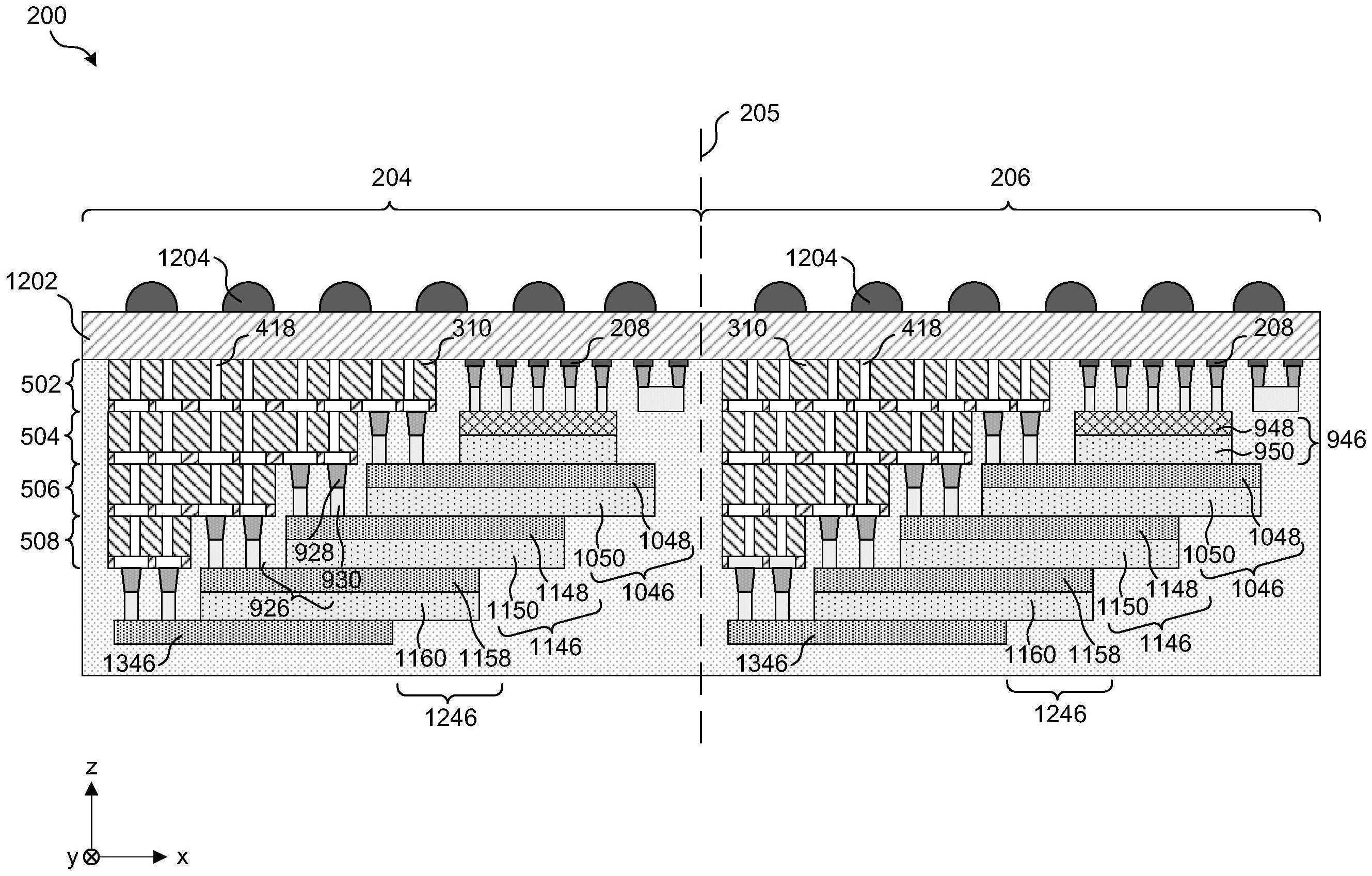

1、本公开包括半导体封装,该半导体封装包括具有与输入/输出(i/o)触点接触的第一表面和与第一表面相对的第二表面的再分布层(rdl)。该半导体封装还包括形成在rdl的第二表面上并且与rdl电连接的阶梯互连结构。该阶梯互连结构包括阶梯层,所述阶梯层包括第一阶梯层和堆叠在第一阶梯层的顶表面上的第二阶梯层。第二阶梯层覆盖第一阶梯层的顶表面的一部分,使得第一阶梯层的顶表面的剩余部分被暴露。集成电路(ic)芯片经由阶梯互连结构电连接到rdl。ic芯片中的第一ic芯片通过第一阶梯层的顶表面的剩余部分电连接到rdl。

2、本公开还包括用于形成半导体封装结构的方法。该方法包括:提供载体衬底;以及在载体衬底上形成阶梯互连结构。形成阶梯互连结构包括:形成第一阶梯层;以及在第一阶梯层的顶表面上形成第二阶梯层。第二阶梯层覆盖第一阶梯层的顶表面的一部分,使得第一阶梯层的顶表面的剩余部分被暴露。该方法还包括将集成电路(ic)芯片倒转安装在载体衬底之上和阶梯互连结构上。倒转安装ic芯片包括将ic芯片中的第一ic芯片通过第一阶梯层的顶表面的剩余部分电连接到第一阶梯层。该方法还包括采用再分布层(rdl)代替载体衬底。该方法还包括通过将第一ic芯片通过第一阶梯层的顶表面的剩余部分电连接到rdl而将ic芯片通过阶梯互连结构电连接到rdl。

技术特征:

1.一种半导体封装,包括:

2.根据权利要求1所述的半导体封装,其中,所述多个阶梯层包括第一阶梯层和第二阶梯层,所述第一阶梯层的宽度大于所述第二阶梯层的宽度。

3.根据权利要求2所述的半导体封装,其中,所述第二阶梯层相比于所述第一阶梯层更远离所述rdl。

4.根据权利要求1所述的半导体封装,其中,任意相邻的两个所述阶梯层中,远离所述rdl的阶梯层覆盖靠近所述rdl的阶梯层的顶表面的一部分,并暴露所述靠近所述rdl的阶梯层的所述顶表面的剩余部分。

5.根据权利要求1所述的半导体封装,其中,沿着远离所述rdl的方向上,所述多个ic芯片依次向靠近所述阶梯互连结构的一侧偏移。

6.根据权利要求4所述的半导体封装,其中,多个所述第一ic芯片分别通过所述柱状凸块与所述多个阶梯层的所述顶表面的所述剩余部分连接。

7.根据权利要求6所述的半导体封装,其中,所述多个第一ic芯片的端部分别位于所述多个阶梯层的所述顶表面的所述剩余部分的正上方。

8.根据权利要求6所述的半导体封装,其中,所述柱状凸块位于所述多个阶梯层的所述顶表面的所述剩余部分上。

9.根据权利要求8所述的半导体封装,其中,所述多个阶梯层分别包括多个垂直互连和多个水平互连,所述柱状凸块与所述水平互连连接。

10.根据权利要求1所述的半导体封装,其中,所述多个第一ic芯片包括nand闪速存储芯片。

11.根据权利要求1所述的半导体封装,还包括:

12.根据权利要求1所述的半导体封装,其中,所述多个第一ic芯片通过所述阶梯互连结构倒转安装在所述rdl上。

13.根据权利要求1所述的半导体封装,还包括包封所述阶梯互连结构和所述多个ic芯片的模制化合物。

14.根据权利要求1所述的半导体封装,还包括多个输入/输出(i/o)触点,所述多个i/o触点位于所述rdl的所述第一表面上。

15.一种半导体封装,包括:

16.根据权利要求15所述的半导体封装,其中,所述多个阶梯层包括第一阶梯层和第二阶梯层,所述第一阶梯层的宽度大于所述第二阶梯层的宽度。

17.根据权利要求16所述的半导体封装,其中,所述第二阶梯层相比于所述第一阶梯层更远离所述rdl。

18.根据权利要求15所述的半导体封装,其中:

19.根据权利要求18所述的半导体封装,其中,沿着远离所述rdl的方向上,所述多个ic芯片先依次向靠近所述第一侧的所述阶梯互连结构偏移,再依次向靠近所述第二侧的所述阶梯互连结构偏移。

20.根据权利要求18所述的半导体封装,其中,多个所述第一ic芯片分别通过所述柱状凸块与所述多个阶梯层的所述顶表面的所述剩余部分连接。

21.根据权利要求20所述的半导体封装,其中:

22.根据权利要求20所述的半导体封装,其中,所述柱状凸块位于所述多个阶梯层的所述顶表面的所述剩余部分上。

23.根据权利要求22所述的半导体封装,其中,所述多个阶梯层分别包括多个垂直互连和多个水平互连,所述柱状凸块与所述水平互连连接。

24.根据权利要求15所述的半导体封装,其中,所述多个第一ic芯片包括nand闪速存储芯片。

25.根据权利要求15所述的半导体封装,还包括:

26.根据权利要求15所述的半导体封装,其中,所述多个第一ic芯片通过所述阶梯互连结构倒转安装在所述rdl上。

27.根据权利要求15所述的半导体封装,还包括包封所述阶梯互连结构和所述多个ic芯片的模制化合物。

28.根据权利要求15所述的半导体封装,还包括多个输入/输出(i/o)触点,所述多个i/o触点位于所述rdl的所述第一表面上。

29.一种用于形成半导体封装结构的方法,所述方法包括:

30.根据权利要求29所述的方法,其中:

31.根据权利要求29所述的方法,其中,形成一所述阶梯层包括:

32.根据权利要求31所述的方法,其中,形成一所述阶梯层还包括:

33.根据权利要求32所述的方法,其中,形成多个水平互连包括:

34.根据权利要求30所述的方法,还包括:

技术总结

本公开包括一种半导体封装,所述半导体封装包括具有与输入/输出(I/O)触点接触的第一表面和与第一表面相对的第二表面的再分布层(RDL)。半导体封装还包括形成在RDL的第二表面上并且与RDL电连接的阶梯互连结构。该阶梯互连结构包括阶梯层,所述阶梯层包括第一阶梯层和堆叠在第一阶梯层的顶表面上的第二阶梯层。第二阶梯层覆盖第一阶梯层的顶表面的一部分,使得第一阶梯层的顶表面的剩余部分被暴露。集成电路(IC)芯片经由阶梯互连结构电连接到RDL。IC芯片中的第一IC芯片通过第一阶梯层的顶表面的剩余部分电连接到RDL。

技术研发人员:曾心如,陈鹏,王蒙,张保华,周厚德

受保护的技术使用者:长江存储科技有限责任公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!