一种用于背电极单元器件阵列拼接的装置及拼接方法

本发明涉及单元激光探测器封装,具体是指一种将多个单元激光探测器按一定间距要求在电学基板上进行共面阵列拼接并焊装的方法。

背景技术:

1、激光雷达是以发射激光束探测目标位置、速度等信息的雷达系统。其通过向目标发射激光束,然后将接收到的目标反射信号(目标回波)与发射信号进行比较,进行适当信息处理后可获得目标的相应位置、距离、形状等信息。激光雷达由激光发射机、光学接受机、转台及信息处理系统等组成。

2、在三维激光雷达探测技术中,激光探测器是激光雷达的核心部件。为提高探测的速度、分辨率及三维姿态测量能力,需要采用阵列式面阵探测器进行面阵成像。其中面阵apd激光三维成像技术使用面阵apd作为接收器件,采用激光发射源照射目标,可得到目标面阵各点的距离像,具有探测灵敏度高、空间分辨率高、距离分辨率高及成像可靠性高等优势。由于受技术封锁及研制难度大、成本较高等因素限制,目前满足应用需求的面阵apd探测器较难直接获得,这极大地影响了国内对激光三维成像技术的应用需求。

3、国内可采购到的商用高性能的apd产品主要为背电极封装形式的单元器件。在面对多元面阵应用需求时,需要将多个单元器件在引线电学基板面上高精度共面阵列拼接。通过多元的共面阵列拼接形成面阵apd探测器,再经过对拼接面阵apd探测器的工程化封装,最终获得满足应用要求的面阵apd探测器组件。为满足激光三维成像技术等面阵apd探测器的应用需求,急需一种可将单元器件进行面阵拼接焊装的技术方法。

技术实现思路

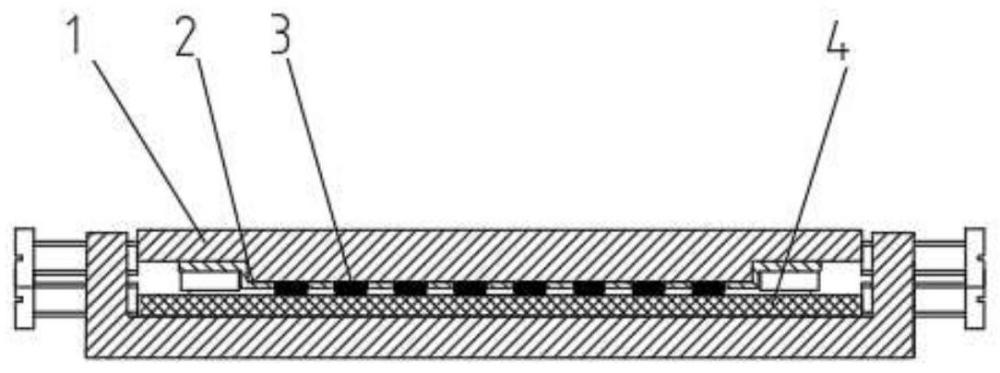

1、本发明的结构如图1所示,它包括:拼接夹具上盖1、单元器件限位架2、单元器件3、电学基板4、拼接夹具底座5、调节螺钉6。

2、其特征在于:如图1所示拼接夹具上盖1下部为单元器件限位架2,单元器件限位孔2-1中为单元器件3,单元器件3下方为电学基板4,最底部为拼接夹具底座5,拼接夹具底座5四周为调节螺钉6。

3、所述的拼接夹具上盖1材料为金属等能耐受锡焊温度的材料,形状尺寸与电学基板4一致,单元器件贴装面1-1上根据单元器件3阵列要求布置光敏面观察孔1-2,单元器件贴装面1-1四周分布限位架安装螺孔1-3。

4、所述的单元器件限位架2材料与拼接夹具上盖1一致,外形尺寸不大于拼接夹具上盖1,单元器件限位架2中间根据单元器件3阵列要求布置单元器件限位孔2-1,限位孔尺寸与单元器件3外形尺寸相匹配。

5、所述的单元器件3,形状为长方形,中心位置为单元器件光敏面3-1,背面为单元器件焊接面3-2。

6、所述的电学基板4,材料为pcb、蓝宝石或陶瓷,电学基板4表面可进行单元器件3阵列焊接。

7、所述的拼接夹具底座5材料与拼接夹具上盖1,四周为底座侧墙5-1,底座侧墙5-1下方为电学基板调节孔5-2,上方为上盖调节孔5-3。拼接夹具上盖1以及电学基板4可嵌入拼接夹具底座5中。

8、所述的调节螺钉6为不锈钢螺钉,规格尺寸与电学基板调节孔5-2,以及上盖调节孔5-3相匹配。

9、本发明的用于背电极单元器件阵列拼接的装置的拼接方法的实现过程如下:

10、1.通过限位架安装螺钉2-2将单元器件限位架2固定至拼接夹具上盖1上;

11、2.将单元器件3逐个通过胶接固定至单元器件限位孔2-1中,使单元器件光敏面3-1固定至单元器件贴装面1-1上,固化后可透过光敏面观察孔1-2检查单元器件3情况;

12、3.在电学基板4表面印刷锡膏,并将电学基板放置于拼接夹具底座5中;

13、4.通过调节螺钉6调节电学基板4与拼接夹具底座5居中并固定,实现电学基板4与拼接夹具底座5对准安装;

14、5.将安装有阵列单元器件3的拼接夹具上盖1放置在电学基板4上;

15、6.通过调节螺钉6调节拼接夹具上盖1与拼接夹具底座5居中并固定,实现单元器件3与电学基板4对准安装;

16、7.将组装好的拼接夹具底座5放置在加热炉中加热焊接;

17、8.将焊接后的拼接夹具上盖1与电学基板4从拼接夹具底座5中取出;

18、9.使用溶剂浸泡单元器件光敏面3-1与单元器件贴装面1-1间的胶,将拼接夹具上盖1从单元器件3上分离,获得阵列拼接单元器件3的电学基板4。

19、本发明的优点是:

20、1.本发明结构简单,制备成本低;

21、2.本发明操作简便,操作重复性好;

22、3.本发明适用于各种规模、各种间距的阵列单元器件的拼接;

技术特征:

1.一种用于背电极单元器件阵列拼接的装置,包括拼接夹具上盖(1)、单元器件限位架(2)、单元器件(3)、电学基板(4)、拼接夹具底座(5)、调节螺钉(6),其特征在于:

2.根据权利要求1所述的一种用于背电极单元器件阵列拼接的装置,其特征在于:所述的拼接夹具上盖(1)材料为金属等能耐受锡焊温度的材料,形状尺寸与电学基板(4)一致,单元器件贴装面(1-1)上根据单元器件(3)阵列要求布置光敏面观察孔(1-2),单元器件贴装面(1-1)四周分布限位架安装螺孔(1-3)。

3.根据权利要求1所述的一种用于背电极单元器件阵列拼接的装置,其特征在于:所述的单元器件限位架(2)材料与拼接夹具上盖(1)一致,外形尺寸不大于拼接夹具上盖(1),单元器件限位架(2)中间根据单元器件(3)阵列要求布置单元器件限位孔(2-1),限位孔尺寸与单元器件(3)外形尺寸相匹配。

4.根据权利要求1所述的一种用于背电极单元器件阵列拼接的装置,其特征在于:所述的单元器件(3),形状为长方形,中心位置为单元器件光敏面(3-1),背面为单元器件焊接面(3-2)。

5.根据权利要求1所述的一种用于背电极单元器件阵列拼接的装置,其特征在于:所述的电学基板(4),材料为pcb、蓝宝石或陶瓷,电学基板(4)表面进行单元器件(3)阵列焊接。

6.根据权利要求1所述的一种用于背电极单元器件阵列拼接的装置,其特征在于:所述的拼接夹具底座(5)材料与拼接夹具上盖(1),四周为底座侧墙(5-1),底座侧墙(5-1)下方为电学基板调节孔(5-2),上方为上盖调节孔(5-3)。

7.根据权利要求1所述的一种用于背电极单元器件阵列拼接的装置,其特征在于:所述的调节螺钉(6)为不锈钢螺钉。

8.一种基于如权利要求1所述一种用于背电极单元器件阵列拼接的装置的拼接方法,其特征包括以下步骤:

技术总结

本发明公开了一种用于背电极单元器件阵列拼接的装置及拼接方法。在背电极单元器件阵列共面成型的实现方法中,主要由拼接夹具上盖、单元器件限位架、单元器件、电学基板、拼接夹具底座等组成。本专利可以实现将背电极单元器件在电学极板上按一定间距阵列拼接成面阵探测器。该实现方法解决了单元器件向面阵器件的拼接封装问题,是一种低成本,操作简便,高拼接精度的背电极单元器件的阵列共面成型的实现方法。

技术研发人员:蒋梦蝶,孙闻,徐琳,赵振力,张磊,李雪

受保护的技术使用者:中国科学院上海技术物理研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!