一种新型的SGT制作方法及结构与流程

本发明涉及芯片半导体,具体为一种新型的sgt制作方法。

背景技术:

1、sgt mosfet是一种新型的功率半导体器件,具有传统深沟槽mosfet的低导通损耗的优点,同时具有更加低的开关损耗。sgt mosfet作为开关器件应用于新能源电动车、新型光伏发电、节能家电等领域的电机驱动系统、逆变器系统及电源管理系统,是核心功率控制部件。

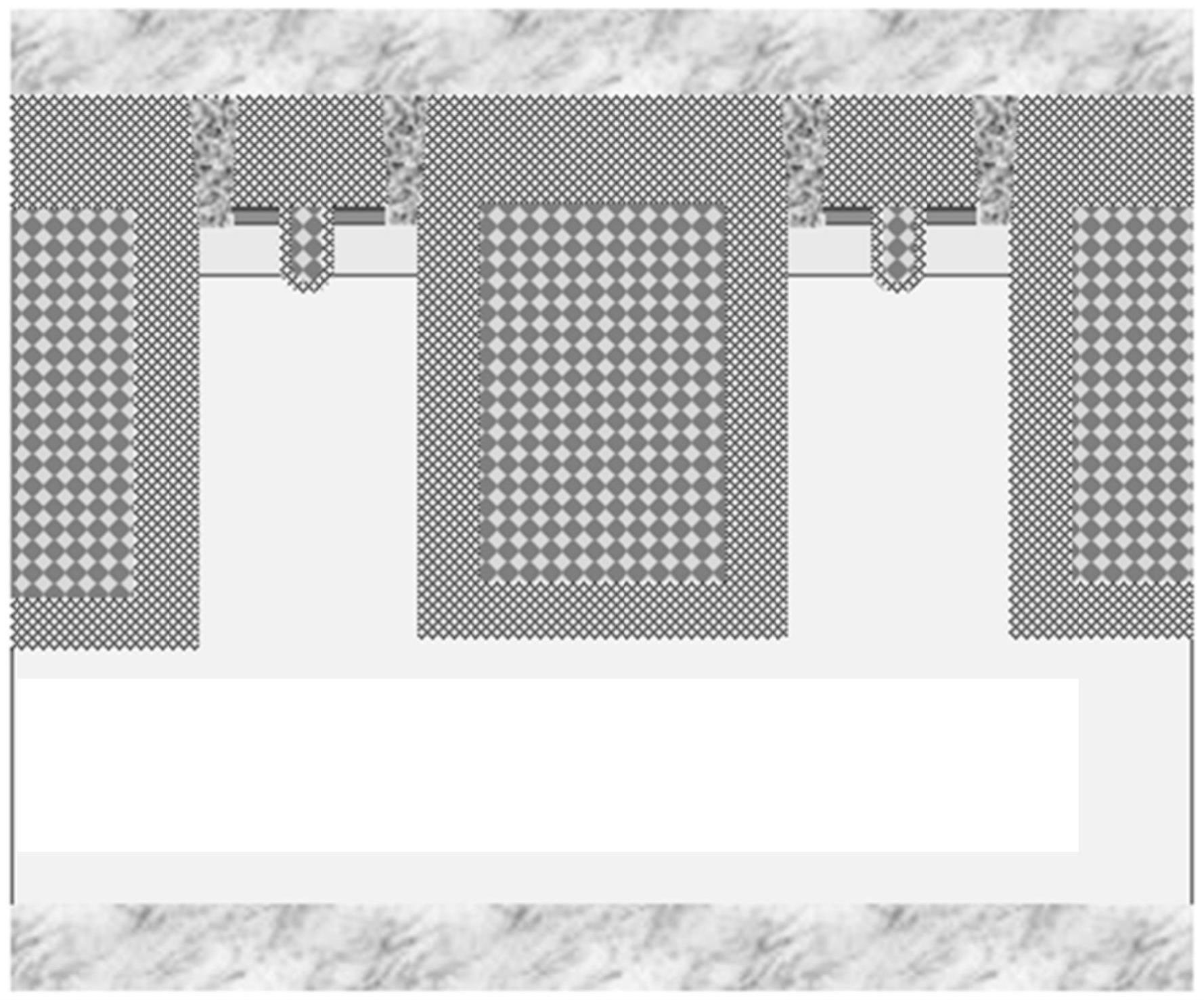

2、请参阅图1,现有的sgt功率管结构如图1所示,第一层多晶硅和第二层多晶硅在同一个沟槽内,当工艺波动时,容易形成栅极和源极之间的漏电通道,造成栅源漏电。而且由于第一层多晶硅和第二层多晶硅在同一个沟槽内,不仅造成工艺较为复杂,需要七次光刻工艺,同时也会造成顶部第二层多晶硅,即栅极多晶硅的工艺受限,比如深度以及宽度等等。

3、本发明公开了一种新型的sgt制作方法及结构,以解决上述技术问题。

技术实现思路

1、本发明提供了一种新型的sgt制作方法及结构,具备光刻次数减少,成本更低、彻底解决了栅源漏电问题的优点,解决现有技术中流程复杂、成本高以及栅源漏电问题等技术问题。

2、为实现上述目的,本发明提供如下技术方案:一种新型的sgt制作方法,包括如下步骤:

3、步骤s1:在硅表面使用薄膜工艺沉积200a-300a的二氧化硅;使用薄膜工艺沉积1500a-2500a的氮化硅;

4、步骤s2:使用光刻工艺曝光出第一沟槽的图形;使用干法刻蚀工艺刻蚀出沟槽,深度5um-6um;

5、步骤s3:使用扩散工艺生长栅极二氧化硅1000a;使用薄膜工艺沉积3000a-4000a的二氧化硅;

6、步骤s4:使用薄膜工艺沉积多晶硅8000a,然后通过刻蚀将多余的多晶硅刻蚀掉,与衬底硅平面水平;湿法去掉步骤s3在单晶硅表面形成二氧化硅,以及去掉表层的氮化硅;

7、步骤s5:使用光刻工艺曝光第二沟槽,即栅极沟槽图形;使用干法刻蚀工艺刻蚀出沟槽,沟槽宽度为0.2um~0.35um,深度为0.7um~1.5um;使用炉管工艺生长250a~1000a的栅极氧化物二氧化硅;使用薄膜工艺沉积多晶硅2000a~8000a,形成栅极;使用干法刻蚀回刻多晶硅,与衬底硅表面平齐;

8、步骤s6:使用普注的离子注入工艺,注入形成体区;使用光刻工艺曝光出源极图形,离子注入形成源极区域;

9、步骤s7:沉积氧化层形成层间介质层,光刻曝光出接触孔图形,通过干法刻蚀形成接触孔;接触孔离子注入,与体区同型,进行接触工艺,沉积ti/tin/w,引出接触孔;

10、步骤s8:后续为正常的正面金属工艺,钝化层沉积,钝化层开孔,背面减薄以及背部金属工艺。

11、为了解决上述技术问题,本发明提供一种新型的sgt结构,所述一种新型的sgt结构由上述的一种新型的sgt制作方法制成。

12、与现有技术相比,本发明的有益效果是:

13、与现有的结构相比,本发明提供的一种新型的sgt制作方法及结构,新结构的工艺流程更为简单,光刻次数减少,成本更低,而且两次多晶硅工艺分别位于两个独立的沟槽内,彻底解决了栅源漏电问题。同时栅极多晶硅位于独立的第二沟槽内,可对栅极进行单独调试,器件参数的可调试范围更大,工艺调试也更为简单。

14、通过新的结构和新的工艺,能够使100v sgt的pitch从旧结构的2.5um缩小到2.1um,极大的提升了芯片的集成度,同样面积下,ron能够提升10%左右。

技术特征:

1.一种新型的sgt制作方法,其特征在于,包括如下步骤:

2.一种新型的sgt结构,其特征在于:所述一种新型的sgt结构由权利要求1所述的一种新型的sgt制作方法制成。

技术总结

本发明公开了一种新型的SGT制作方法,包括如下步骤:使用光刻工艺曝光第二沟槽,即栅极沟槽图形;使用干法刻蚀工艺刻蚀出沟槽,沟槽宽度为0.2um~0.35um,深度为0.7um~1.5um;使用炉管工艺生长250A~1000A的栅极氧化物二氧化硅;使用薄膜工艺沉积多晶硅2000A~8000A,形成栅极;使用干法刻蚀回刻多晶硅,与衬底硅表面平齐;使用普注的离子注入工艺,注入形成体区;使用光刻工艺曝光出源极图形,离子注入形成源极区域;本发明公开了一种新型的SGT结构,本发明具备光刻次数减少,成本更低、彻底解决了栅源漏电问题的优点等优点。

技术研发人员:陈佳旅,何昌,杨勇,朱勇华,张光亚

受保护的技术使用者:深圳市美浦森半导体有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!