一种LED芯片及其制备方法与流程

本发明涉及半导体,特别涉及一种led芯片及其制备与使用方法。

背景技术:

1、led(light-emitting diode,发光二极管)作为固态主动发光光源,具有节能环保、高效率、高寿命、高亮度、高色纯度、低能耗、响应时间快等优点,通常可以实现更高的耐久性、更紧凑的体积和更高的设计灵活性,被广泛应用于照明、显示、背光源、车载等领域。

2、由于led芯片所面临的使用条件和环境各种各样,尤其是在户内外显示屏使用环境更加严苛。在显示屏终端应用过程中受到高温、水汽、化学腐蚀等环境影响。而目前led芯片常见的电极金属材料包括ni、gr、al、ti、pt、au等,led芯片在外加电场以及水汽、卤素引入的情况下,当水汽渗入到芯片表面,金属元素可被电解形成离子态,此时如果施加正向电压,p电极电解出的金属离子会沿着电场方向迁移;若施加逆向电压,n电极电解出的金属离子会沿着电场方向迁移,并且,在封装体内存在卤素电子的条件下,卤素电子易与金属离子结合,将加速金属的迁移,使得电极出现金属迁移异常。而金属迁移导致正负极之间发生短路而死灯异常甚至电极脱落,严重影响发光二极管的使用。

技术实现思路

1、基于此,本发明的目的是提供一种led芯片及其制备方法,解决现有技术中的led芯片在恶劣环境下工作,电极容易发生金属迁移,导致电极脱落的问题。

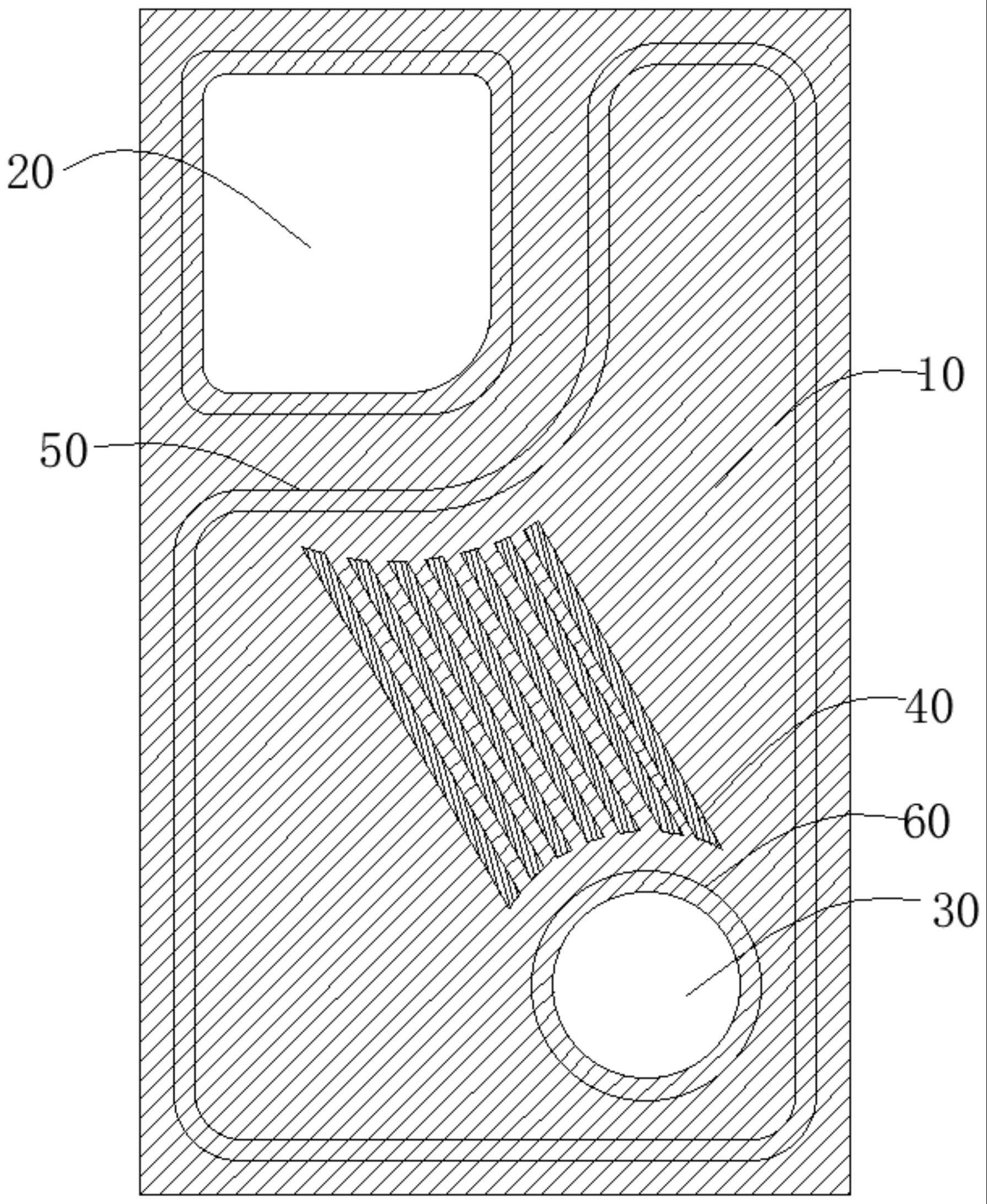

2、本发明提供一种led芯片,包括led外延层、设置在所述外延层上的电极、以及设置在所述led外延层上且覆盖所述电极的钝化层,所述电极包括p型电极和n型电极,所述钝化层上开设有凹槽,所述p型电极和所述n型电极通过所述凹槽至少部分裸露用于打线,所述钝化层包括第一钝化子层和设置在所述第一钝化子层上的第二钝化子层,其中,所述第二钝化子层在位于所述p型电极和所述n型电极之间的部位上设有沟槽或孔洞。

3、本发明中的led芯片,通过在电极外侧设置钝化层,由于钝化层位于p型电极和n型电极之间的金属迁移的路径上,使得p型电极和n型电极之间的横向金属迁移速率受到限制,又由于在钝化层上开设凹槽,使p型电极和n型电极只部分裸露于钝化层用于打线,使得两电极之间发生金属迁移时,需要先向上迁移再横向迁移,改变了金属迁移方向,提高了芯片抗金属迁移性能,具体的,钝化层包括第一钝化子层和设置在第一钝化子层上的第二钝化子层,第一钝化子层用于防止水汽进入电极内,第二钝化子层上设有沟槽或孔洞,使得两电极之间的路径上下起伏,水汽附着在上下起伏的路径上形成迁移路径,相对应平坦的路径需要更多的量,因此变相增强了芯片的抗金属迁移能力。因此本发明解决了现有技术中的led芯片在恶劣环境下工作,电极容易发生金属迁移,导致电极脱落的问题。

4、优选地,所述第一钝化子层的材料为sio2、al2o3及sinx中的一种,所述第二钝化子层的材料为sio2或sinx,所述第一钝化子层的防水性能高于所述第二钝化子层的防水性能。

5、优选地,所述第一钝化子层的厚度为所述第二钝化子层的厚度为

6、优选地,所述沟槽的为长条状,所述沟槽的宽度为3μm-10μm,所述沟槽的深度与所述第二钝化子层一致,相邻两所述沟槽之间的间距为3μm-6μm。

7、优选地,所述孔洞的直径为3μm-10μm,所述孔洞的深度与所述第二钝化子层一致,相邻两所述孔洞之间的间距为3μm-6μm。

8、优选地,所述led外延片还包括衬底、n型半导体、量子阱层、p型半导体和透明导电层;

9、所述电极和所述钝化层层叠在所述透明导电层上,其中,通过刻蚀去除部分所述n型半导体上的所述量子阱层和所述p型半导体,所述p型电极和所述n型电极分别通过所述透明导电层与所述n型半导体和所述p型半导体连接。

10、优选地,所述p型半导体与所述n型半导体交界处为n型半导体台阶线,所述钝化层与所述p型电极交界处为p型电极包覆线,靠近所述n型半导体的所述沟槽或所述孔洞距离所述n型半导体台阶线的距离为4μm-10μm,靠近所述p型半导体的所述沟槽或所述孔洞距离所述p型电极包覆线的距离为4μm-10μm。

11、本发明还提供一种led芯片制备方法,方法包括:

12、制备led外延层,并在所述led外延层上依次生长,并在所述led外延层上依次生长电极和钝化层,所述钝化层包括第一钝化子层和第二钝化子层,所述电极包括p型电极和n型电极;

13、在上述结构上进行光刻胶涂布,并利用光刻技术露出部分所述p型电极和所述n型电极上的所述钝化层,并用刻蚀技术去除部分钝化层,使得所述p型电极和所述n型电极部分裸露用于打线;

14、再通过光刻技术和刻蚀技术,去除所述p型电极和所述n型电极之间的所述第二钝化子层以生成沟槽或孔洞。

15、优选地,所述在所述p型半导体和所述n型半导体上依次生长所述透明导电层、电极和钝化层,所述钝化层包括第一钝化子层和第二钝化子层,所述电极包括p型电极和n型电极的步骤包括:

16、通过镀膜设备在所述p型半导体和所述n型半导体镀所述透明导电层,并通过光刻和湿法刻蚀技术,在所述透明导电层上制备电极图层;

17、通过金属镀膜设备在电极图层上制备所述p型电极和所述n型电极;

18、在上述结构上通过ald设备沉积所述第一钝化子层;

19、通过pecvd技术在所第一钝化子层上沉积所述第二钝化子层。

20、优选地,所述在上述结构上进行光刻胶涂布,并利用光刻技术露出部分所述p型电极和所述n型电极上的所述钝化层,并用刻蚀技术去除部分钝化层,使得所述p型电极和所述n型电极部分裸露用于打线步骤包括:

21、先用湿法刻蚀技术刻蚀所述第二钝化子层,再用icp干法刻蚀技术刻蚀所述第一钝化子层,所述湿法刻蚀技术采用的溶液为boe溶液。

技术特征:

1.一种led芯片,其特征在于,包括led外延层、设置在所述外延层上的电极、以及设置在所述led外延层上且覆盖所述电极的钝化层,所述电极包括p型电极和n型电极,所述钝化层上开设有凹槽,所述p型电极和所述n型电极通过所述凹槽至少部分裸露;

2.根据权利要求1所述的led芯片,其特征在于,所述第一钝化子层的材料为sio2、al2o3及sinx中的一种,所述第二钝化子层的材料为sio2或sinx,所述第一钝化子层的防水性能高于所述第二钝化子层的防水性能。

3.根据权利要求1所述的led芯片,其特征在于,所述第一钝化子层的厚度为所述第二钝化子层的厚度为

4.根据权利要求1所述的led芯片,其特征在于,所述沟槽的为长条状,所述沟槽的宽度为3μm-10μm,所述沟槽的深度与所述第二钝化子层一致,相邻两所述沟槽之间的间距为3μm-6μm。

5.根据权利要求1所述的led芯片,其特征在于,所述孔洞的直径为3μm-10μm,所述孔洞的深度与所述第二钝化子层一致,相邻两所述孔洞之间的间距为3μm-6μm。

6.根据权利要求1所述的led芯片,其特征在于,所述led外延片还包括衬底、以及依次层叠在所述衬底上的n型半导体、量子阱层、p型半导体和透明导电层;

7.根据权利要求6所述的led芯片,其特征在于,所述p型半导体与所述n型半导体交界处为n型半导体台阶线,所述钝化层与所述p型电极交界处为p型电极包覆线,靠近所述n型半导体的所述沟槽或所述孔洞距离所述n型半导体台阶线的距离为4μm-10μm,靠近所述p型半导体的所述沟槽或所述孔洞距离所述p型电极包覆线的距离为4μm-10μm。

8.一种led芯片的制备方法,其特征在于,用于制备1至7任一项权利要求所述的led芯片,所述方法包括:

9.根据权利要求8所述的led芯片的制备方法,其特征在于,所述在所述p型半导体和所述n型半导体上依次生长所述透明导电层、电极和钝化层,所述钝化层包括第一钝化子层和第二钝化子层,所述电极包括p型电极和n型电极的步骤包括:

10.根据权利要求8所述的led芯片制备方法,其特征在于,所述在上述结构上进行光刻胶涂布,并利用光刻技术露出部分所述p型电极和所述n型电极上的所述钝化层,并用刻蚀技术去除部分钝化层,使得所述p型电极和所述n型电极部分裸露用于打线步骤包括:

技术总结

本发明提供一种LED芯片及其制备方法,其中LED芯片包括LED外延层、设置在外延层上的电极、以及设置在LED外延层上且覆盖所述电极的钝化层,所述电极包括P型电极和N型电极,所述钝化层上开设有凹槽,所述P型电极和所述N型电极通过所述凹槽至少部分裸露;所述钝化层包括第一钝化子层和设置在所述第一钝化子层上的第二钝化子层,其中,所述第二钝化子层在位于所述P型电极和所述N型电极之间的部位上设有沟槽或孔洞。本发明中的LED芯片,通过第一钝化子层和第二钝化子层来对电极进行保护,在通过第二钝化子层上的孔洞或沟槽延长两电极间的距离,以阻止金属迁移,解决了现有技术中的LED芯片在恶劣环境下工作,电极容易发生金属迁移,导致电极脱落的问题。

技术研发人员:张星星,张雪,林潇雄,胡加辉,金从龙

受保护的技术使用者:江西兆驰半导体有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!