影像感测模组、显示模组及电子设备的制作方法

本申请涉及芯片封装,特别是涉及一种影像感测模组、显示模组及电子设备。

背景技术:

1、目前,在影像感测模组的制造过程中,需要将影像传感器和图像处理器封装在一起得到影像感测模组,但是相关技术中影像感测模组整体较厚,难以满足轻薄化的使用需求。

技术实现思路

1、基于此,有必要提供一种影像感测模组、显示模组及电子设备,以减小影像感测模组整体的厚度,满足轻薄化的使用需求。

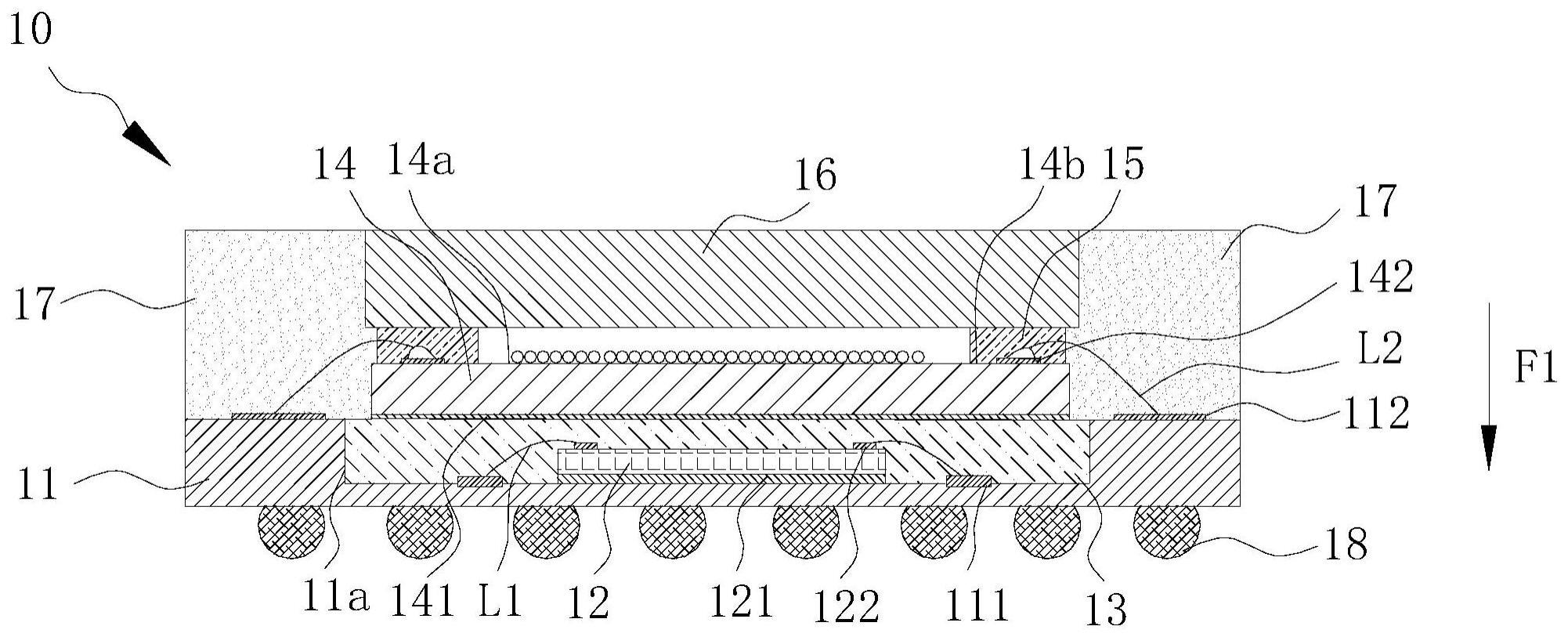

2、根据本申请的第一方面,提供一种影像感测模组,包括:

3、基板,设有凹槽;及

4、处理芯片和密封结构,处理芯片与基板电性连接,处理芯片借助于密封结构封装于凹槽内。

5、在其中一个实施例中,密封结构的至少部分位于凹槽内。

6、在其中一个实施例中,密封结构在凹槽的槽口所在平面上的正投影,与凹槽在凹槽的槽口所在平面上的正投影彼此重合。

7、在其中一个实施例中,密封结构的一部分位于凹槽内,另一部分位于凹槽外。

8、在其中一个实施例中,定义密封结构位于凹槽外的部分为目标部分;

9、凹槽在凹槽的槽口所在平面上的正投影,位于目标部分在凹槽的槽口所在平面上的正投影内。

10、在其中一个实施例中,影像感测模组还包括第一焊盘和第一连接导线;

11、第一焊盘电性连接基板,处理芯片借助于第一连接导线连接于第一焊盘;

12、其中,第一焊盘和第一连接导线均封装于密封结构内;

13、第一焊盘在凹槽的槽口所在平面上的正投影,位于凹槽在凹槽的槽口所在平面上的正投影外。

14、在其中一个实施例中,密封结构背离凹槽的底壁的一侧表面,与凹槽的槽口所在平面彼此平行。

15、在其中一个实施例中,影像感测模组还包括感测芯片;

16、感测芯片设于密封结构背离处理芯片的一侧表面,且感测芯片电性连接于基板。

17、在其中一个实施例中,感测芯片具有感测区和围绕感测区的边缘区;

18、影像感测模组还包括:

19、粘结层,设于边缘区;及

20、盖板,盖板借助粘结层与感测芯片相连接。

21、在其中一个实施例中,影像感测模组还包括封装结构;

22、封装结构设于基板远离凹槽的底壁的一侧表面上,且封装结构配置为具有空腔;

23、盖板和感测芯片容置于空腔。

24、在其中一个实施例中,感测芯片借助于焊线工艺电性连接于基板。

25、根据本申请的第二方面,提供一种显示模组,包括如前述任一项实施例的影像感测模组。

26、根据本申请的第三方面,提供一种电子设备,包括如前述的显示模组。

27、上述的影像感测模组、显示模组及电子设备中,该影像感测模组至少包括基板、处理芯片和密封结构。通过将处理芯片设于基板提供的凹槽内,借助密封结构封装该处理芯片,能够减薄影像感测模组的厚度,满足轻薄化的使用需求。

技术特征:

1.一种影像感测模组,其特征在于,包括:

2.根据权利要求1所述的影像感测模组,其特征在于,所述密封结构的至少部分位于所述凹槽内。

3.根据权利要求2所述的影像感测模组,其特征在于,所述密封结构在所述凹槽的槽口所在平面上的正投影,与所述凹槽在所述凹槽的槽口所在平面上的正投影彼此重合。

4.根据权利要求2所述的影像感测模组,其特征在于,所述密封结构的一部分位于所述凹槽内,另一部分位于所述凹槽外。

5.根据权利要求4所述的影像感测模组,其特征在于,定义所述密封结构位于所述凹槽外的部分为目标部分;

6.根据权利要求5所述的影像感测模组,其特征在于,所述影像感测模组还包括第一焊盘和第一连接导线;

7.根据权利要求1-6任一项所述的影像感测模组,其特征在于,所述密封结构背离所述凹槽的底壁的一侧表面,与所述凹槽的槽口所在平面彼此平行。

8.根据权利要求1-6任一项所述的影像感测模组,其特征在于,所述影像感测模组还包括感测芯片;

9.根据权利要求8所述的影像感测模组,其特征在于,所述感测芯片具有感测区和围绕所述感测区的边缘区;

10.根据权利要求9所述的影像感测模组,其特征在于,所述影像感测模组还包括封装结构;

11.根据权利要求8所述的影像感测模组,其特征在于,所述感测芯片借助于焊线工艺电性连接于所述基板。

12.一种显示模组,其特征在于,包括如权利要求1-11任一项所述的影像感测模组。

13.一种电子设备,其特征在于,包括如权利要求12所述的显示模组。

技术总结

本申请涉及一种影像感测模组、显示模组及电子设备,该影像感测模组,包括基板、处理芯片和密封结构;基板设有凹槽;处理芯片与基板电性连接,处理芯片借助于密封结构封装于凹槽内。本申请通过将处理芯片设于基板提供的凹槽内,借助密封结构封装该处理芯片,能够减薄影像感测模组的厚度,满足轻薄化的使用需求,而且后续的感测芯片可以直接在该密封结构上再次进行封装,如此,感测芯片和处理芯片能够共用一个基板,在封装处理芯片和感测芯片前后,不需翻转基板,也不需要设置其他中间层来封装处理芯片,有效简化多芯片的封装工艺,提高封装效率。

技术研发人员:张正芳,庄伟仲,佘庆威

受保护的技术使用者:业泓科技(成都)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!