一种功率半导体器件及其制备方法、芯片与流程

本申请属于功率器件,尤其涉及一种功率半导体器件及其制备方法、芯片。

背景技术:

1、碳化硅(sic)的带隙宽度大约是硅的三倍,临界电场强度是硅的十倍,热导率是硅的三倍,在用作功率金属氧化物半导体场效应晶体管(metal-oxide-se miconductorfield-effect transistor,mosfet)时,其具有比硅更快的开关速度、更低的开关损耗和更高的工作温度范围。mosfet通常由元胞区和终端区构成,终端可以有效减小局部电场,提高器件击穿电压(breakdown voltage,bv)及可靠性,常用的终端结构有场板(fp)结构、场限环(flr)结构、结终端扩展(jte)结构和横向变掺杂(vld)结构等。目前普遍采用的结构是flr结构、jte结构和基于二者的组合结构。

2、然而,flr结构需要占用较大的终端面积,并且其击穿电压对环间距敏感,jte结构可以减小终端面积,但其耐压对活化掺杂浓度非常敏感,无法实现在占用较小的终端面积的情况下实现与flr结构相同的击穿电压。

技术实现思路

1、为了解决上述技术问题,本申请实施例提供了一种功率半导体器件及其制备方法、芯片,可以在设定的击穿电压下占用较小的终端面积。

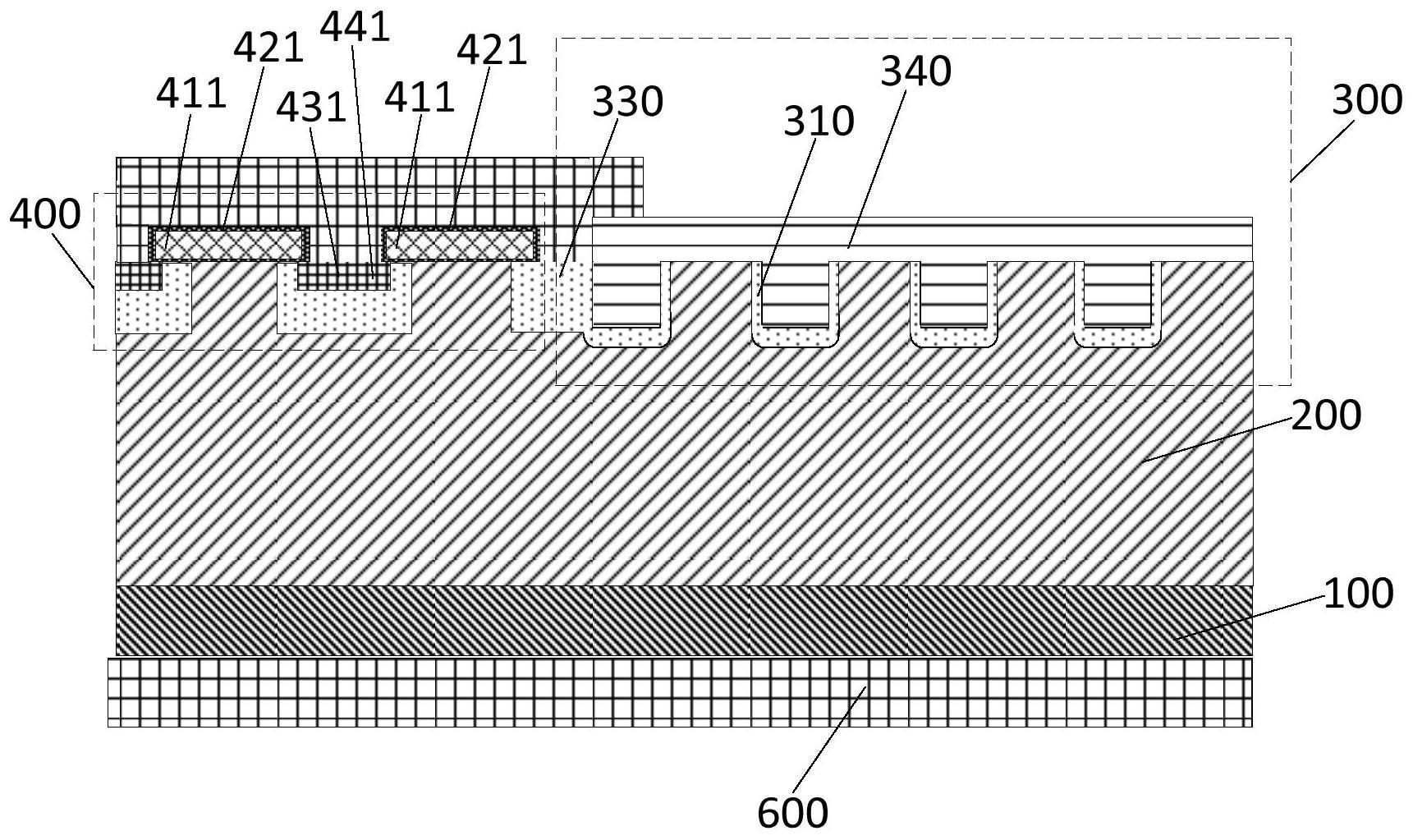

2、本申请实施例第一方面提供了一种功率半导体器件,所述功率半导体器件包括:漏极层、n型衬底层、n型漂移层、元胞结构、终端结构以及源极层,其中,所述元胞结构形成于所述n型漂移层与所述源极层之间;

3、所述终端结构包括终端扩展区、多个p型掺杂区以及介质层;

4、所述终端扩展区位于所述n型漂移层上,且所述终端扩展区分别与所述源极层和所述介质层接触,并与最靠近所述元胞结构的p型掺杂区相邻;

5、所述p型掺杂区位于对应的所述终端沟槽的槽底和侧壁;

6、所述介质层覆盖于所述终端沟槽、所述p型掺杂区以及所述终端扩展区的部分区域上,对所述终端沟槽进行填充。

7、在一个实施例中,所述p型掺杂区与所述终端沟槽的槽底之间形成平面pn结,所述p型掺杂区与所述终端沟槽的槽壁之间形成柱面pn结,所述p型掺杂区与所述终端沟槽的底部拐角区之间形成球面pn结。

8、在一个实施例中,所述终端沟槽的宽度与第一距离呈反比例关系,所述第一距离为所述终端扩展区与最靠近所述元胞结构的终端沟槽之间的距离。

9、在一个实施例中,相邻的所述终端沟槽之间的距离相等。

10、在一个实施例中,所述p型掺杂区的底部的上表面与所述终端扩展区的下表面齐平。

11、在一个实施例中,相邻的所述终端沟槽之间的n型漂移层的宽度小于所述终端沟槽的宽度。

12、在一个实施例中,所述元胞结构包括:第一栅极多晶硅、第二栅极多晶硅、第一栅极介质层、第二栅极介质层、p型基区、n型沟道区;

13、所述第一栅极多晶硅和所述第二栅极多晶硅分别设于所述n型漂移层上,所述第一栅极介质层用于包裹所述第一栅极多晶硅,所述第二栅极介质层用于包裹所述第二栅极多晶硅,所述p型基区分别与所述第一栅极介质层和所述第二栅极介质层接触;所述n型沟道区设于所述第一栅极多晶硅和所述第二栅极多晶硅之间,且与所述p型基区和所述源极层接触。

14、在一个实施例中,所述p型基区为凹形结构,所述n型沟道区位于所述凹形结构的凹槽内,所述凹形结构的两侧凸起部分别与所述第一栅极介质层和所述第二栅极介质层接触。

15、本申请实施例第二方面还提供了一种功率半导体器件的制备方法,包括:

16、在n型衬底层上形成n型漂移层;

17、在所述n型漂移层上的第一区域形成多个终端沟槽;

18、向所述第一区域注入p型掺杂离子形成终端扩展区、多个p型掺杂区;其中,所述p型掺杂区位于对应的所述终端沟槽的槽底和侧壁;所述终端扩展区与第一个终端沟槽相邻;

19、填充介质材料形成介质层,所述介质层覆盖于所述终端沟槽、所述p型掺杂区上;

20、在所述n型漂移层上的第二区域形成元胞结构;

21、形成与所述终端扩展区和元胞结构接触的源极层,在所述n型衬底的背面形成漏极层。

22、本申请实施例第三方面还提供了一种芯片,如上述任一项实施例所述的功率半导体器件;或者包括上述任一项实施例所述的功率半导体器件的制备方法制备的功率半导体器件。

23、本申请实施例的有益效果:在n型漂移层与源极层之间形成元胞结构,在n型漂移层上形成包括终端扩展区、终端沟槽、p型掺杂区以及介质层的终端结构;终端扩展区位于n型漂移层上,且终端扩展区分别与源极层和介质层接触,并与最靠近元胞结构的终端沟槽相邻;p型掺杂区位于对应的终端沟槽的槽底和槽壁;介质层覆盖于终端沟槽、p型掺杂区上,通过终端沟槽截断p型掺杂区与沟槽侧壁之间形成的柱面结,使得沟槽下方的p型掺杂区部分更接近平面pn结,减少了电场的集中,并通过对终端沟槽进行填充介质材料,可以承受较高的临界电场,从而在更小的终端宽度下提升了击穿电压,进而实现在设定的击穿电压下占用较小的终端面积。

技术特征:

1.一种功率半导体器件,其特征在于,所述功率半导体器件包括:漏极层、n型衬底层、n型漂移层、元胞结构、终端结构以及源极层,其中,所述元胞结构形成于所述n型漂移层与所述源极层之间;

2.如权利要求1所述的功率半导体器件,其特征在于,所述p型掺杂区与所述终端沟槽的槽底之间形成平面pn结,所述p型掺杂区与所述终端沟槽的槽壁之间形成柱面pn结,所述p型掺杂区与所述终端沟槽的底部拐角区之间形成球面pn结。

3.如权利要求1所述的功率半导体器件,其特征在于,所述终端沟槽的宽度与第一距离呈反比例关系,所述第一距离为所述终端扩展区与最靠近所述元胞结构的终端沟槽之间的距离。

4.如权利要求1所述的功率半导体器件,其特征在于,相邻的所述终端沟槽之间的距离相等。

5.如权利要求1所述的功率半导体器件,其特征在于,所述p型掺杂区的底部的上表面与所述终端扩展区的下表面齐平。

6.如权利要求1所述的功率半导体器件,其特征在于,相邻的所述终端沟槽之间的n型漂移层的宽度小于所述终端沟槽的宽度。

7.如权利要求1-6任一项所述的功率半导体器件,其特征在于,所述元胞结构包括:第一栅极多晶硅、第二栅极多晶硅、第一栅极介质层、第二栅极介质层、p型基区、n型沟道区;

8.如权利要求7所述的功率半导体器件,其特征在于,所述p型基区为凹形结构,所述n型沟道区位于所述凹形结构的凹槽内,所述凹形结构的两侧凸起部分别与所述第一栅极介质层和所述第二栅极介质层接触。

9.一种功率半导体器件的制备方法,其特征在于,包括:

10.一种芯片,其特征在于,如权利要求1-8任一项所述的功率半导体器件;或者包括如权利要求9所述的功率半导体器件的制备方法制备的功率半导体器件。

技术总结

本申请属于功率器件技术领域,提供了一种功率半导体器件及其制备方法、芯片,在N型漂移层与源极层之间形成元胞结构,在N型漂移层上形成包括终端扩展区、终端沟槽、P型掺杂区以及介质层的终端结构;终端扩展区位于N型漂移层上,且终端扩展区分别与源极层和介质层接触,并与最靠近元胞结构的终端沟槽相邻;P型掺杂区位于对应的终端沟槽的槽底和槽壁;介质层覆盖于终端沟槽、P型掺杂区上,通过终端沟槽截断P型掺杂区与沟槽侧壁之间形成的柱面结,使得沟槽下方的P型掺杂区部分更接近平面PN结,减少了电场的集中,并通过对终端沟槽进行填充介质材料,可以承受较高的临界电场,从而在更小的终端宽度下提升了击穿电压。

技术研发人员:乔凯

受保护的技术使用者:天狼芯半导体(成都)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!