静电放电器件及包括该静电放电器件的显示驱动芯片的制作方法

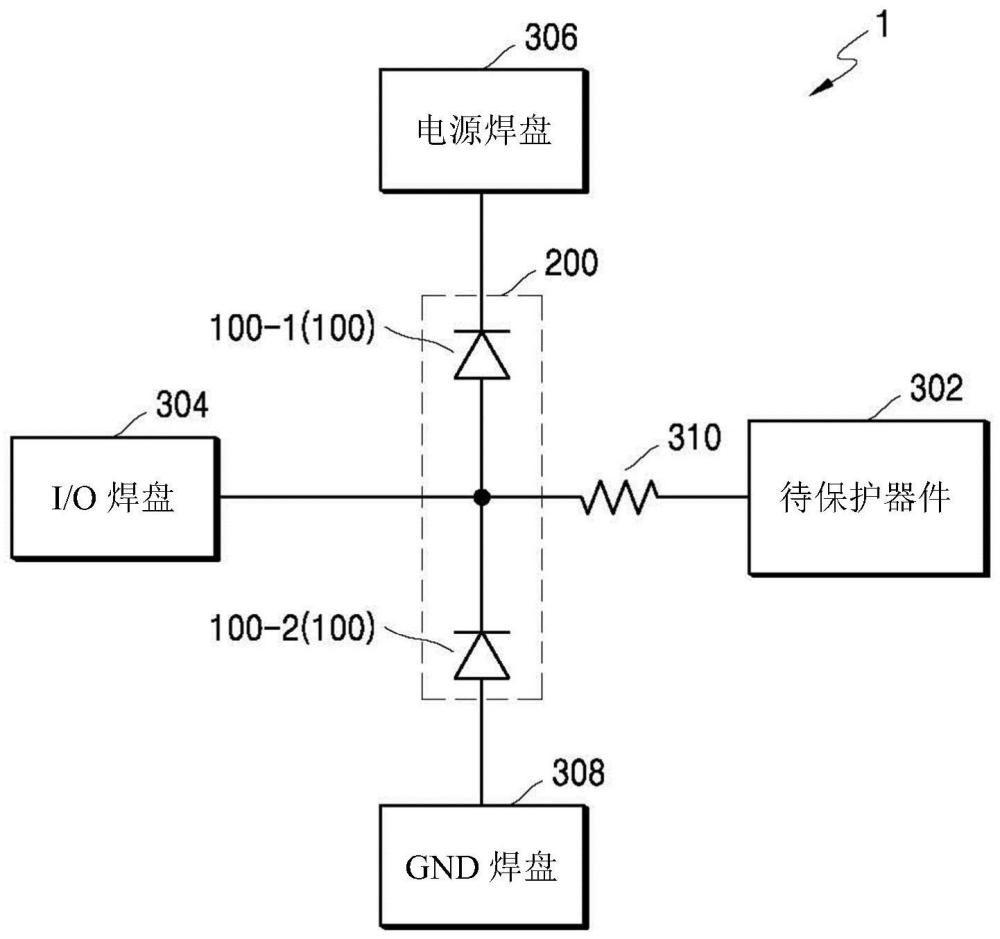

发明构思涉及静电放电(electrostatic discharge,esd)器件,更具体地,涉及具有二极管结构的esd器件和/或包括该esd器件的显示驱动芯片。

背景技术:

1、由于各种原因,半导体器件可能瞬间暴露于几千伏或更高的esd。当半导体器件暴露于esd时,由于半导体器件中晶体管的栅极绝缘层的破坏或金属-硅结处的结穿刺(junction spiking),半导体器件可能被破坏或被损坏。因此,esd可能会严重影响半导体器件的可靠性。为了限制和/或防止由esd引起的损坏,通常在电子器件中使用esd器件或esd保护电路。近来,随着电子器件变得的高度集成化,芯片尺寸不断减小。因此,为了减小esd器件或esd保护电路的尺寸,同时维持esd耐受性,不断进行研究。

技术实现思路

1、发明构思提供了一种具有小尺寸和/或提高的可靠性的静电放电(esd)器件、和/或包括该器件的显示驱动芯片。

2、根据发明构思的实施例,一种静电放电(esd)器件可以包括半导体衬底、第一硅化物层和第二硅化物层。所述半导体衬底可以包括基础阱、在所述基础阱中的第一区、以及在所述基础阱中的第二区。所述第一区可以包括具有第一导电类型的第一区基础阱和在第一区基础阱上的具有第一导电类型的第一杂质区。所述第二区可以在所述基础阱中与所述第一区在水平方向上间隔开。所述第二区可以包括具有第二导电类型的第二区基础阱、在所述第二区基础阱中的具有所述第二导电类型的第二区中间阱、以及在所述第二区中间阱上的具有所述第二导电类型的第二杂质区。所述第二导电类型可以与所述第一导电类型相反。所述第一硅化物层可以在所述第一杂质区上。所述第一硅化物层可以与所述第一杂质区在垂直方向上至少部分地交叠。所述第二硅化物层可以在所述第二杂质区上并且可以与所述第一硅化物层在所述水平方向上间隔开。所述第二硅化物层可以与所述第二杂质区在所述垂直方向上至少部分地交叠。所述基础阱的第一部分可以位于所述第一区与所述第二区之间。所述基础阱的第一部分的至少一部分可以位于所述半导体衬底的分隔区中,所述分隔区在所述第一硅化物层与所述第二硅化物层之间。

3、根据发明构思的实施例,一种静电放电(esd)器件可以包括半导体衬底、第一硅化物层、第二硅化物层和虚设栅极结构。所述半导体衬底可以包括基础阱、在所述基础阱中的第一区、以及在所述基础阱中的第二区。所述基础阱可以具有第一导电类型。所述第一区可以包括具有所述第一导电类型的第一区基础阱和在所述第一区基础阱上的第一杂质区。所述第一杂质区可以具有所述第一导电类型。所述第二区可以与所述第一区在水平方向上间隔开。所述第二区可以包括具有第二导电类型的第二区基础阱、在所述第二区基础阱中的具有所述第二导电类型的第二区中间阱、以及在所述第二区中间阱上的具有所述第二导电类型的第二杂质区。所述第二导电类型可以与所述第一导电类型相反。所述第一硅化物层可以在所述第一杂质区上。所述第一硅化物层可以与所述第一杂质区在垂直方向上至少部分地交叠。所述第二硅化物层可以在所述第二杂质区上。所述第二硅化物层可以与所述第一硅化物层在所述水平方向上间隔开。所述第二硅化物层可以与所述第二杂质区在所述垂直方向上至少部分地交叠。所述虚设栅极结构可以在所述半导体衬底的上表面上。所述虚设栅极结构可以在所述半导体衬底的分隔区上。所述分隔区可以在所述第一硅化物层与所述第二硅化物层之间。所述第一硅化物层可以连接到第一电极。所述第二硅化物层可以连接到第二电极。

4、根据发明构思的实施例,一种显示驱动芯片可以包括电路区、输入区和输出区。所述输出区可以包括多个单元。所述多个单元可以包括静电放电(esd)器件。所述esd器件可以包括p型半导体衬底、在所述p型半导体衬底中的具有n型的基础阱、在所述基础阱中的第一区、在所述基础阱中的第二区、第一硅化物层、以及第二硅化物层。所述第一区可以包括具有第一导电类型的第一区基础阱和在所述第一区基础阱上的具有所述第一导电类型的第一杂质区。所述第二区与所述第一区可以在所述基础阱中在水平方向上间隔开。所述第二区可以包括具有第二导电类型的第二区基础阱、在所述第二区基础阱中的具有所述第二导电类型的第二区中间阱、以及在所述第二区中间阱上的具有所述第二导电类型的第二杂质区。所述第二导电类型可以与所述第一导电类型相反。所述第一硅化物层可以在所述第一杂质区上。所述第一硅化物层可以与所述第一杂质区在垂直方向上至少部分地交叠。所述第二硅化物层可以在所述第二杂质区上并且可以与所述第一硅化物层在所述水平方向上间隔开。所述第二硅化物层可以与所述第二杂质区在所述垂直方向上至少部分地交叠。所述基础阱的一部分可以在所述第一区与所述第二区之间。所述基础阱的所述一部分可以在所述第一硅化物层与所述第二硅化物层之间暴露于p型半导体衬底的上表面。所述第一硅化物层可以连接到第一电极。所述第二硅化物层可以连接到第二电极。

技术特征:

1.一种esd器件,esd即静电放电,包括:

2.根据权利要求1所述的esd器件,其中,

3.根据权利要求1所述的esd器件,其中,

4.根据权利要求1所述的esd器件,其中,

5.根据权利要求1所述的esd器件,其中,

6.根据权利要求1所述的esd器件,还包括:

7.根据权利要求1所述的esd器件,还包括:

8.根据权利要求1所述的esd器件,其中,

9.根据权利要求1所述的esd器件,其中,

10.根据权利要求1所述的esd器件,其中,所述半导体衬底的导电类型不同于所述基础阱的导电类型。

11.一种esd器件,esd即静电放电,包括:

12.根据权利要求11所述的esd器件,其中,

13.根据权利要求11所述的esd器件,其中,

14.根据权利要求11所述的esd器件,其中,所述虚设栅极结构包括:

15.根据权利要求11所述的esd器件,其中,

16.根据权利要求11所述的esd器件,其中,

17.一种显示驱动芯片,包括:

18.根据权利要求17所述的显示驱动芯片,其中,

19.根据权利要求17所述的显示驱动芯片,其中,

20.根据权利要求17所述的显示驱动芯片,其中,

技术总结

一种静电放电器件及包括该静电放电器件的显示驱动芯片。所述静电放电(ESD)器件可以包括:半导体衬底;半导体衬底中的基础阱;在基础阱内的、包括具有第一导电类型的第一杂质区的第一区;在基础阱中的、与第一区在水平方向上间隔开并且包括具有第二导电类型的第二杂质区的第二区;在第一杂质区上与第一杂质区在垂直方向上至少部分地交叠的第一硅化物层;以及在第二杂质区上与第一硅化物层在水平方向上间隔开的第二硅化物层。第二硅化物层可以与第二杂质区在垂直方向上至少部分地交叠。第二导电类型可以与第一导电类型相反。

技术研发人员:高在赫,康彰植,金晙赫

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!