半导体装置的制造方法及等离子体处理装置与流程

本发明的实施方式涉及一种半导体装置的制造方法及等离子体处理装置。

背景技术:

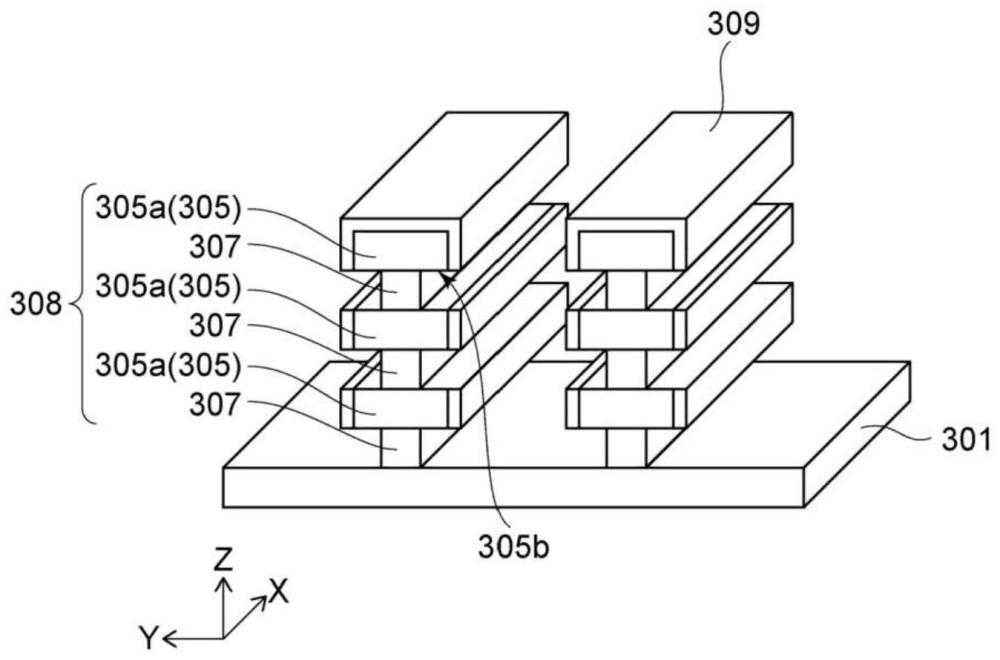

1、在半导体装置的制造过程中,有时会将组成元素不同的层层叠,并对包含其中一种元素的层进行各向同性蚀刻。

2、例如,若将金属-氧化物-半导体场效应晶体管(metal-oxide-semiconductorfield effect transistor,mosfet)微细化,则接通/断开比变小。因此,提出了一种mosfet,所述mosfet具有全环绕栅极(gate all around,gaa)结构,以获得所期望的接通电流。

3、在具有gaa结构的mosfet的制造过程中,在基板上交替地层叠多个包含硅锗(sige)的层以及包含硅(si)的层并对其依次进行蚀刻,从而形成层叠体,所述层叠体交替地层叠有包含硅锗的层以及包含硅的层。然后,通过各向同性蚀刻去除层叠体中所含的包含硅锗的层。层叠体中所含的包含硅的层成为所谓的纳米线通道。

4、此处,在进行各向同性蚀刻时,若不提高相对于硅而言的硅锗的选择比,则层叠体中所含的包含硅的层(纳米线通道)的切削量变多。即,若提高相对于硅而言的硅锗的选择比,则仅能切削去要切削的层(包含硅锗的层)。其结果,可将包含硅的层(纳米线通道)形成为目标尺寸。若无法将包含硅的层(纳米线通道)形成为目标尺寸,则具有gaa结构的mosfet的功能或可靠性可能会降低。

5、因此,期望开发一种在将组成元素不同的层层叠,并对包含其中一种元素的层进行各向同性蚀刻的情况下可提高相对于另一种元素而言的其中一种元素的选择比的技术。

6、[现有技术文献]

7、[专利文献]

8、[专利文献1]日本专利特开2011-29503号公报

技术实现思路

1、[发明所要解决的问题]

2、本发明所要解决的课题在于提供一种在将组成元素不同的层层叠、并对包含其中一种元素的层进行各向同性蚀刻的情况下可提高相对于另一种元素而言的其中一种元素的选择比的半导体装置的制造方法及等离子体处理装置。

3、[解决问题的技术手段]

4、实施方式的半导体装置的制造方法包括如下工序:在层叠体的包含侧面的表面形成保护膜,所述层叠体层叠有第一层以及组成元素与所述第一层不同的第二层;以及对形成有所述保护膜的所述层叠体进行各向同性蚀刻。形成所述保护膜的工序是使用利用等离子体激励第一气体并使其活化而生成的第一自由基来进行。对所述层叠体进行各向同性蚀刻的工序是使用利用等离子体激励与所述第一气体不同的第二气体并使其活化而生成的第二自由基来进行。形成所述保护膜的工序与对所述层叠体进行各向同性蚀刻的工序是在相同的气氛内进行。

5、[发明的效果]

6、根据本发明的实施方式,提供一种在将组成元素不同的层层叠,并对包含其中一种元素的层进行各向同性蚀刻的情况下可提高相对于另一种元素而言的其中一种元素的选择比的半导体装置的制造方法及等离子体处理装置。

技术特征:

1.一种半导体装置的制造方法,包括如下工序:

2.根据权利要求1所述的半导体装置的制造方法,其中,在形成所述保护膜的工序中,所述保护膜的形成于所述第一层的表面的部分的蚀刻速率高于所述保护膜的形成于所述第二层的表面的部分的蚀刻速率。

3.根据权利要求1或2所述的半导体装置的制造方法,其中,在对所述层叠体进行各向同性蚀刻的工序中,在判定为去除了形成于所述第二层的表面的所述保护膜的情况下,停止所述各向同性蚀刻,进行形成所述保护膜的工序。

4.根据权利要求3所述的半导体装置的制造方法,其中,根据自所述各向同性蚀刻开始的时间及发光光谱的变化中的至少任一者进行所述保护膜已被去除的判定。

5.根据权利要求3所述的半导体装置的制造方法,其中,形成所述保护膜的工序与对所述层叠体进行各向同性蚀刻的工序交替地进行多次。

6.根据权利要求1或2所述的半导体装置的制造方法,其中,所述第一层包含硅锗,

7.一种等离子体处理装置,包括:

8.根据权利要求7所述的等离子体处理装置,更包括检测部,所述检测部对所述处理物的处理面的附近的发光进行检测,

9.根据权利要求7或8所述的等离子体处理装置,其中,所述控制器交替地进行多次所述保护膜的形成以及所述层叠体的各向同性蚀刻。

技术总结

本发明提供一种在将组成元素不同的层层叠,并对包含其中一种元素的层进行各向同性蚀刻的情况下可提高相对于另一种元素而言的其中一种元素的选择比的半导体装置的制造方法及等离子体处理装置。制造方法包括如下工序:在层叠体的包含侧面的表面形成保护膜,层叠体层叠有第一层以及组成元素与第一层不同的第二层;以及对形成有保护膜的层叠体进行各向同性蚀刻。形成保护膜的工序是使用利用等离子体激励第一气体并使其活化而生成的第一自由基来进行。对层叠体进行各向同性蚀刻的工序是使用利用等离子体激励与第一气体不同的第二气体并使其活化而生成的第二自由基来进行。形成保护膜的工序与对层叠体进行各向同性蚀刻的工序是在相同的气氛内进行。

技术研发人员:上马俊之,渡邉大辅,林俊宏,目黒佑一

受保护的技术使用者:芝浦机械电子装置株式会社

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!