半导体结构及其制备方法与流程

本申请涉及集成电路,特别是涉及一种半导体结构及其制备方法。

背景技术:

1、在绝缘衬底上的硅(silicon-on-insulator,soi)器件结构中,通常需要制备多层走线层,而且多层走线层之间还需要接触结构进行互连。这导致越靠近顶层的走线层的制备难度越大。

技术实现思路

1、基于此,有必要针对相关技术中的多层走线层制备难度较大的问题提供一种半导体结构及其制备方法。

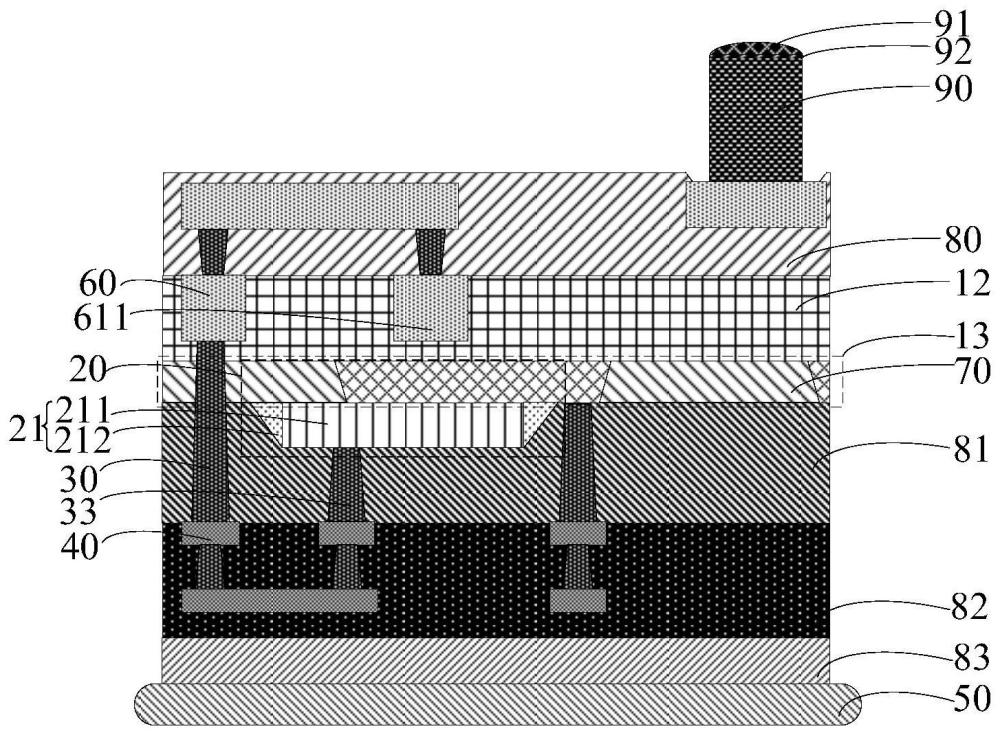

2、为了实现上述目的,一方面,本发明提供了一种半导体结构,包括:

3、支撑基板,

4、第一面走线层,位于所述支撑基板上方,所述第一面走线层具有第一厚度;

5、介质层,位于所述第一面走线层远离所述支撑基板的一侧;

6、半导体器件,位于所述第一面走线层与所述介质层之间,所述半导体器件连接所述第一面走线层;

7、第二面走线层,位于所述介质层远离所述第一面走线层的一侧,所述第二面走线层具有第二厚度,且所述第一厚度与所述第二厚度不同;

8、互连柱,贯穿所述介质层且连接所述第一面走线层和所述第二面走线层。

9、在其中一个实施例中,所述第一厚度的数值小于所述第二厚度的数值;

10、所述半导体结构包括:

11、接入结构,位于所述第二面走线层远离所述支撑基板的一侧,且电连接所述第二面走线层;

12、接出结构,电连接所述第一面走线层。

13、在其中一个实施例中,所述半导体结构包括:

14、第一钝化层,覆盖所述第二面走线层;

15、连接结构,贯穿所述第一钝化层且延伸至所述第二面走线层,所述接入结构位于所述连接结构顶部。

16、在其中一个实施例中,所述第二面走线层包括背栅;

17、所述半导体器件包括晶体管器件,所述第一面走线层连接所述晶体管器件的栅极,所述背栅与所述晶体管器件的沟道区相对设置。

18、在其中一个实施例中,所述半导体结构还包括:

19、接触插塞,连接所述半导体器件的栅极与所述第一面走线层;

20、第二钝化层,覆盖所述半导体器件、所述接触插塞以及所述第一面走线层;

21、塑封层,位于所述支撑基板与所述第二钝化层之间。

22、本发明还提供了一种半导体结构的制备方法,包括如下步骤:

23、提供基底,所述基底包括衬底以及位于所述衬底上的介质层;

24、于所述介质层上形成半导体层;

25、基于所述半导体层,形成半导体器件;

26、于所述半导体器件上方形成互连柱与第一面走线层,

27、所述互连柱电连接所述第一面走线层,所述互连柱贯穿所述介质层并延伸至所述衬底,所述第一面走线层连接所述半导体器件,且所述第一面走线层具有第一厚度;

28、于所述互连柱与所述第一面走线层上方键合支撑基板,并去除所述衬底;

29、将所述支撑基板翻转至底部,并于所述基底去除所述衬底的一侧形成第二面走线层,所述第二面走线层电连接所述互连柱,所述第二面走线层具有第二厚度,且所述第一厚度与所述第二厚度不同。

30、在其中一个实施例中,所述第一厚度的数值小于所述第二厚度的数值;

31、于所述第一钝化材料层内形成延伸至第二面走线层的连接孔,剩余所述第一钝化材料层形成第一钝化层;

32、于所述连接孔内填充导电材料,形成连接结构;

33、于所述连接结构顶部形成接入结构。

34、在其中一个实施例中,所述半导体器件包括晶体管器件,所述第一面走线层连接所述晶体管器件的栅极;

35、所述将所述支撑基板翻转至底部,并于所述基底去除所述衬底的一侧形成第二面走线层,包括:

36、于去除所述衬底后暴露出的所述介质层上方形成图形化光刻胶层;

37、基于图形化光刻胶层刻蚀所述介质层,于所述介质层内形成凹槽,所述凹槽与所述晶体管器件的沟道区相对应;

38、填充凹槽形成背栅。

39、在其中一个实施例中,所述于所述半导体器件上方形成互连柱与第一面走线层,包括:

40、形成覆盖所述半导体器件的第二钝化材料层;

41、刻蚀所述第二钝化材料层,形成互连孔与接触孔,剩余的第二钝化材料层构成第二钝化层,所述互连孔自所述第二钝化层上表面延伸至所述衬底,所述接触孔自所述第二钝化层上表面延伸至所述半导体器件;

42、填充所述互连孔与所述接触孔,分别形成互连柱与接触插塞;

43、于所述互连柱和所述接触插塞上方形成所述第一面走线层。

44、在一个实施例中,所述于所述互连柱与所述第一面走线层上方键合支撑基板,并去除所述衬底,包括:

45、于所述第二钝化层上形成塑封层;

46、键合所述塑封层与所述支撑基板,并去除所述衬底。

47、本发明的半导体结构及其制备方法中,通过将第一面走线层和第二面走线层分别设置于介质层的两侧,使用互连柱连接第一面走线层和第二面走线层,同时,第一面走线层具有第一厚度,第二面走线层具有第二厚度,且第一厚度与第二厚度不同,不仅达到简化制备走线层的目的,而且,厚度不同的走线层分别位于半导体器件的两侧,降低了晶圆翘曲的可能性。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述第一厚度的数值小于所述第二厚度的数值;

3.根据权利要求2所述的半导体结构,其特征在于,所述半导体结构包括:

4.根据权利要求1所述的半导体结构,其特征在于,所述第二面走线层包括背栅;

5.根据权利要求4所述的半导体结构,其特征在于,所述半导体结构包括:

6.一种半导体结构的制备方法,其特征在于,包括如下步骤:

7.根据权利要求6所述的半导体结构的制备方法,其特征在于,所述第一厚度的数值小于所述第二厚度的数值;

8.根据权利要求6所述的半导体结构的制备方法,其特征在于,所述半导体器件包括晶体管器件,所述第一面走线层连接所述晶体管器件的栅极;

9.根据权利要求8所述的半导体结构的制备方法,其特征在于,所述于所述介质层上形成互连柱与第一面走线层,包括:

10.根据权利要求9所述的半导体结构的制备方法,其特征在于,所述于所述互连柱与所述第一面走线层上方键合支撑基板,并去除所述衬底,包括:

技术总结

本发明涉及一种半导体结构及其制备方法,半导体结构包括:支撑基板,第一面走线层,位于支撑基板上方,第一面走线层具有第一厚度;介质层,位于第一面走线层远离支撑基板的一侧;半导体器件,位于第一面走线层与介质层之间,半导体器件连接第一面走线层;第二面走线层,位于介质层远离第一面走线层的一侧,第二面走线层具有第二厚度,且第一厚度与第二厚度不同;互连柱,贯穿介质层且连接第一面走线层和第二面走线层。本发明的半导体结构及其制备方法中,通过将第一面走线层和第二面走线层分别设置于介质层的两侧,并且使用互连柱连接第一面走线层和第二面走线层,以此达到简化制备走线层的目的。

技术研发人员:张旭,李海艇,周强,侯飞凡

受保护的技术使用者:江苏卓胜微电子股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!