晶片规模芯片结构以及用于设计该结构的方法和系统与流程

本公开涉及晶片规模(wafer-scale)芯片,更具体地涉及晶片规模芯片结构以及用于设计该结构的方法和系统的实施例。

背景技术:

1、半导体晶片通常具有相对较大的直径,例如200mm直径(例如8英寸直径)、300mm直径(例如12英寸直径)、450mm直径(例如18英寸直径)等。通常,具有相同设计和尺寸(例如约2.5cm×2.5cm)的多个芯片形成在半导体晶片上并且由切口线分隔开。在芯片制造之后,半导体晶片沿着切口线被切割(即,分割),从而分离芯片。对于需要强大计算能力的应用,多个芯片可以安装在印刷电路板(pcb)上,或者封装在多芯片模块(mcm)中并相互连接。最近,已经开发了晶片规模芯片来提高处理速度。在晶片规模芯片中,在晶片上形成多个管芯(die)。管芯中的一些可以具有相同的设计,而一些可以具有不同的设计。半导体上的各种管芯相互连接(例如,使用后段制程(beol)布线),从而避免了分割半导体晶片的需要,并提高了处理速度,特别是与芯片到芯片通信相关的处理速度。然而,因为具有相同设计的管芯可能形成在晶片上的不同位置,并且因为这些不同位置的晶片形貌(topography)可能不同,所以管芯可能有不同的表现。

技术实现思路

1、本文公开了晶片规模芯片结构的实施例。所述晶片规模芯片结构可以包括半导体晶片。所述晶片规模芯片结构还可以包括位于所述半导体晶片上的多个管芯。所述管芯可以包括具有不同填充形状图案的至少两个管芯。

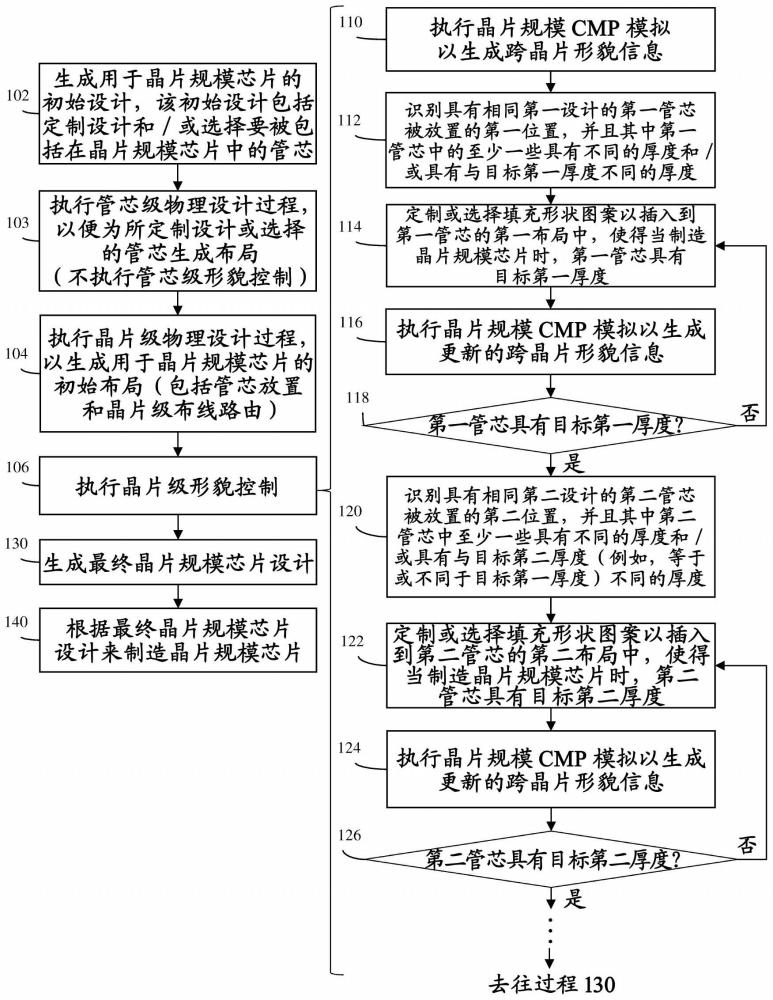

2、本文公开了一种用于晶片规模芯片的设计方法的实施例。该方法可以包括由处理器从存储器访问用于晶片规模芯片的跨晶片管芯放置信息和用于所述晶片规模芯片的跨晶片形貌信息。跨晶片管芯放置信息可以指示管芯在半导体晶片上的位置。跨晶片形貌信息可以指示在给定的所述管芯的放置的情况下所述晶片规模芯片的在所述半导体晶片上相同位置处的不同厚度。该方法还可以包括基于所述跨晶片管芯放置信息和所述跨晶片形貌信息,将不同填充形状图案插入到用于所述管芯的布局中(例如,以使所有跨晶片厚度变化最小化或至少使与具有相同特定设计的特定管芯相关联的跨晶片厚度变化最小化)。该方法还可以包括由所述处理器生成包括所述不同填充形状图案的最终晶片规模芯片设计。这种最终晶片规模芯片设计被输出以用于制造所述晶片规模芯片。

3、本文还公开了用于晶片规模芯片的设计系统的实施例。该系统可以包括存储器,其存储用于晶片规模芯片的跨晶片管芯放置信息和用于所述晶片规模芯片的跨晶片形貌信息。所述跨晶片管芯放置信息可以指示管芯在半导体晶片上的位置。所述跨晶片形貌信息可以指示在给定的所述管芯的放置的情况下所述晶片规模芯片的在所述半导体晶片上相同位置处的不同厚度。该系统还可以包括与所述存储器通信的处理器。所述处理器可以访问所述跨晶片管芯放置信息和所述跨晶片形貌信息,并且可以基于所述跨晶片管芯放置信息和所述跨晶片形貌信息,将不同填充形状图案插入到用于所述管芯的布局中(例如,以使所有跨晶片厚度变化最小化或至少使与具有相同特定设计的特定管芯相关联的跨晶片厚度变化最小化)。所述处理器还可以生成包括所述不同填充形状图案的最终晶片规模芯片设计。这种最终晶片规模芯片设计可以被输出以用于制造所述晶片规模芯片。

技术特征:

1.一种结构,包括:

2.根据权利要求1所述的结构,其中,所述管芯包括具有填充形状图案的第一管芯,其中,具有所述填充形状图案的所述第一管芯具有相同的第一厚度和相同的第一设计,并且其中,所述第一管芯中的所述填充形状图案的至少一些是不同的。

3.根据权利要求2所述的结构,其中,所述管芯包括具有填充形状图案的第二管芯,其中,所述第二管芯具有相同的第二设计和相同的第二厚度,并且其中,所述第二管芯中的所述填充形状图案的至少一些是不同的。

4.根据权利要求3所述的结构,其中,所述第一厚度和所述第二厚度基本相同。

5.根据权利要求3所述的结构,其中,所述第一厚度和所述第二厚度是不同的。

6.根据权利要求1所述的结构,其中,每个填充形状图案包括在电介质层内的金属填充形状和在金属层内的电介质填充形状中的任一者。

7.根据权利要求1所述的结构,其中,任何两种不同填充形状图案的差异包括不同图案尺寸、不同填充形状尺寸、不同填充形状、不同填充形状密度、不同填充形状间距和不同图案层数量中的任一者。

8.根据权利要求1所述的结构,其中,所述不同填充形状图案使任何跨晶片厚度变化和具有相同特定设计的特定管芯之间的跨晶片厚度变化中的一者最小化。

9.根据权利要求1所述的结构,其中,所述填充形状是电隔离的且非功能性的。

10.一种方法,包括:

11.根据权利要求10所述的方法,其中,执行将所述不同填充形状图案插入到用于所述管芯的所述布局中,以使具有相同特定设计的特定管芯之间的厚度变化最小化。

12.根据权利要求10所述的方法,其中,将所述不同填充形状图案插入到用于所述管芯的所述布局中包括:

13.根据权利要求12所述的方法,其中,将所述不同填充形状图案插入到用于所述管芯的所述布局中包括:

14.根据权利要求13所述的方法,其中,所述第一厚度基本等于所述第二厚度。

15.根据权利要求13所述的方法,其中,所述第一厚度和所述第二厚度是不同的。

16.根据权利要求13所述的方法,其中,所述第一管芯中的至少一些具有第一布局,所述第一布局具有不同的插入填充形状图案,并且所述第二管芯中的至少一些具有第二布局,所述第二布局具有不同的插入填充形状图案。

17.根据权利要求10所述的方法,其中,每个填充形状图案包括在电介质层内的金属填充形状和在金属层内的电介质填充形状中的任一者。

18.根据权利要求10所述的方法,其中,任何两种不同的填充形状图案的差异包括不同图案尺寸、不同填充形状尺寸、不同填充形状、不同填充形状密度、不同填充形状间距和不同图案层数量中的任一者。

19.根据权利要求10所述的方法,其中,执行将所述不同填充形状图案插入到用于所述管芯的所述布局中,以使任何跨晶片厚度变化最小化。

20.一种系统,包括:

技术总结

本公开涉及晶片规模芯片结构及用于设计该结构的方法和系统。公开了包括半导体晶片和半导体晶片上的多个管芯的晶片规模芯片结构。管芯可包括具有不同填充形状图案的至少两个管芯。还公开了晶片规模芯片设计方法和系统。在设计方法和系统中,执行芯片布局后晶片级形貌优化,以例如使晶片规模芯片内相同设计的管芯之间的性能变化最小化。具体地,跨晶片管芯放置和晶片级形貌信息用于定制设计和/或选择要被插入到放置在晶片规模芯片的不同位置处的管芯的布局中的不同填充形状图案(包括要被插入到具有相同设计的管芯的布局中的不同图案),以生成使所有跨晶片厚度变化最小化或至少使与具有相同特定设计的特定管芯关联的跨晶片厚度变化最小化的设计。

技术研发人员:O·S·中川,U·卡塔卡姆赛地,H·S·兰迪斯,S·N·沃伊科夫

受保护的技术使用者:格芯(美国)集成电路科技有限公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!