半导体结构的制作方法

本发明涉及半导体制造,尤其涉及一种采用双重图案化技术的半导体结构。

背景技术:

1、在集成电路的制作过程中,光刻(photolithography)工艺为不可或缺的技术,目前,在32nm及其以下技术节点,光刻技术所需的分辨率指标已经超越现有的光刻机台的极限能力。因此,可以在现有的光刻机台上加大最小图案距离的双重图案化技术(doublepatterning technique,dpt)已成为32nm至22nm线宽技术的解决方案。dpt技术是通过将一套高密度的电路图形分解拆分为两套或多套密集度较低的电路图形,然后分别制作光掩模,并逐次完成相应曝光和蚀刻工艺,最终合并形成最初需求的高密度图形。

2、然而,由于dpt技术必须经历多次曝光步骤,因此重叠控制与对准一直是dpt技术所关注的问题,且重叠控制与对准的问题在高密度的电路图形分解拆分为两套或多套密集度较低的电路图形时又更加突显。当dpt技术发生重叠错误或对准不精确时,都会导致电路图形发生断线或相连,而造成严重的断路或短路问题。

3、因此,业界仍需要一种可以克服上述问题的制作半导体布局的方法以及采用此布局制作的半导体结构。

技术实现思路

1、本发明提供一种半导体结构、其制作方法以及制作半导体布局的方法,以解决现有的双重图案化技术中发生的断线、相连等问题。

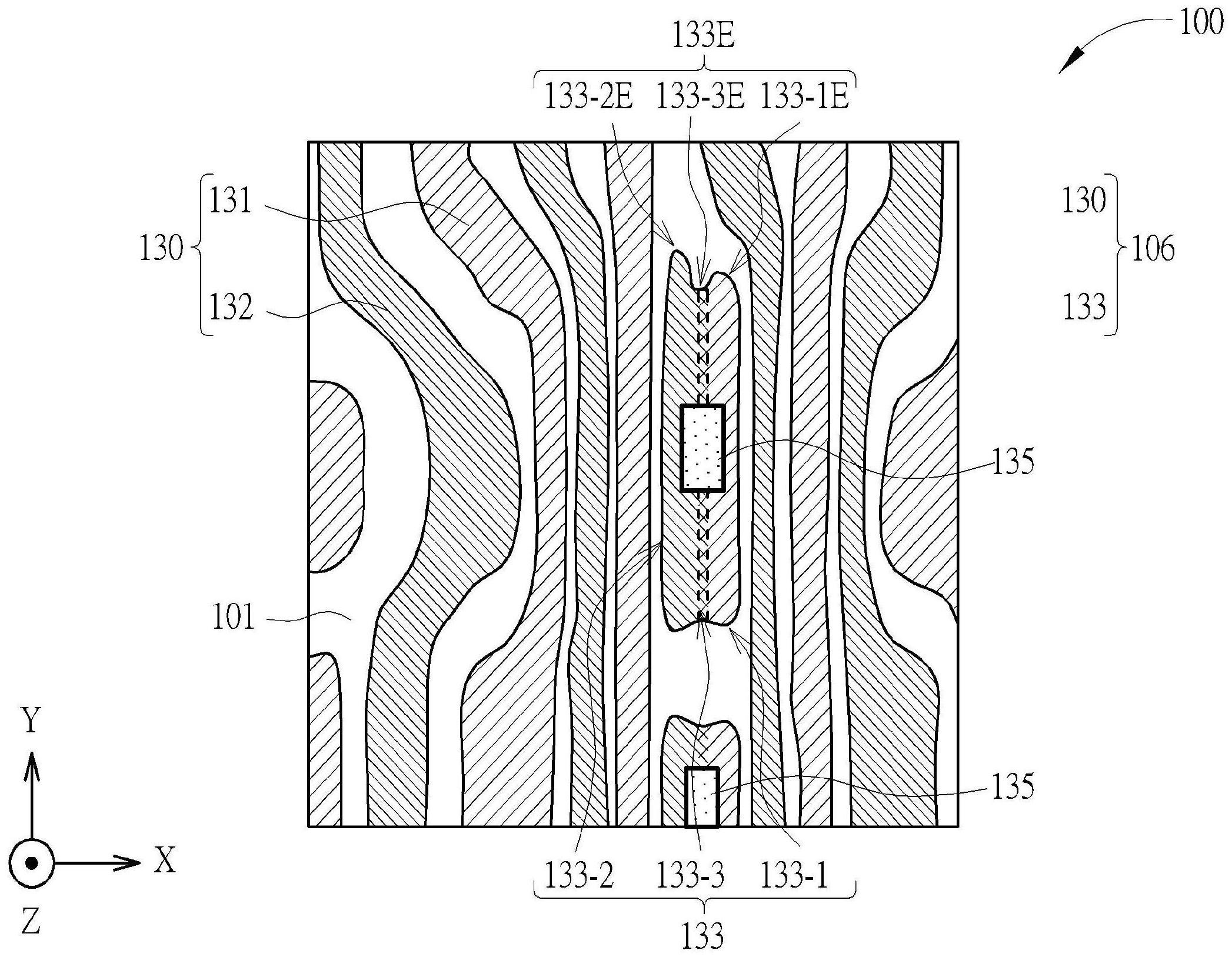

2、根据本发明的一实施例,提供一种半导体结构,包含衬底、多个连线图案以及合并图案,其中,所述衬底包含多个有源区,所述多个连线图案设置在所述衬底上,所述合并图案设置在相邻的所述多个连线图案之间,其中所述合并图案包含沿着第一方向依序排列和互相连接的第一外侧线段、中间线段、和第二外侧线段,且所述第一外侧线段的端面、所述中间线段的端面、和所述第二外侧线段的端面沿着所述第一方向彼此错位。

3、根据本发明的一实施例,提供一种半导体结构的制作方法,包含提供布局,其中所述布局包含多个连线图案和至少一待切割图案;分解所述布局成交替排列的多个第一连线图案和多个第二连线图案,其中所述待切割图案设置于两相邻的所述第一连线图案和所述第二连线图案之间;切割所述待切割图案成切割部分和对应部分;将所述多个第一连线图案和所述切割部分所构成的布局形成于第一光掩模;将所述多个第二连线图案和所述对应部分所构成的布局形成于第二光掩模;提供一衬底,其上设置有目标层;以及将所述第一光掩模的布局和所述第二光掩模的布局转移至所述目标层中,以形成多个连线图案和合并图案,其中所述合并图案的轮廓是由所述切割部分和所述对应部分所定义,所述合并图案包含相对设置的两端面,各所述端面包含凹陷区和突出区。

4、根据本发明的一实施例,提供一种制作半导体布局的方法,包含提供布局,其中所述布局包含多个连线图案和至少一待切割图案;分解所述布局成交替排列的多个第一连线图案和多个第二连线图案,其中所述待切割图案设置于两相邻的所述第一连线图案和所述第二连线图案之间;切割所述待切割图案成原始切割部分和原始对应部分,其中所述原始切割部分和所述原始对应部分之间包含交界线;移动所述原始切割部分的所述交界线,以形成修正的切割部分,其中所述修正的切割部分的面积大于所述原始切割部分的面积;以及将所述多个第一连线图案和所述修正的切割部分形成于光掩模。

5、根据本发明一实施例所提供的制作半导体布局的方法,将宽度较大的待切割图案切割成原始切割部分和原始对应部分,并移动原始切割部分和原始对应部分之间的交界线,产生面积较大的修正的切割部分和修正的对应部份,接着将修正的切割部分和修正的对应部份分别形成于两个光掩模上,并将这两个光掩模的布局转移至目标层中,所形成的半导体结构的合并图案是由切割部分和对应部分所定义,并且可以确保合并图案对应于切割部分和对应部分的两个外侧线段之间不会有断开的情况发生,以提高所形成的半导体结构的可靠度。本发明所提供的半导体结构、其制作方法以及制作半导体布局的方法,可以在不增加工艺复杂度的前提下,有效且可靠地制作密集度高且部份图案尺寸差异较大的电路图形。

技术特征:

1.一种半导体结构,其特征在于包含:

2.依据权利要求第1项所述之半导体结构,其特征在于,所述半导体结构是半导体存储器件的部分结构,其中:

3.依据权利要求第1项所述之半导体结构,其特征在于,所述合并图案具有至少一个空隙,所述空隙位于所述第一外侧线段和所述第二外侧线段之间。

4.依据权利要求第3项所述之半导体结构,其特征在于,还包含接触结构,部分重叠于所述空隙。

5.依据权利要求第1项所述之半导体结构,其特征在于,所述合并图案包含在第二方向上相对设置的两端面,各所述端面包含凹陷区和突出区,其中所述第二方向垂直于所述第一方向。

6.依据权利要求第4项所述之半导体结构,其特征在于,所述凹陷区和所述突出区分别包含弯曲面。

7.依据权利要求第1项所述之半导体结构,其特征在于,所述连线图案包含多个第一连线图案和多个第二连线图案,其中所述多个第一连线图案和所述多个第二连线图案设置在所述衬底上,且沿着所述第一方向交替排列。

8.依据权利要求第7项所述之半导体结构,其特征在于,

9.依据权利要求第7项所述之半导体结构,其特征在于,所述合并图案的宽度大于各所述第一连线图案和各所述第二连线图案的宽度。

10.依据权利要求第9项所述之半导体结构,其特征在于,还包含接触结构,在第三方向上重叠于所述合并图案,其中所述第三方向垂直于衬底的表面。

技术总结

本发明公开了一种半导体结构,包含多个连线图案设置在衬底上,以及合并图案设置在相邻的所述多个连线图案之间,其中合并图案包含沿着第一方向依序排列和互相连接的第一外侧线段、中间线段、和第二外侧线段,且第一外侧线段的端面、中间线段的端面、和第二外侧线段的端面沿着第一方向彼此错位。此外,还公开了半导体结构的制作方法以及制作半导体布局的方法。

技术研发人员:林刚毅,童宇诚,詹益旺,颜逸飞,方晓培

受保护的技术使用者:福建省晋华集成电路有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!