功率半导体器件及功率半导体器件的制作方法与流程

本公开属于半导体,特别涉及一种功率半导体器件及功率半导体器件的制作方法。

背景技术:

1、功率半导体器件,是一种用于进行功率处理的半导体器件,其具有处理高电压、大电流的能力。

2、在相关技术中,ga2o3材料常应用于具有同质衬底的功率半导体器件中,其抗击穿场强为8mv/cm,性能较为优秀。

3、然而,ga2o3材料的电子迁移率较低,仅有数百cm2/vs,导致功率半导体器件在高频和大功率射频领域下的工作能力较差。

技术实现思路

1、本公开实施例提供了一种功率半导体器件及功率半导体器件的制作方法,能够提高电子迁移率,实现导通电阻的降低,提升功率半导体器件在高频和大功率射频领域下的工作能力。所述技术方案如下:

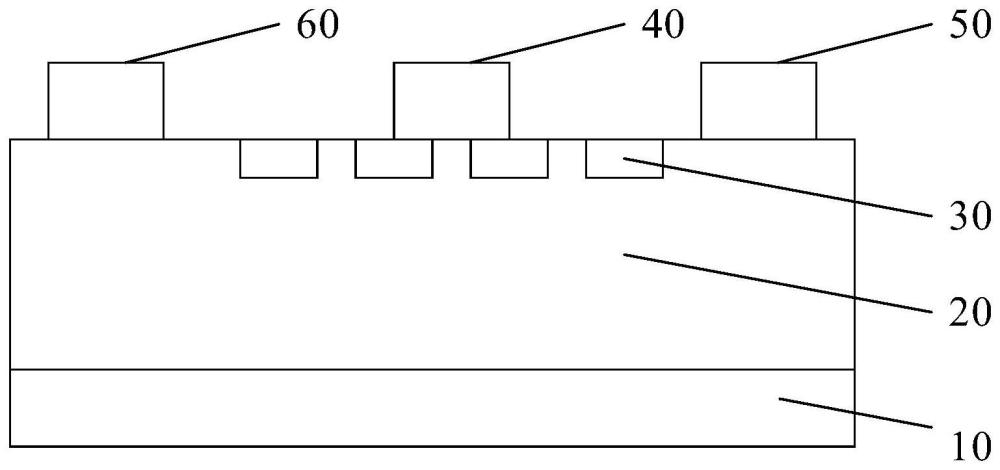

2、第一方面,本公开实施例提供了一种功率半导体器件,包括:衬底、外延层、微结构层、栅电极、漏电极和源电极;

3、所述外延层生长在所述衬底的一面;

4、所述微结构层位于所述外延层背向所述衬底的一面,所述微结构层包括gan层和gaas层中的任一种;

5、所述栅电极位于所述微结构层背向所述衬底的一面,所述漏电极和所述源电极分别位于所述栅电极的两侧。

6、在本公开的一种实现方式中,所述微结构层包括多个所述gan层;

7、多个所述gan层相互间隔排布。

8、在本公开的一种实现方式中,所述gan层的厚度为10~50nm,相邻两个所述gan层的间距为20~100nm。

9、在本公开的一种实现方式中,所述外延层背向所述衬底的一面具有凹槽,所述凹槽在所述外延层的生长方向的截面形状为三角形;

10、所述gaas层生长在所述凹槽内。

11、在本公开的一种实现方式中,所述gaas层的最大厚度为10~40nm。

12、在本公开的一种实现方式中,所述凹槽与所述漏电极的间距为1~3um,所述凹槽与所述源电极的间距为1~3um。

13、在本公开的一种实现方式中,所述衬底为ga2o3衬底;

14、所述外延层包括依次生长的非掺杂ga2o3层和n型掺杂ga2o3沟道层。

15、第二方面,本公开实施例提供了一种功率半导体器件的制作方法,所述制作方法用于制备第一方面所述的功率半导体器件,所述制作方法包括:

16、提供一衬底;

17、在所述衬底的一面生长外延层;

18、在所述外延层背向所述衬底的一面制备gan层或gaas层,以形成微结构层;

19、在所述微结构层对应的位置设置栅电极;

20、在所述栅电极的两侧设置漏电极和源电极。

21、在本公开的一种实现方式中,在所述外延层背向所述衬底的一面制备gan层,包括:

22、对所述外延层背向所述衬底的一面进行定点氮气等离子体轰击,以在所述外延层背向所述衬底的一面形成多个相互间隔排布的所述gan层。

23、在本公开的一种实现方式中,在所述外延层背向所述衬底的一面制备gaas层,包括:

24、在所述外延层背向所述衬底的一面刻蚀形成凹槽,所述凹槽在所述外延层的生长方向的截面形状为三角形;

25、在所述凹槽内溅射生长所述gaas层。

26、本公开实施例提供的技术方案带来的有益效果至少包括:

27、在外延层背向衬底的一面设置有微结构层,微结构层包括gan层或者gaas层,将栅电极设置在微结构层背向所述衬底的一面,所述漏电极和所述源电极分别设置在所述栅电极的两侧,使得功率半导体器件形成水平结构。利用gan材料和gaas材料导通电阻较低的特性,有效的提升了电子迁移率,实现了较高的开光比,功率半导体器件转换效率高,提升功率半导体器件在高频和大功率射频领域下的工作能力。

28、也就是说,通过增设gan层或者gaas层,能够有效的提升了电子迁移率,实现了较高的开光比,功率半导体器件转换效率高,提升功率半导体器件在高频和大功率射频领域下的工作能力。

技术特征:

1.一种功率半导体器件,其特征在于,包括:衬底(10)、外延层(20)、微结构层(30)、栅电极(40)、漏电极(50)和源电极(60);

2.根据权利要求1所述的功率半导体器件,其特征在于,所述微结构层(30)包括多个所述gan层(310);

3.根据权利要求2所述的功率半导体器件,其特征在于,所述gan层(310)的厚度为10~50nm,相邻两个所述gan层(310)的间距为20~100nm。

4.根据权利要求1所述的功率半导体器件,其特征在于,所述外延层(20)背向所述衬底(10)的一面具有凹槽(210),所述凹槽(210)在所述外延层(20)的生长方向的截面形状为三角形;

5.根据权利要求4所述的功率半导体器件,其特征在于,所述gaas层(320)的最大厚度为10~40nm。

6.根据权利要求4所述的功率半导体器件,其特征在于,所述凹槽(210)与所述漏电极(50)的间距为1~3um,所述凹槽(210)与所述源电极(60)的间距为1~3um。

7.根据权利要求1~6任一项所述的功率半导体器件,其特征在于,所述衬底(10)为ga2o3衬底;

8.一种功率半导体器件的制作方法,其特征在于,所述制作方法用于制备权利要求1~7任一项所述的功率半导体器件,所述制作方法包括:

9.根据权利要求8所述的制作方法,其特征在于,在所述外延层(20)背向所述衬底(10)的一面制备gan层(310),包括:

10.根据权利要求8所述的制作方法,其特征在于,在所述外延层(20)背向所述衬底(10)的一面制备gaas层(320),包括:

技术总结

本公开提供了一种功率半导体器件及功率半导体器件的制作方法,属于半导体技术领域。该功率半导体器件,包括:衬底、外延层、微结构层、栅电极、漏电极和源电极;外延层生长在衬底的一面;微结构层位于外延层背向衬底的一面,微结构层包括GaN层和GaAs层中的任一种;栅电极位于微结构层背向衬底的一面,漏电极和源电极分别位于栅电极的两侧。本公开能够提高电子迁移率,实现导通电阻的降低,提升功率半导体器件在高频和大功率射频领域下的工作能力。

技术研发人员:王群,龚逸品,陈张笑雄,吴志浩,梅劲,王江波,刘榕

受保护的技术使用者:华灿光电(浙江)有限公司

技术研发日:

技术公布日:2024/2/6

- 还没有人留言评论。精彩留言会获得点赞!