一种碳化硅MOSFET器件及其制备方法与流程

本申请涉及电力电子领域,特别是一种碳化硅mosfet器件及其制备方法。

背景技术:

1、电能是一种经济清洁、方便运输、易于转换的能源。功率半导体器件作为电力电子技术的基石,同时也是实现电能转换、传输的核心控制元件,因此功率半导体器件性能的优劣决定着电能效率的高低。国内的功率半导体器件的发展开始于20世纪60年代,从较为简单的硅基功率二极管起步,现在已经具备了硅基功率晶闸管、双极结型晶体管、功率mosfet和绝缘栅双极晶体管等器件的研发和制造能力。随着器件结构设计的不断创新和迭代更新,以及制造工艺精细化发展,目前,硅基功率半导体器件虽然仍是主流应用器件,但是其性能已经逐渐接近硅基材料的极限。

2、功率半导体器件的发展目标仍是提高开关速度、降低能量损耗、提升功率密度等以适用于高功率和高频化的应用需求。以碳化硅(sic)为代表的第三代宽禁带半导体材料拥有比硅基材料更大的禁带宽度、更高的临界击穿电场强度、更高的电子饱和漂移速度和更高的热导率,能使其在高温、高频、大功率等领域应用。

3、碳化硅金属氧化物半导体场效应晶体管(碳化硅mosfet)结合了碳化硅材料的优势和金属氧化物半导体场效应晶体管(mosfet)开关速度快、驱动简单等优点,得到了广泛的研究和应用。沟槽栅碳化硅mosfet因垂直晶面缺陷密度低使得沟道迁移率高,以及消除了寄生的结型场效应晶体管结构的优势,有着更大的导通电流密度。然而其沟槽栅底部容易出现电场集中效应影响栅介质可靠性,导致器件提前失效。

4、此外,碳化硅mosfet器件中寄生体二极管(pin二极管)的导通电压较高,且在pin二极管的关断过程中存在少数载流子的存储,导致较长的反向恢复时间和较大的损耗。因此,当前的碳化硅mosfet器件在应用中通常反并联一个肖特基二极管,或者在碳化硅mosfet器件中集成肖特基二极管。然而集成肖特基二极管的碳化硅mosfet在器件处于反向耐压时,有较大的反向漏电流。以上的一些问题使得碳化硅mosfet器件在实际应用中受到了一定的限制。

技术实现思路

1、鉴于所述问题,提出了本申请以便提供克服所述问题或者至少部分地解决所述问题的一种碳化硅mosfet器件及其制备方法,包括:

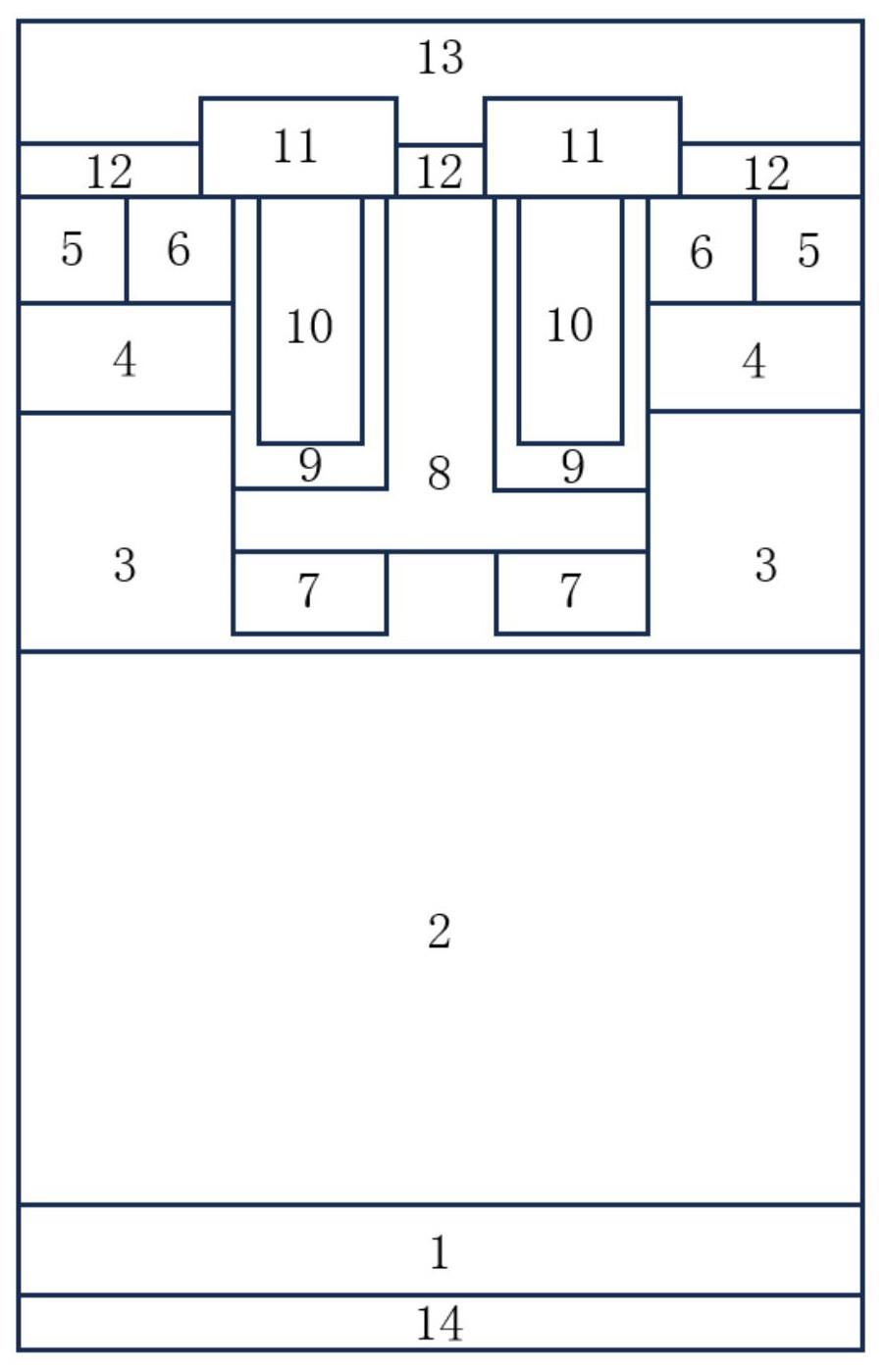

2、一种碳化硅mosfet器件,包括依次层叠设置的漏极金属层、碳化硅n型衬底层、碳化硅n型外延层和碳化硅n型电流扩展层;

3、所述碳化硅n型电流扩展层内部设有碳化硅p型屏蔽层,所述p型屏蔽层顶部设有p型多晶硅,且所述p型多晶硅的两端和底部与所述碳化硅n型电流扩展层接触;所述p型多晶硅内部设有栅极结构,所述栅极结构顶部设有层间电介质层。

4、进一步地,所述碳化硅n型电流扩展层顶部设有碳化硅p型阱区,所述碳化硅p型阱区顶部设有碳化硅n型源区和碳化硅p型接触区,所述碳化硅n型源区和所述碳化硅p型接触区上方设有源极接触金属。

5、进一步地,所述p型多晶硅贯穿所述栅极结构,所述栅极结构的中部与底部均被所述p型多晶硅覆盖。

6、进一步地,所述栅极结构包括栅介质和设置在所述栅介质内部的多晶硅栅,所述多晶硅栅顶部与所述层间电介质层接触,所述多晶硅栅其他面均被所述栅介质包裹。

7、进一步地,所述p型多晶硅的两个底角分别至少设有一个所述碳化硅p型屏蔽层,所述碳化硅p型屏蔽层之间互不接触。

8、进一步地,位于所述p型多晶硅同一底角的若干所述碳化硅p型屏蔽层之间间距的宽度为0.3μm-0.8μm。

9、进一步地,所述p型多晶硅的厚度为1μm-2μm,且所述p型多晶硅厚度大于所述栅极结构厚度。

10、进一步地,所述碳化硅n型电流扩展层的厚度为0.5μm-1.5μm。

11、一种碳化硅mosfet器件的制备方法,所述方法用于制备上述任一项所述的碳化硅mosfet,包括:

12、依据预设条件与工艺在碳化硅n型衬底层上生成碳化硅n型外延层,在所述碳化硅n型外延层上生成碳化硅n型电流扩展层,在所述碳化硅n型电流扩展层上生成碳化硅p型阱区;

13、依据预设结构排布注入掩模版,并通过所述注入掩模版依次注入碳化硅p型接触区、碳化硅n型源区和碳化硅p型屏蔽层;其中,在注入所述碳化硅p型屏蔽层之前,依据预设结构蚀刻碳化硅沟槽;

14、在所述碳化硅沟槽内淀积p型多晶硅,依据预设结构刻蚀形成多晶硅沟槽;并在所述多晶硅沟槽内设置栅介质和多晶硅栅;

15、通过淀积、刻蚀工艺生成层间电介质层,剥离金属并进行快速热退火形成源极接触金属;

16、在器件顶部蒸发金属并刻蚀形成金属pad,在器件底部溅射金属并退火形成漏极金属层,完成制备。

17、本申请具有以下优点:

18、在本申请的实施例中,相对于现有技术中的碳化硅mosfet器件中寄生pin二极管可靠性较低,集成肖特基二极管又有较大反向漏电流,本申请提供了集成异质结二极管的解决方案,具体为:依次层叠设置的漏极金属层、碳化硅n型衬底层、碳化硅n型外延层和碳化硅n型电流扩展层;所述碳化硅n型电流扩展层内部设有碳化硅p型屏蔽层,所述碳化硅p型屏蔽层顶部设有p型多晶硅,且所述p型多晶硅的两端和底部与所述碳化硅n型电流扩展层接触;所述p型多晶硅内部设有栅极结构,所述栅极结构顶部设有层间电介质层。通过所述p型多晶硅的两端和底部与所述碳化硅n型电流扩展层接触,形成了具有整流特性的异质结接触,同时形成多条电流路径,避免器件在反向续流下的电流集中,提高了器件的可靠性。

技术特征:

1.一种碳化硅mosfet器件,其特征在于,包括依次层叠设置的漏极金属层、碳化硅n型衬底层、碳化硅n型外延层和碳化硅n型电流扩展层;

2.根据权利要求1所述的碳化硅mosfet器件,其特征在于,所述碳化硅n型电流扩展层顶部设有碳化硅p型阱区,所述碳化硅p型阱区顶部设有碳化硅n型源区和碳化硅p型接触区,所述碳化硅n型源区和所述碳化硅p型接触区上方设有源极接触金属。

3.根据权利要求1所述的碳化硅mosfet器件,其特征在于,所述p型多晶硅贯穿所述栅极结构,所述栅极结构的中部与底部均被所述p型多晶硅覆盖。

4.根据权利要求1所述的碳化硅mosfet器件,其特征在于,所述栅极结构包括栅介质和设置在所述栅介质内部的多晶硅栅,所述多晶硅栅顶部与所述层间电介质层接触,所述多晶硅栅其他面均被所述栅介质包裹。

5.根据权利要求1所述的碳化硅mosfet器件,其特征在于,所述p型多晶硅的两个底角分别至少设有一个所述碳化硅p型屏蔽层,所述碳化硅p型屏蔽层之间互不接触。

6.根据权利要求5所述的碳化硅mosfet器件,其特征在于,位于所述p型多晶硅同一底角的若干所述碳化硅p型屏蔽层之间间距的宽度为0.3μm-0.8μm。

7.根据权利要求1所述的碳化硅mosfet器件,其特征在于,所述p型多晶硅的厚度为1μm-2μm,且所述p型多晶硅厚度大于所述栅极结构厚度。

8.根据权利要求1所述的碳化硅mosfet器件,其特征在于,所述碳化硅n型电流扩展层的厚度为0.5μm-1.5μm。

9.一种碳化硅mosfet器件的制备方法,其特征在于,所述方法用于制备权利要求1-8中任一项所述的碳化硅mosfet器件,包括:

技术总结

本申请提供了一种碳化硅MOSFET器件及其制备方法,包括:依次层叠设置的漏极金属层、碳化硅N型衬底层、碳化硅N型外延层和碳化硅N型电流扩展层;所述碳化硅N型电流扩展层内部设有碳化硅P型屏蔽层,所述碳化硅P型屏蔽层顶部设有P型多晶硅,且所述P型多晶硅的两端和底部与所述碳化硅N型电流扩展层接触;所述P型多晶硅内部设有栅极结构,所述栅极结构顶部设有层间电介质层。通过所述P型多晶硅的两端和底部与所述碳化硅N型电流扩展层接触,形成了具有整流特性的异质结接触,同时形成多条电流路径,避免器件在反向续流下的电流集中,提高了器件的可靠性。

技术研发人员:汪之涵,和巍巍,温正欣

受保护的技术使用者:深圳基本半导体有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!