用于深沟槽内的低温选择性外延的方法及设备与流程

本公开内容的实施方式一般地涉及半导体制造工艺领域,尤其是,涉及用于形成半导体器件的沉积含硅膜的群集工具和方法。

背景技术:

1、低温外延具有具非常高程度掺杂剂活化的产生外延膜的明显优点。具有高度掺杂剂活化的外延膜可以对于cmos制造工艺中的接触应用是有用的,其中热预算需要在特定温度或低于特定温度,以在中段(middle-of-line(mol))制造工艺中保持高k金属栅极堆叠,特定温度诸如450摄氏度。

2、需要在本领域中整合用于生长含磷硅层的低温外延,以能够减少nmos晶体管的接触电阻的量级。

技术实现思路

1、本公开内容一般地涉及用于在半导体器件上形成外延层的群集工具和方法。在一个实施方式中,群集工具包括传送腔室、耦接到传送腔室的预清洁腔室、耦接到传送腔室的等离子体清洁腔室、耦接到传送腔室的沉积腔室、耦接到传送腔室的蚀刻腔室及耦接到传送腔室的热处理腔室。

2、在另一实施方式中,群集工具包括耦接到负载锁定腔室的传送腔室、耦接到传送腔室的第一清洁腔室、耦接到该传送腔室的第二清洁腔室、耦接到该传送腔室的外延沉积腔室、耦接到传送腔室的蚀刻腔室及耦接到传送腔室的热处理腔室,所述第一清洁腔室包括电容耦合等离子体源和耦接到偏压rf电源的基板支撑件,该第二清洁腔室包括电感耦合等离子体源,所述外延腔室包括与液体前驱物源流体连通的液体蒸发器。

技术特征:

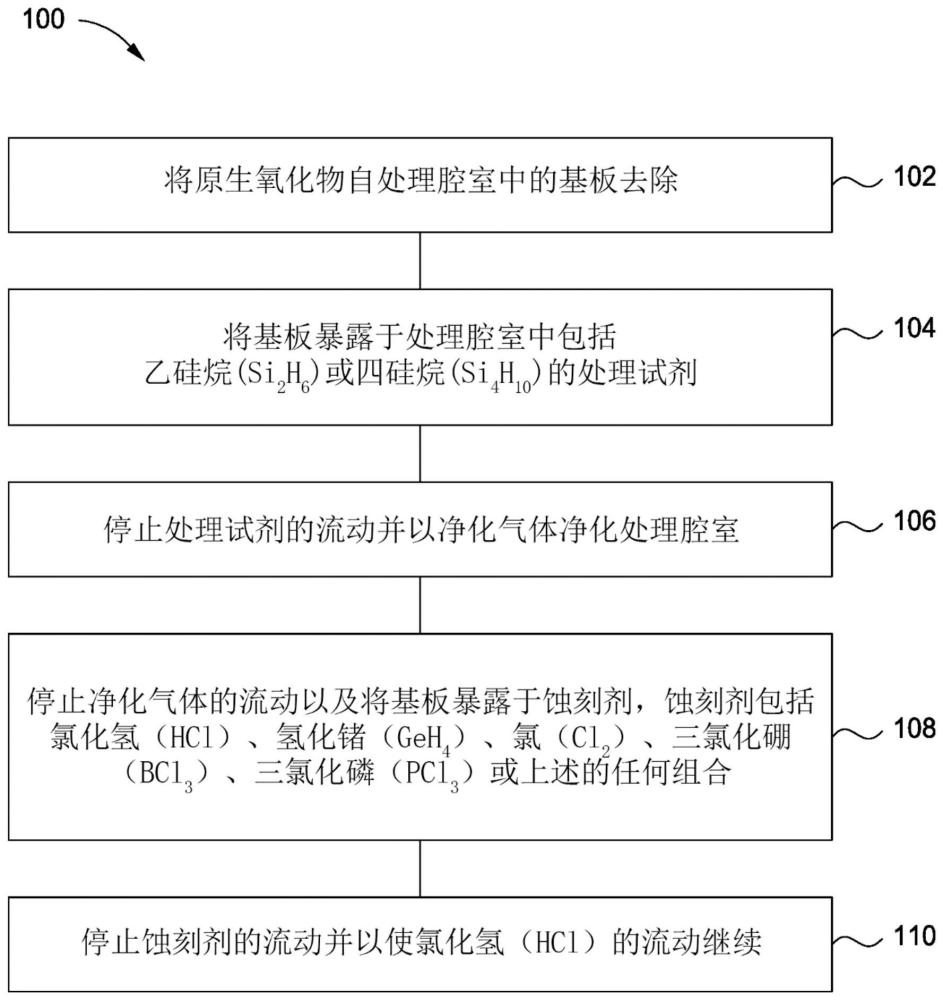

1.一种形成外延层的方法,包括以下步骤:

2.根据权利要求1所述的方法,其中所述硅源包括二硅烷、三硅烷、四硅烷、五硅烷或六硅烷。

3.根据权利要求1所述的方法,其中所述清洁工艺包括溅射蚀刻工艺、基于等离子体的氧化物蚀刻工艺、湿式蚀刻工艺、烘烤工艺或上述工艺的组合。

4.根据权利要求1所述的方法,其中所述清洁工艺包括基于等离子体的氧化物蚀刻工艺,所述基于等离子体的氧化物蚀刻工艺进一步包括同时将所述基板暴露于由电感耦合等离子体工艺、电容耦合等离子体工艺或远程等离子体辅助干式蚀刻工艺形成的nf3和nh3等离子体副产物。

5.根据权利要求1所述的方法,其中所述清洁工艺包括在存在氢气的情况下加热所述基板。

6.根据权利要求1所述的方法,其中所述清洁工艺进一步包括在去除所述氧化物之后在所述基板的所述表面上形成硅-氢键结。

7.根据权利要求1所述的方法,其中所述清洁工艺是在预清洁腔室中执行的,所述预清洁腔室包括电容耦合等离子体源和耦接到偏压rf电源的基板支撑件,并且其中所述电容耦合等离子体源耦接到he和nf3源。

8.根据权利要求1所述的方法,其中所述清洁处理包括将所述基板的所述表面上的所述氧化物暴露于hf清洁,以在单晶硅表面上产生-h端基并在介电氧化物表面上产生-oh端基。

9.根据权利要求1所述的方法,其中所述净化气体包括氢气或氩气。

10.根据权利要求1所述的方法,其中所述蚀刻气体包括含锗化合物,并且其中所述含锗化合物包括氢化锗、二锗烷、三锗烷、四氯化锗、二氯锗烷、三氯锗烷、六氯二锗烷、或上述的任意组合。

11.根据权利要求1所述的方法,其中所述蚀刻气体包含含氯化合物,并且其中所述含氯化合物包含氯气、三氯化硼、三氯化磷、或上述的任意组合。

12.根据权利要求1所述的方法,其中所述蚀刻气体包括氯化氢、氢化锗和三氯化磷。

13.根据权利要求1所述的方法,其中所述蚀刻气体进一步包括载气,所述载气包括氢气、氮气、氩气、氦气、和上述的任意组合。

14.根据权利要求1所述的方法,其中所述蚀刻气体选择性地从所述基板的介电表面去除非晶硅。

15.根据权利要求1所述的方法,其中所述基板的所述表面包括深宽比为10:1或更高的接触沟槽。

16.根据权利要求1所述的方法,其中所述外延工艺是在耦接到处理系统的外延腔室中执行的,并且所述外延腔室包括与液体前驱物源流体连通的液体前驱物蒸发器。

17.一种形成外延层的方法,包括以下步骤:

18.根据权利要求16所述的方法,其中所述硅源包括二硅烷、三硅烷、四硅烷、五硅烷或六硅烷。

19.根据权利要求17所述的方法,其中所述工艺循环重复2个循环至5个循环。

20.根据权利要求19所述的方法,其中所述基板的所述表面包括深宽比为10:1或更高的接触沟槽。

21.根据权利要求17所述的方法,其中所述清洁工艺包括基于等离子体的氧化物蚀刻工艺,所述基于等离子体的氧化物蚀刻工艺进一步包括同时将所述基板暴露于由电感耦合等离子体工艺、电容耦合等离子体工艺或远程等离子体辅助干式蚀刻工艺形成的nf3和nh3等离子体副产物。

22.一种形成外延层的方法,包括以下步骤:

技术总结

本公开内容一般地涉及用于在半导体器件上形成外延层的群集工具和方法。在一个实施方式中,群集工具包括传送腔室、耦接到传送腔室的预清洁腔室、耦接到传送腔室的等离子体清洁腔室、耦接到传送腔室的沉积腔室、耦接到传送腔室的蚀刻腔室及耦接到传送腔室的热处理腔室。

技术研发人员:阿布舍克·杜贝,李学斌,华·春,芙洛拉·芳-松·张

受保护的技术使用者:应用材料公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!