一种基于多层应力记忆技术的CMOS器件制造方法

本发明属于集成电路制造,尤其涉及一种基于多层应力记忆技术的cmos器件制造方法。

背景技术:

1、随着半导体制造技术的进步,应力记忆技术(smt,stress memorizationtechnology)能够有效提高互补型金属氧化物半导体场效应管(complementary metal-oxide semiconductor field effect transistor,cmosfet)的性能。通过向cmos的导电沟道引入局部单向应力,达到提升cmos的导电沟道内载流子迁移率的目的,从而在栅极电介质层厚度变薄或保持不变的情况下使驱动电流大幅增长,最终提高cmos器件性能。

2、同时随着mos器件尺寸的缩小和氧化层的减薄,作用在栅氧化层中的电场强度极大增加,mos器件的可靠性控制变得日益重要。尤其是负偏压温度不稳定性(negative biastemperature instability,nbti)效应越来越明显。nbti主要是由硅/氧化层(si/si0,)界面陷阱电荷和氧化层电荷的变化而引起的。在栅极的硅/氧化层界面中存在着一些si的悬挂键。在工艺中,一旦有h扩散到硅/氧化层的界面中,h会和硅的悬挂键结合形成si-h键。但是在器件工作中会在栅极上形成一个高电场,此时si-h键就容易被打断,si的悬挂键重新出现,吸引电荷,进而成为带正电的界面陷阱。此类界面陷阱随着栅极偏置电压的增加和温度的上升而变多,进一步影响器件性能和可靠性。

3、pmos器件性能有两个影响因素,一个是拉应力会降低空穴迁移率,另一个因素则是h对器件掺杂和界面态的影响,进一步影响性能和可靠性。一般对于成本受限的制造流程,通常采用<100>晶向的晶圆制造cmos器件能够使pmos器件免受拉应力的影响,本文不做赘述,但是仍存在h对器件性能和可靠性造成的影响。

4、应力记忆技术中,采用化学气相沉积薄膜的由于沉积过程中所使用的源气体为sih4和nh3的混合气体,沉积的薄膜中含有大量的h,经退火后大量的h扩散到器件中,不仅仅会和硅/氧界面的si悬挂键结合成si-h键,也会扩散到器件的源/漏中去,导致pmos的源/漏区中掺杂的硼向沟道区中扩散,增加短沟道效应,都导致了集成电路性能的下降。通常来说采用紫外光固化技术处理刻蚀阻挡层就能避免此类问题发生,但是紫外光固化等其他工艺的引入增加了制造和设备成本。为了低成本考虑,采用等离子体氮化处理工艺代替紫外光固化工艺。实验证明,采用等离子体氮化工艺处理刻蚀阻挡层,得到的阻挡层致密度不如紫外光固化工艺,对氢的阻挡效果不好。

技术实现思路

1、有鉴于此,本发明提供一种基于多层应力记忆技术的cmos器件制造方法,从而有效地改善半导体元器件的电学性能。

2、根据上述目的,本发明的技术方案是这样实现的:

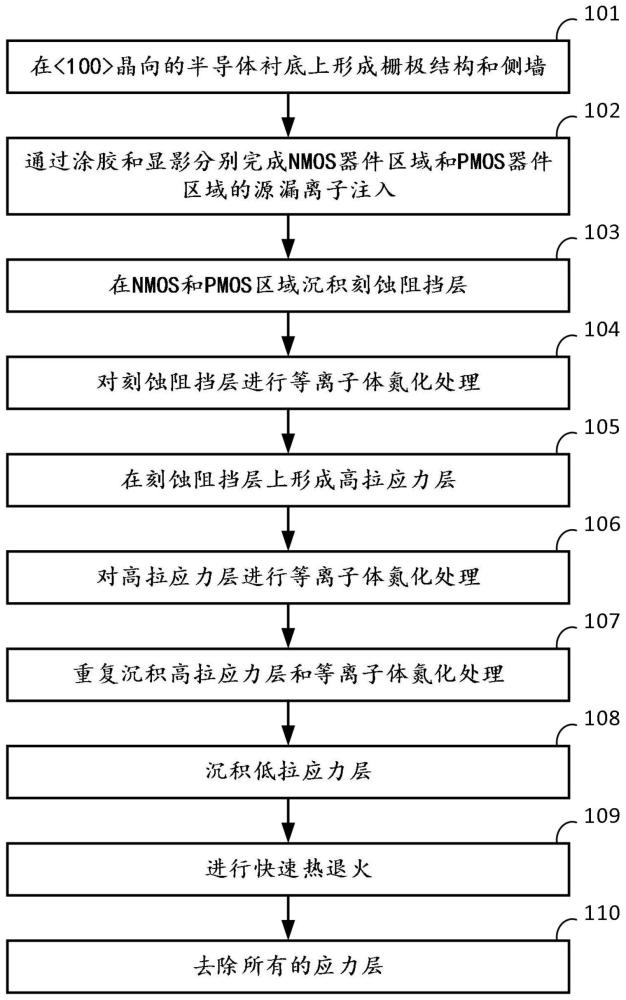

3、一种基于多层应力记忆技术的cmos器件制造方法,包括:

4、在晶圆上沉积刻蚀阻挡层;

5、所述刻蚀阻挡层进行等离子体氮化处理;

6、在处理后的刻蚀阻挡层上进行n次沉积高拉应力层,并对高拉应力层进行等离子体氮化处理;n≥1;

7、在最上层等离子体氮化处理后的高拉应力层沉积低拉应力层;其中所述低拉应力层的拉应力和氢含量均小于所述高拉应力层的拉应力和氢含量;

8、对沉积刻蚀阻挡层、高拉应力层、低拉应力层的晶圆进行快速热退火;

9、对快速热退火后的晶圆刻蚀,去除所述高拉应力层、低拉应力层。

10、作为优选,所述晶圆为<100>晶向。

11、作为优选,在晶圆上沉积刻蚀阻挡层前所述晶圆还进行如下处理:所述晶圆的半导体衬底上形成栅极结构和侧墙;通过涂胶和显影分别完成nmos器件区域和pmos器件区域的源/漏离子注入。

12、作为优选,在注入源/漏离子的nmos器件区域和pmos器件区域沉积刻蚀阻挡层。

13、作为优选,所述刻蚀阻挡层的材质选用氮化硅、氮氧化硅或者氮化硅。

14、作为优选,所述等离子体氮化处理的方法是在200-650℃的反应条件下向所述刻蚀阻挡层层的表面通入含氮气体,所述含氮气体是氮气、一氧化氮和一氧化二氮中的一种或任意组合气体;所述含氮气体的流量范围是50-5000标况每立方厘米,所述含氮气体的高频功率范围是10-2000瓦;所述含氮气体的压力范围是1-100托。

15、作为优选,所述高拉应力层、低拉应力层的沉积工艺为化学气相沉积方法;沉积工艺条件如下:高拉应力层的沉积工艺条件如下:反应物为含硅气体和含氮气体,所述含硅气体的流量范围是1-200sccm,所述含氮气体的流量范围是1-200sccm;所述沉积工艺的压力范围是1-100托;所述沉积工艺的温度范围是200-650℃;所述沉积工艺射频功率为50-200w。低拉应力层的沉积工艺条件如下:反应物为含硅气体和含氮气体,所述含硅气体的流量范围是1-200sccm,所述含氮气体的流量范围是1-200sccm;所述沉积工艺的压力范围是1-100托;所述沉积工艺的温度范围是200-650℃;所述沉积工艺射频功率为1-49w。

16、作为优选,所述高拉应力层的沉积厚度为拉应力范围为800-1400mpa;所述低拉应力层的沉积厚度为拉应力范围为1-700mpa。

17、作为优选,相邻高拉应力层的拉应力不同或相同。

18、作为优选,n=1~5。

19、本发明在沉积低拉应力层之前,在晶圆器件上沉积刻蚀阻挡层和高拉应力层,刻蚀阻挡层和高拉应力层至少同时覆盖在n阱和p阱上方;对刻蚀阻挡层进行表面等离子体氮化处理,随后沉积高拉应力层,进行接着表面等离子体氮化处理,并且多次沉积多次进行表面等离子体氮化处理,循环的次数取决采用此方法制造的pmos器件的可靠性测试,随后沉积低拉应力层,退火晶片,以促进应力施加效果。本发明通过强化阻挡层和多次循环沉积和处理的高拉应力层抵抗氢原子扩散的能力,减小了nmos和pmos器件的nbti效应,避免了由上述过程形成的应力材料层中的氢原子导致的硼扩散现象发生造成的pmos器件性能退化。

20、本发明的有益效果是:

21、本发明通过沉积多层致密的高拉应力层抵抗氢原子扩散的能力,减小了cmos器件的nbti效应,减轻了pmos器件性能的退化。

22、本发明通过对高拉应力层表面进行等离子体氮化处理,增大高拉应力层表面的氮含量,使高拉应力层表面更加致密,形成致密的界面,进一步增大阻挡氢原子扩散的能力,还使得自身高拉应力层内的氢原子含量减少,进而促进pmos器件性能的退化。

23、通过使用本发明所提供的半导体器件和制造方法,可用超低的制造成本改善半导体器件的电学性能,在保证nmos器件性能有进一步优化的同时,防止pmos器件性能的退化。

技术特征:

1.一种基于多层应力记忆技术的cmos器件制造方法,其特征在于,该方法包括:

2.根据权利要求1所述的方法,其特征在于,所述晶圆为<100>晶向。

3.根据权利要求1所述的方法,其特征在于,在晶圆上沉积刻蚀阻挡层前所述晶圆还进行如下处理:所述晶圆的半导体衬底上形成栅极结构和侧墙;通过涂胶和显影分别完成nmos器件区域和pmos器件区域的源/漏离子注入。

4.根据权利要求3所述的方法,其特征在于,在注入源/漏离子的nmos器件区域和pmos器件区域沉积刻蚀阻挡层。

5.根据权利要求1或4所述的方法,其特征在于,所述刻蚀阻挡层的材质选用氮化硅、氮氧化硅或者氮化硅。

6.根据权利要求1所述的方法,其特征在于,所述等离子体氮化处理的条件是在200-650℃温度下,向刻蚀阻挡层表面通入含氮气体;通入含氮气体的流量是50-5000sccm;所述含氮气体的高频功率范围是10-2000w;所述含氮气体的压力范围是1-100torr。

7.根据权利要求1所述的方法,其特征在于,所述高拉应力层、低拉应力层的沉积工艺为化学气相沉积方法;

8.根据权利要求1或7所述的方法,其特征在于,所述高拉应力层的沉积厚度为拉应力范围为800-1400mpa;所述低拉应力层的沉积厚度为拉应力范围为1-700mpa。

9.根据权利要求1所述的方法,其特征在于,相邻高拉应力层的拉应力不同或相同。

10.根据权利要求1所述的方法,其特征在于,刻蚀阻挡层和高拉应力层至少同时覆盖在n阱和p阱上方。

技术总结

本发明提供一种基于多层应力记忆技术的CMOS器件制造方法,包括:在晶圆上沉积刻蚀阻挡层,并对刻蚀阻挡层进行等离子体氮化处理;在处理后的刻蚀阻挡层上进行n次沉积高拉应力层,并对高拉应力层进行等离子体氮化处理;在最上层等离子体氮化处理后的高拉应力层沉积低拉应力层;其中低拉应力层的拉应力和氢含量均小于所述高拉应力层的拉应力和氢含量;对沉积刻蚀阻挡层、高拉应力层、低拉应力层的晶圆进行快速热退火;对快速热退火后的晶圆刻蚀,去除所有应力层。通过使用本发明所提供的半导体器件和制造方法,可用超低的制造成本改善半导体器件的电学性能,在保证NMOS器件性能有进一步优化的同时,防止PMOS器件性能的退化。

技术研发人员:程勇鹏,郑隆跃,许凯,邓良耀,刘巾溆

受保护的技术使用者:浙江大学

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!