半导体器件的制作方法

本申请涉及显示,尤其是涉及一种半导体器件。

背景技术:

1、随着显示技术的发展,现有显示器件为了实现窄边框、高开口率、高亮度和高分辨率,需要将薄膜晶体管的尺寸和占用面积减小。但多晶硅薄膜晶体管的迁移率较小,为了提高薄膜晶体管的迁移率,需要减小沟道长度也就是增大有源层的占用面积,且沟道长度受到工艺限制导致缩小程度有限,导致显示器件无法兼顾薄膜晶体管的迁移率和尺寸。现有显示器件为了解决上述问题,会采用垂直结构的薄膜晶体管,通过将有源层的厚度作为薄膜晶体管的沟道长度,不会受到工艺限制,可以实现极小沟道长度的薄膜晶体管。但在垂直结构的薄膜晶体管的制备过程中,需要分别形成栅极、源极、漏极、欧姆接触层、沟道层和位于各层之间的绝缘层,导致薄膜晶体管的制备工艺较为复杂。且在三维堆叠的薄膜晶体管中,需要设置更多的薄膜晶体管,会导致工艺更为复杂。

2、所以,现有垂直结构的薄膜晶体管存在需要分别形成多个膜层导致工艺较为复杂的技术问题。

技术实现思路

1、本申请实施例提供一种半导体器件,用以改善现有垂直结构的薄膜晶体管存在需要分别形成多个膜层导致工艺较为复杂的技术问题。

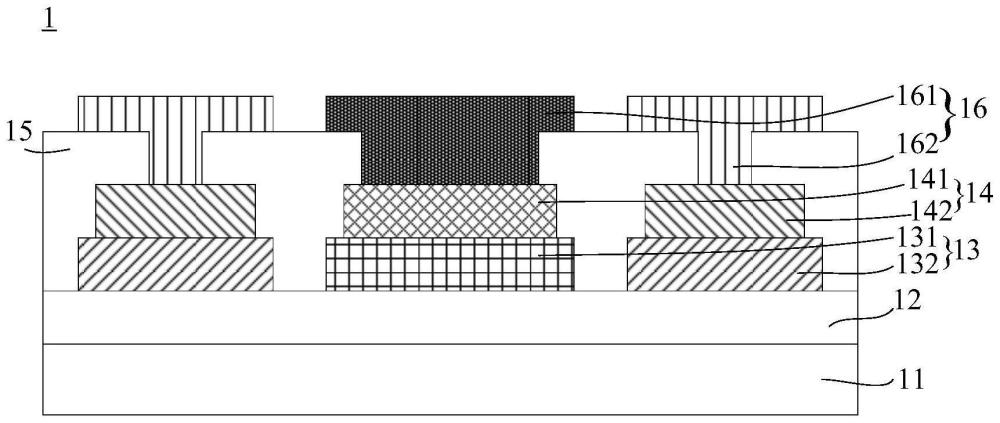

2、本申请实施例提供一种半导体器件,该半导体器件包括:

3、衬底;

4、第一金属层,设置于所述衬底一侧,所述第一金属层包括第一电极和第一栅极部;

5、有源层,设置于所述第一金属层远离所述衬底的一侧,所述有源层包括沟道部;

6、第二金属层,设置于所述有源层远离所述第一金属层的一侧,所述第二金属层包括第二电极和所述第二栅极部;

7、其中,所述沟道部的底面与所述第一电极接触,所述沟道部的顶面与所述第二电极接触,所述第一栅极部与所述第二栅极部电连接。

8、在一些实施例中,所述有源层还包括第三栅极部,所述第三栅极部的掺杂元素浓度大于所述沟道部的掺杂元素浓度,所述第三栅极部与所述第一栅极部接触且电连接,所述第三栅极部与所述第二栅极部接触且电连接。

9、在一些实施例中,所述第一栅极部设置于所述第一电极一侧,所述第三栅极部设置于所述沟道部一侧,所述第二栅极部设置于所述第二电极一侧,且所述第一栅极部、第三栅极部和所述第二栅极部位于所述沟道部的同一侧。

10、在一些实施例中,所述第三栅极部设置于所述沟道部的至少两侧。

11、在一些实施例中,所述第一栅极部位于所述第一电极的至少两侧,所述第二栅极部设置于所述第二电极的至少两侧,且位于所述沟道部同一侧的第一栅极部与所述第三栅极部接触且电连接,位于所述沟道部同一侧的第三栅极部与所述第二栅极部接触且电连接。

12、在一些实施例中,所述第一栅极部位于所述第一电极的相邻两侧,且位于所述第一电极相邻两侧的第一栅极部接触且电连接,所述第三栅极部位于所述沟道部的相邻两侧,且位于所述沟道部两侧的第三栅极部接触且电连接,所述第二栅极部位于所述第二电极的相邻两侧,且位于所述第二电极相邻两侧的所述第二栅极部接触且电连接。

13、在一些实施例中,所述第一栅极部位于所述第一电极的相对两侧,所述第三栅极部位于所述沟道部的相对两侧,所述第二栅极部位于所述第二电极的相对两侧。

14、在一些实施例中,所述第一栅极部在所述第一电极的三侧环绕所述第一电极设置,所述第三栅极部在所述沟道部的三侧环绕所述沟道部设置,所述第二栅极部在所述第二电极的三侧环绕所述第二电极设置。

15、在一些实施例中,所述第一电极沿远离所述第一栅极部的一侧超出所述沟道部设置,所述第二电极沿远离所述第二栅极部的一侧超出所述沟道部设置。

16、在一些实施例中,所述第三栅极部环绕所述沟道部设置。

17、在一些实施例中,所述第一栅极部设置于所述第一电极的至少一侧,所述第二栅极部设置于所述第二电极的至少一侧,且所述第一栅极部和所述第二栅极部位于所述沟道部同一侧,或者所述第一栅极部和所述第二栅极部位于所述沟道部的相对侧;或者所述第一栅极部和所述第二栅极部位于所述沟道部的相邻侧。

18、在一些实施例中,所述半导体器件还包括连接部,所述连接部包括第一子部、第二子部和第三子部,所述第一子部与所述第一电极连接,所述第一子部设置于所述第一金属层,所述第二子部设置于所述有源层,所述第三子部设置于所述第二金属层,所述第一子部与所述第二子部接触且电连接,所述第二子部与所述第三子部接触且电连接,所述第二子部的掺杂元素浓度大于所述沟道部的掺杂元素浓度。

19、在一些实施例中,所述第三栅极部的掺杂元素浓度范围为每立方厘米内设有10的14次方个掺杂元素至每立方厘米内设有10的19次方个掺杂元素。

20、在一些实施例中,所述半导体器件还包括:

21、第三金属层,设置于所述第二金属层远离所述有源层的一侧,所述第三金属层包括第三电极和第四栅极部;

22、半导体层,设置于所述第三金属层远离所述第二金属层的一侧,所述半导体层包括半导体部和第五栅极部;

23、第四金属层,设置于所述半导体层远离所述第三金属层的一侧,所述第四金属层包括第四电极和第六栅极部;

24、其中,所述半导体部底面与所述第三电极接触,所述半导体部的顶面与所述第四电极接触,所述第五栅极部的掺杂元素浓度大于所述半导体部的掺杂元素浓度,所述第四栅极部与所述第五栅极部接触且电连接,所述第五栅极部与所述第六栅极部接触且电连接;且所述半导体部在所述衬底上的投影与所述沟道部在所述衬底上的投影存在重合。

25、有益效果:本申请提供一种半导体器件;该半导体器件包括衬底、第一金属层、有源层和第二金属层,第一金属层设置于衬底一侧,第一金属层包括第一电极和第一栅极部,有源层设置于第一金属层远离衬底的一侧,有源层包括沟道部,第二金属层设置于有源层远离第一金属层的一侧,第二金属层包括第二电极和第二栅极部,其中,沟道部的底面与第一电极接触,沟道部的顶面与第二电极接触,所述第一栅极部与所述第二栅极部电连接。本申请通过使第一金属层和第二金属层分别形成栅极的第一栅极部和第二栅极部,且第一栅极部与第二栅极部电连接,第一栅极部和第二栅极部可以作为栅极控制薄膜晶体管,无需单独设置栅极层,减少了工艺步骤,提高了薄膜晶体管的制备效率,且并联设置的第一栅极部和第二栅极部可以提高栅极的导电性能,减小栅极的电阻,减小功耗。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.如权利要求1所述的半导体器件,其特征在于,所述有源层还包括第三栅极部,所述第三栅极部的掺杂元素浓度大于所述沟道部的掺杂元素浓度,所述第三栅极部与所述第一栅极部接触且电连接,所述第三栅极部与所述第二栅极部接触且电连接。

3.如权利要求2所述的半导体器件,其特征在于,所述第一栅极部设置于所述第一电极一侧,所述第三栅极部设置于所述沟道部一侧,所述第二栅极部设置于所述第二电极一侧,且所述第一栅极部、第三栅极部和所述第二栅极部位于所述沟道部的同一侧。

4.如权利要求2所述的半导体器件,其特征在于,所述第三栅极部设置于所述沟道部的至少两侧。

5.如权利要求4所述的半导体器件,其特征在于,所述第一栅极部位于所述第一电极的至少两侧,所述第二栅极部设置于所述第二电极的至少两侧,且位于所述沟道部同一侧的第一栅极部与所述第三栅极部接触且电连接,位于所述沟道部同一侧的第三栅极部与所述第二栅极部接触且电连接。

6.如权利要求5所述的半导体器件,其特征在于,所述第一栅极部位于所述第一电极的相邻两侧,且位于所述第一电极相邻两侧的第一栅极部接触且电连接,所述第三栅极部位于所述沟道部的相邻两侧,且位于所述沟道部两侧的第三栅极部接触且电连接,所述第二栅极部位于所述第二电极的相邻两侧,且位于所述第二电极相邻两侧的所述第二栅极部接触且电连接。

7.如权利要求5所述的半导体器件,其特征在于,所述第一栅极部位于所述第一电极的相对两侧,所述第三栅极部位于所述沟道部的相对两侧,所述第二栅极部位于所述第二电极的相对两侧。

8.如权利要求5所述的半导体器件,其特征在于,所述第一栅极部在所述第一电极的三侧环绕所述第一电极设置,所述第三栅极部在所述沟道部的三侧环绕所述沟道部设置,所述第二栅极部在所述第二电极的三侧环绕所述第二电极设置。

9.如权利要求8所述的半导体器件,其特征在于,所述第一电极沿远离所述第一栅极部的一侧超出所述沟道部设置,所述第二电极沿远离所述第二栅极部的一侧超出所述沟道部设置。

10.如权利要求2所述的半导体器件,其特征在于,所述第三栅极部环绕所述沟道部设置。

11.如权利要求10所述的半导体器件,其特征在于,所述第一栅极部设置于所述第一电极的至少一侧,所述第二栅极部设置于所述第二电极的至少一侧,且所述第一栅极部和所述第二栅极部位于所述沟道部同一侧,或者所述第一栅极部和所述第二栅极部位于所述沟道部的相对侧;或者所述第一栅极部和所述第二栅极部位于所述沟道部的相邻侧。

12.如权利要求2所述的半导体器件,其特征在于,所述半导体器件还包括连接部,所述连接部包括第一子部、第二子部和第三子部,所述第一子部与所述第一电极连接,所述第一子部设置于所述第一金属层,所述第二子部设置于所述有源层,所述第三子部设置于所述第二金属层,所述第一子部与所述第二子部接触且电连接,所述第二子部与所述第三子部接触且电连接,所述第二子部的掺杂元素浓度大于所述沟道部的掺杂元素浓度。

13.如权利要求2所述的半导体器件,其特征在于,所述第三栅极部的掺杂元素浓度范围为每立方厘米内设有10的14次方个掺杂元素至每立方厘米内设有10的19次方个掺杂元素。

14.如权利要求1所述的半导体器件,其特征在于,所述半导体器件还包括:

技术总结

本申请提供一种半导体器件和电子器件;该半导体器件通过使第一金属层和第二金属层分别形成栅极的第一栅极部和第二栅极部,且第一栅极部与第二栅极部电连接,第一栅极部和第二栅极部可以作为栅极控制薄膜晶体管,无需单独设置栅极层,减少了工艺步骤,提高了薄膜晶体管的制备效率,且并联设置的第一栅极部和第二栅极部可以提高栅极的导电性能,减小栅极的电阻,减小功耗。

技术研发人员:周志超,谭志威,刘忠杰

受保护的技术使用者:惠州华星光电显示有限公司

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!