高空穴迁移率沟道的围栅堆叠纳米片器件及其制备方法

本发明涉及半导体器件领域,特别涉及一种高空穴迁移率沟道的围栅堆叠纳米片器件及其制备方法。

背景技术:

1、集成电路特征尺寸持续微缩,传统三栅或双栅的finfet在3nm以下节点受到限制,与主流后高k金属栅finfet工艺兼容的纳米环栅晶体管(gaa-fet)将是实现尺寸微缩的下一代关键结构,其沟道主要为堆叠纳米片(stacked nanosheet)结构。

2、在gaa-fet器件的传统制备过程中往往要外延sige与si的交替堆叠层,其中,si为最终的纳米片沟道(ns沟道),sige作为牺牲层可以引入沟道应力,由于sige的晶格常数比si大,所以sige对si ns沟道在(100)面沿着沟道与垂直沟道方向会施加拉应力,这样的应力条件会提高沟道中电子迁移率,但是围栅堆叠si ns cmos器件面临的挑战之一就是ns表面(100)晶向的空穴迁移率低,造成p型器件性能退化。

3、为此,提出本发明。

技术实现思路

1、本发明的主要目的在于提供一种高空穴迁移率沟道的围栅堆叠纳米片器件及其制备方法,提高了空穴迁移率,可以克服p管性能退化的问题。

2、为了实现以上目的,本发明提供了以下技术方案。

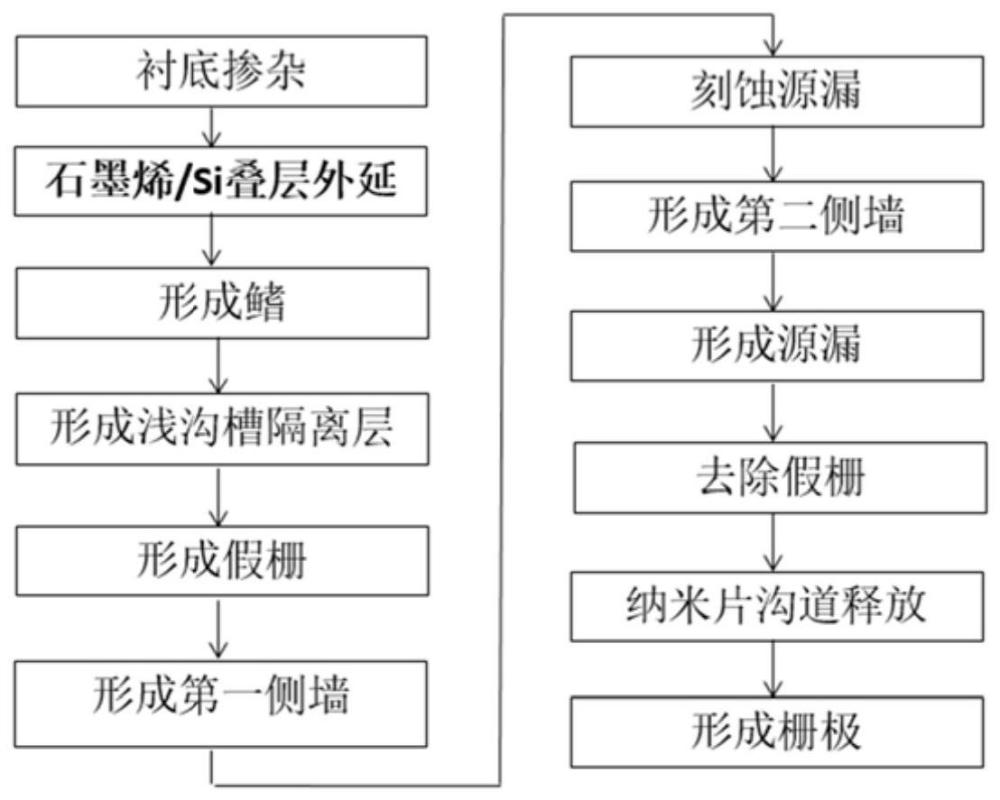

3、本发明的第一方面提供了一种高空穴迁移率沟道的围栅堆叠纳米片器件的制备方法,其包括:

4、提供衬底;

5、在所述衬底表面形成硅层和石墨烯层交替层叠的超晶格叠层;

6、刻蚀所述超晶格叠层以及所述衬底的部分厚度,形成鳍;

7、在所述衬底上形成第一介质层,作为鳍之间的浅沟槽隔离层;

8、在所述鳍上形成假栅,在所述假栅的侧壁上形成第一侧墙;

9、刻蚀鳍中的超晶格叠层,释放出待形成源漏的凹槽;

10、在鳍中的超晶格叠层的侧壁形成第二侧墙;

11、在所述凹槽外延半导体材料,形成源漏;

12、去除假栅;

13、刻蚀掉所述超晶格叠层中的石墨烯层,实现纳米片沟道释放,所述纳米片形成的叠层构成多个导电沟道;

14、形成环绕式栅极,其环绕所述纳米片形成的叠层。

15、本发明采用石墨烯代替了传统的锗硅牺牲层,由于石墨烯晶格常数(0.246nm)小于si(0.543nm),因此会对si在(100)面上沿着沟道与垂直沟道方向产生压应力,从而提高空穴迁移率,当其适用于p管器件时,可以克服p管性能退化的问题。

16、进一步地,所述石墨烯层通过碳分子束外延生长法形成。

17、通过调整碳分子束外延生长法(cmbe)的工艺条件可以控制石墨烯层的厚度,得到具有一定厚度的单层石墨烯层。

18、进一步地,所述刻蚀鳍中的超晶格叠层,释放出待形成源漏的凹槽时,采用等离子体刻蚀法。等离子体刻蚀法对si与石墨烯都有很好的各向同性刻蚀效果,并且对sio2及sinx都有极高的选择比,因此用该手段释放源漏凹槽时容易得到形状规则的凹槽。

19、进一步地,所述等离子体刻蚀法采用o2等离子体、ar等离子体中的至少一种。

20、进一步地,所述第一侧墙和所述第二侧墙为氮化硅。

21、进一步地,所述刻蚀掉所述超晶格叠层中的石墨烯层的方法包括:采用n-甲基吡咯烷酮去除石墨烯层。

22、n-甲基吡咯烷酮(nmp)作为半导体工艺中的常见有机溶剂,对si、sinx、sio2等都具有极高的选择比。

23、进一步地,所述围栅堆叠纳米片器件为p型器件。采用传统工艺制备p型器件时空穴迁移率低的问题较为突出,因此,本发明的方法更适宜制备p型器件。

24、进一步地,所述超晶格叠层中石墨烯层靠近所述衬底。

25、进一步地,所述超晶格叠层包括三层石墨烯层。

26、本发明的第二方面提供了一种高空穴迁移率沟道的围栅堆叠纳米片器件,其采用第一方面的制备方法制备得到。

27、综上,与现有技术相比,本发明达到了以下技术效果:

28、(1)石墨烯(c60)晶格常数(0.246nm)小于si(0.543nm),会对si在(100)面上沿着沟道与垂直沟道方向产生压应力,从而提高p管的空穴迁移率,克服p管性能退化的问题;

29、(2)o2、ar等离子体刻蚀法对si与石墨烯都有很好的各向同性刻蚀效果,并且对sio2及sinx都有极高的选择比。

30、(3)nmp,对si、sinx、sio2等都具有极高的选择比,因此更适合刻蚀石墨烯层,释放纳米沟道。

技术特征:

1.一种高空穴迁移率沟道的围栅堆叠纳米片器件的制备方法,其特征在于,包括:

2.根据权利要求1所述的制备方法,其特征在于,所述石墨烯层通过碳分子束外延生长法形成。

3.根据权利要求1或2所述的制备方法,其特征在于,所述刻蚀鳍中的超晶格叠层,释放出待形成源漏的凹槽时,采用等离子体刻蚀法。

4.根据权利要求3所述的制备方法,其特征在于,所述等离子体刻蚀法采用o2等离子体、ar等离子体中的至少一种。

5.根据权利要求1所述的制备方法,其特征在于,所述第一侧墙和所述第二侧墙为氮化硅。

6.根据权利要求1所述的制备方法,其特征在于,所述刻蚀掉所述超晶格叠层中的石墨烯层的方法包括:采用n-甲基吡咯烷酮去除石墨烯层。

7.根据权利要求1或2或5-6任一项所述的制备方法,其特征在于,所述围栅堆叠纳米片器件为p型器件。

8.根据权利要求1所述的制备方法,其特征在于,所述超晶格叠层中石墨烯层靠近所述衬底。

9.根据权利要求1或8所述的制备方法,其特征在于,所述超晶格叠层包括三层石墨烯层。

10.一种高空穴迁移率沟道的围栅堆叠纳米片器件,其特征在于,其采用权利要求1-9任一项所述的制备方法制备得到。

技术总结

本发明涉及一种高空穴迁移率沟道的围栅堆叠纳米片器件及其制备方法。制备方法,其包括:提供衬底;在衬底表面形成硅层和石墨烯层交替层叠的超晶格叠层;刻蚀超晶格叠层以及衬底的部分厚度,形成鳍;在衬底上形成第一介质层,作为鳍之间的浅沟槽隔离层;在鳍上形成假栅,在假栅的侧壁上形成第一侧墙;刻蚀鳍中的超晶格叠层,释放出待形成源漏的凹槽;在鳍中的超晶格叠层的侧壁形成第二侧墙;在凹槽外延半导体材料,形成源漏;去除假栅;刻蚀掉超晶格叠层中的石墨烯层,实现纳米片沟道释放,纳米片形成的叠层构成多个导电沟道;形成环绕式栅极,其环绕纳米片形成的叠层。本发明提高了P管的空穴迁移率,克服P管性能退化的问题。

技术研发人员:殷华湘,蒋任婕,桑冠荞,李庆坤,魏延钊,王鹏,张青竹,李俊峰

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!