半导体装置的制作方法

本发明涉及半导体,尤其是涉及一种半导体装置。

背景技术:

1、在半导体器件中,为降低功率模块的功率损耗,需要绝缘栅双极晶体管具有较低的通断损耗以及导通电压。另外,为保证半导体器件在实际应用中的稳定性,需要绝缘栅双极晶体管具有较好的鲁棒性以及稳定的开关特性。目前的功率绝缘栅双极晶体管中,尽管在绝缘栅双极晶体管的稳定性上取得进步,但是在其开关特性上仍存在不足。

2、现有技术中,绝缘栅双极晶体管的开通或者关断时,均会存在损耗的问题,这是绝缘栅双极晶体管功率损耗的主要原因。在绝缘栅双极晶体管中增加载流子存储层的浓度有利于增加绝缘栅双极晶体管的开关速度,进而有利于降低绝缘栅双极晶体管的开通损耗,但是载流子载流子存储层的浓度升高,绝缘栅双极晶体管容易出现开关速度不受控制的问题。另外,功率绝缘栅双极晶体管普遍存在耐压稳定性不足的情况。

技术实现思路

1、本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明的一个目的在于提出一种半导体装置,该半导体装置可以优化开关性能,提升鲁棒性。

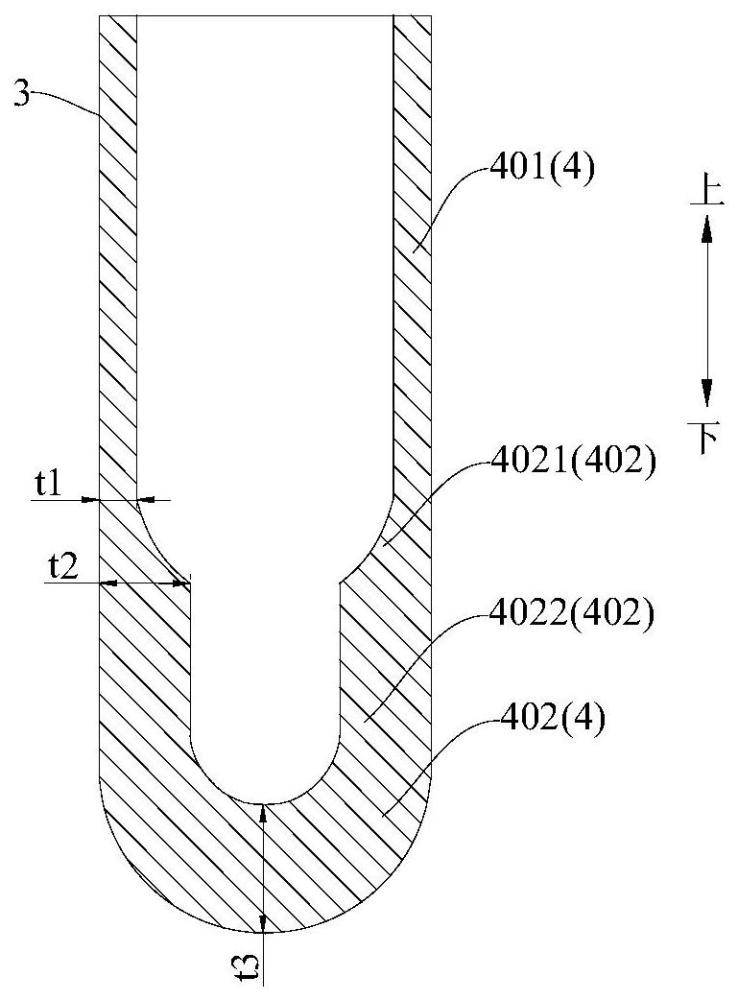

2、根据本发明实施例的半导体装置,包括:第一导电类型的漂移层;基极层,所述基极层设置于所述漂移层的上表面;沟槽部,所述沟槽部从所述基极层的上表面向下贯穿所述基极层且到达所述漂移层内;载流子存储层,所述载流子存储层设置于所述漂移层上表面且位于所述漂移层和所述基极层之间,所述沟槽部从所述基极层的上表面向下贯穿所述基极层和所述载流子存储层且到达所述漂移层内;氧化层,所述氧化层设置于所述沟槽部的内壁且包括第一氧化部和第二氧化部,所述第二氧化部设置于所述第一氧化部的下方,所述第一氧化部径向上的厚度为t1,所述第二氧化部径向上的厚度为t2,t1和t2满足关系式:t1<t2。

3、由此,在同等栅极和发射极之间电压的作用下,载流子存储层的浓度越高,产生的沟道越宽,导致开通速度过快,不受控制。通过设置第二氧化部的径向厚度大于第一氧化部的径向厚度,不仅可以使靠近第二氧化部的载流子存储层受到的栅极场效应减弱,可以改善该区域载流子存储层的掺杂量上升带来的开通速度过快而造成电流变化率不受控的问题,而且还可以提高沟槽部对应第二氧化部的耐压能力,从而不仅可以改善半导体装置的开关性能,而且还可以提高半导体装置的鲁棒性。

4、在本发明的一些示例中,所述第二氧化部包括第一部分和第二部分,所述第一部分连接在所述第一氧化部和第二部分之间,所述第一氧化部径向上的厚度在上下方向上相等,所述第二部分径向上的厚度在上下方向上相等,所述第一部分上端径向上的厚度为t1,所述第一部分下端径向上的厚度为t2。

5、在本发明的一些示例中,所述第一部分远离所述沟槽部内侧壁的一侧到所述沟槽部内侧壁之间的距离在从上向下的方向上逐渐增大。

6、在本发明的一些示例中,所述第二氧化部呈弧形,所述第二氧化部底部上下方向的厚度为t3,t3和t2满足关系式:t2≤t3。

7、在本发明的一些示例中,所述基极层上下方向上的深度为d1,所述第一氧化部和所述第一部分上下方向上的深度之和为d2,d1和d2满足关系式:d1<d2。

8、在本发明的一些示例中,所述基极层和所述载流子存储层上下方向上的深度之和为d3,所述氧化层上下方向上的深度为d4,d3和d4满足关系式:d3<d4。

9、在本发明的一些示例中,所述第一氧化部和所述第二氧化部为连续结构,所述第一氧化部和所述第二氧化部径向上的厚度均在从上向下的方向上逐渐增大。

10、在本发明的一些示例中,所述第二氧化部呈弧形,所述第二氧化部下端径向上的厚度为t4,所述第二氧化部底部上下方向的厚度为t5,t4和t5满足关系式:t4≤t5。

11、在本发明的一些示例中,所述氧化层的侧壁相对上下方向延伸的竖直平面倾斜设置,所述氧化层的侧壁与所述竖直平面之间形成有夹角α,α满足关系式:0°<α<90°。

12、在本发明的一些示例中,所述基极层上下方向上的深度为d5、所述氧化层上下方向上的深度为d6,d5和d6满足关系式:d5<d6,所述载流子存储层上下方向上的深度为d7,d5、d6和d7满足关系式:d7+d5<d6。

13、本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

技术特征:

1.一种半导体装置,其特征在于,包括:

2.根据权利要求1所述的半导体装置,其特征在于,所述第二氧化部(402)包括第一部分(4021)和第二部分(4022),所述第一部分(4021)连接在所述第一氧化部(401)和第二部分(4022)之间,所述第一氧化部(401)径向上的厚度在上下方向上相等,所述第二部分(4022)径向上的厚度在上下方向上相等,所述第一部分(4021)上端径向上的厚度为t1,所述第一部分(4021)下端径向上的厚度为t2。

3.根据权利要求2所述的半导体装置,其特征在于,所述第一部分(4021)远离所述沟槽部(3)内侧壁的一侧到所述沟槽部(3)内侧壁之间的距离在从上向下的方向上逐渐增大。

4.根据权利要求3所述的半导体装置,其特征在于,所述第二氧化部(402)呈弧形,所述第二氧化部(402)底部上下方向的厚度为t3,t3和t2满足关系式:t2≤t3。

5.根据权利要求2所述的半导体装置,其特征在于,所述基极层(2)上下方向上的深度为d1,所述第一氧化部(401)和所述第一部分(4021)上下方向上的深度之和为d2,d1和d2满足关系式:d1<d2。

6.根据权利要求4所述的半导体装置,其特征在于,所述基极层(2)和所述载流子存储层(5)上下方向上的深度之和为d3,所述氧化层(4)上下方向上的深度为d4,d3和d4满足关系式:d3<d4。

7.根据权利要求1所述的半导体装置,其特征在于,所述第一氧化部(401)和所述第二氧化部(402)为连续结构,所述第一氧化部(401)和所述第二氧化部(402)径向上的厚度均在从上向下的方向上逐渐增大。

8.根据权利要求6所述的半导体装置,其特征在于,所述第二氧化部(402)呈弧形,所述第二氧化部(402)下端径向上的厚度为t4,所述第二氧化部(402)底部上下方向的厚度为t5,t4和t5满足关系式:t4≤t5。

9.根据权利要求6所述的半导体装置,其特征在于,所述氧化层(4)的侧壁相对上下方向延伸的竖直平面倾斜设置,所述氧化层(4)的侧壁与所述竖直平面之间形成有夹角α,α满足关系式:0°<α<90°。

10.根据权利要求6所述的半导体装置,其特征在于,所述基极层(2)上下方向上的深度为d5、所述氧化层(4)上下方向上的深度为d6,d5和d6满足关系式:d5<d6,所述载流子存储层(5)上下方向上的深度为d7,d5、d6和d7满足关系式:d7+d5<d6。

技术总结

本发明公开了一种半导体装置,半导体装置包括:沟槽部;载流子存储层;氧化层,氧化层设置于沟槽部的内壁且包括第一氧化部和第二氧化部,第二氧化部设置于第一氧化部的下方,第一氧化部径向上的厚度为t1,第二氧化部径向上的厚度为t2,t1和t2满足关系式:t1<t2。由此,通过设置第二氧化部的径向厚度大于第一氧化部的径向厚度,不仅可以使靠近第二氧化部的载流子存储层受到的栅极场效应减弱,可以改善该区域载流子存储层的掺杂量上升带来的开通速度过快而造成电流变化率不受控的问题,而且还可以提高沟槽部对应第二氧化部的耐压能力,从而不仅可以改善半导体装置的开关性能,而且还可以提高半导体装置的鲁棒性。

技术研发人员:刘子俭,陈道坤,储金星,张永旺,刘恒,杨晶杰,何濠启,史世平,邹苹,周文杰

受保护的技术使用者:海信家电集团股份有限公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!